# Predictable and Composable System-on-Chip Memory Controllers

### PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 24 februari 2010 om 16.00 uur

door

Benny Åkesson

geboren te Saxtorp, Zweden

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr. K.G.W. Goossens en prof.dr. H. Corporaal

ISBN: 978-90-386-2169-2 NUR: 959

ii

A catalogue record is available from the Eindhoven University of Technology Library

# Predictable and Composable System-on-Chip Memory Controllers

Benny Åkesson

Members of the dissertation committee:

| Prof.dr. K.G.W. Goossens    | Eindhoven University of Technology   | (first promotor)  |

|-----------------------------|--------------------------------------|-------------------|

| Prof.dr. H. Corporaal       | Eindhoven University of Technology   | (second promotor) |

| Prof.dr.ir. C.H. van Berkel | Eindhoven University of Technology   |                   |

|                             | ST Ericsson                          |                   |

| Prof.dr.ir. M.J.G. Bekooij  | University of Twente                 |                   |

|                             | NXP Semiconductors                   |                   |

| Prof.DrIng R. Ernst         | Technical University of Braunschweig |                   |

| Prof.dr.ir. H.J. Sips       | Delft University of Technology       |                   |

| Dr.ir. P. van der Wolf      | Virage Logic                         |                   |

| Prof.dr.ir. A.C.P.M. Backx  | Eindhoven University of Technology   | (chairman)        |

|                             |                                      |                   |

This work was carried out at Philips Electronics & NXP Semiconductors.

Copyright 2010 Benny Åkesson

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means electronic, mechanical, photocopying, or otherwise, without the prior written permission from the copyright owner.

Cover design by Juan Manuel Martelli.

Printing by Printservice, Eindhoven University of Technology.

iv

This thesis is dedicated to the memory of Marianne Åkesson, my loving mother who left us much too soon. v

vi

### Acknowledgements

This journey would not have been possible without the contributions from many people. I want to thank Prof. Lambert Spaanenburg for organizing the field-trip that first brought me to the Netherlands and resulted in my master project at Philips Research in Eindhoven. I am also grateful to Prof. Jef van Meerbergen for the opportunity to become a Ph.D. student at the Eindhoven University of Technology.

Moving abroad was a life-changing experience. Thanks to the friends in Sweden that kept in touch after I left, most prominently Malin Davidsson. I also want to thank the International Student Network in Eindhoven, through which I quickly made many new friends from all over the world. Special thanks to Ramesh Chidambaram and Anastasia Andreadaki, who were both here from the very beginning, and who are still here, no matter how hard they try not to. During my stay in Eindhoven, I developed a passion for capoeira. Obrigado Formado Tayson and all capoeiristas in Eindhoven for the classes and the good times in the roda.

In the Electronic Systems group at Eindhoven University of Technology, I want to thank my second promotor Prof. Henk Corporaal for the fruitful feedback that improved this thesis. Big thanks also to Sander Stuijk for all the technical support over the years. I furthermore want to recognize our dear secretaries, Rian van Gaalen and Marja de Mol-Regels, who always helped with practical matters.

I always enjoyed working at Philips and NXP. I want to thank Prof. Kees Goossens for being my first promotor, and a role model as mentor, scientist, and Jedi master. I am proud to have been a part of his Æthereal team. Never before did so many people work so hard on a project that was so cancelled. I am also happy to have worked with Prof. Marco Bekooij and his people in the Hijdra project. I further want to mention Roelof Salters for sharing his deep knowledge about SDRAM memories, Ad Siereveld for his insights on memory controller architectures, and Liesbeth Steffens for teaching me about real-time arbitration. Coming to work was always a pleasure with great office mates and fellow Ph.D. students. Thank you Aleksandar Milutinovic, Tjerk Bijlsma,

Maarten Wiggers, Arno Moonen and Philippe Dumont, just to name a few. Working together is more fun than working alone. In this spirit, I thank my students Markus Ringhofer, Eelke Strooisma, Getachew Teshome, Williston Hayes, and Winston Siauw for their contributions to my research and for the fun we had together.

I extend my deepest gratitude to Andreas Hansson, a great friend and house mate. I really value our cooperation during the past decade. Now, our quest to take over the world continues, but on different hemispheres. Divide and conquer!

I would not be here without my family who always supported me throughout my life, and encouraged me to follow my dreams and leave my country when the opportunity presented itself. In particular, I want to thank my parents, Marianne and Lars-Göran Åkesson, for always acting in the best interest of their children. I owe it all to you! Finally, I want to thank María Eugenia Martelli for being the greatest girlfriend through the long working hours and mood swings it means to finish a Ph.D. I love you!

viii

### Abstract

#### Predictable and Composable System-on-Chip Memory Controllers

Contemporary System-on-Chip (SoC) become more and more complex, as increasing integration results in a larger number of concurrently executing applications. These applications consist of tasks that are mapped on heterogeneous multi-processor platforms with distributed memory hierarchies, where SRAMs and SDRAMs are shared by a variety of arbiters. Some applications have *real-time requirements*, meaning that they must perform a particular computation before a deadline to guarantee functional correctness, or to prevent quality degradation. Mapping the applications on the platform such that all real-time requirements are satisfied is very challenging. The number of possible mappings of tasks to processing elements and data structures to memories may be large, and appropriate configuration settings must be determined once the mapping is chosen. Verifying that a particular mapping satisfies all application requirements is typically done by system-level simulation. However, resource sharing causes interference between applications, making their temporal behaviors inter-dependent. All concurrently executing applications must hence be verified together, causing the verification complexity of the system to increase exponentially with the number of applications. Together these factors contribute to making the integration and verification process a dominant part of SoC development, both in terms of time and money.

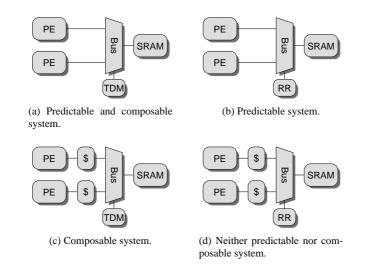

*Predictable* and *composable* systems are proposed to manage the increasing verification complexity. Predictable systems provide lower bounds on application performance, while applications in composable systems are completely isolated and cannot affect each other's temporal behavior by even a single clock cycle. Predictable systems enable formal verification that covers all possible interactions with the platform. However, this assumes that the behavior of an application is captured in a performance model, which is not the case for many applications. Composability offers a complementary verification approach by letting these applications be verified independently by simulation with linear verification complexity. A limitation of current predictable and composable systems is that there are no memory controllers supporting the concepts in a general way. Current SRAM controllers can be shared in a predictable way with a variety of arbiters, but are only composable if statically scheduled or shared using time-division multiplexing. Existing SDRAM controllers are not composable, and are either unpredictable or limited to applications that are statically scheduled.

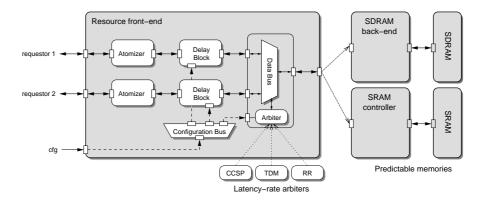

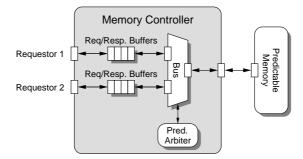

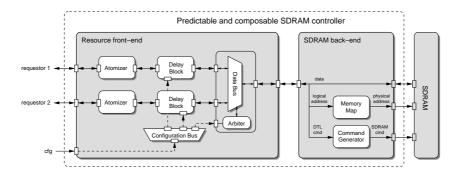

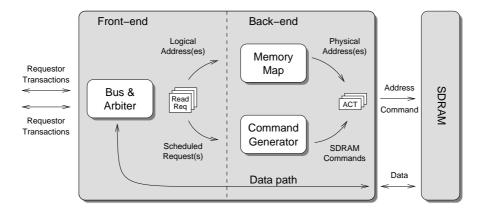

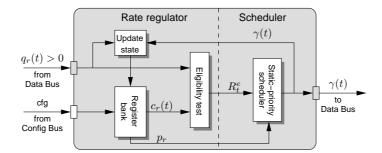

This thesis addresses the limitations of current predictable and composable systems by proposing a general predictable and composable memory controller, thereby addressing the mapping and verification problem in embedded systems. The proposed memory controller is divided into a *front-end* and a *back-end*. The back-end is specific for DDR2/DDR3 SDRAM and makes the memory behave in a predictable manner using precomputed memory patterns that are dynamically combined at run time. The front-end contains buffering and an arbiter in the class of Latency-Rate ( $\mathcal{LR}$ ) servers, which is a class with many well-known predictable arbiters. We extend this class with a Credit-Controlled Static-Priority (CCSP) arbiter that is developed specifically for shared resources with latency-critical requestors and high loads, such as memories. Three key features of CCSP are: 1) It accommodates latency-critical requestors with low bandwidth requirements without wasting bandwidth. 2) Over-allocated bandwidth due to discretization can be made negligible at an increased area cost, without affecting latency. 3) It has a small implementation that runs fast enough to keep up with most DDR2/DDR3 memories. The proposed front-end is general and can be used with other predictable resources, such as SRAM controllers. The proposed memory controller hence supports multiple arbiter and memory types, thus addressing the diversity in modern SoCs. The combination of front-end and predictable memory behaves like a  $\mathcal{LR}$  server, which is the *shared* resource abstraction used in this work. In essence, a  $\mathcal{LR}$  server guarantees a requestor a minimum bandwidth and a maximum latency, enabling formal verification of real-time requirements. The  $\mathcal{LR}$  server model is compatible with several commonly used formal analysis frameworks, such as network calculus and data-flow analysis. Our memory controller hence allows *any combination* of predictable memory and  $\mathcal{LR}$  arbiter to be used transparently for formal verification of applications with any of these frameworks.

Sharing a predictable memory at run-time results in interference between requestors, making the memory controller non-composable. This is addressed by adding a Delay Block to the front-end that delays all signals sent from the front-end to a requestor to always emulate worst-case interference. This makes requestors unable to affect each other's temporal behavior, which is sufficient to guarantee composability on the level of applications. Our predictable memory controller hence offers composable service with a variety of memory and arbiter types, which widely extends the scope of composable platforms. Another benefit of this approach is that it enables composable service to be dynamically enabled and disabled, enabling requestors that do not require composable service to use slack bandwidth to improve performance.

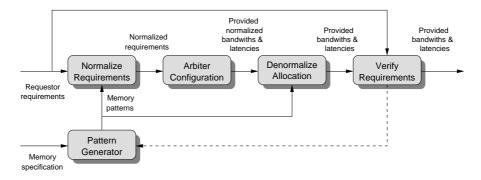

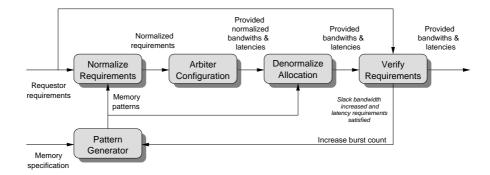

The predictable and composable memory controller is supported by a configuration flow that *automatically computes memory patterns and arbiter settings* to satisfy given bandwidth and latency requirements. The flow uses abstraction to separate the configuration of the memory and the arbiter, enabling settings to be computed in a streamlined fashion for all supported memories and arbiters.

### Contents

| 1 | Intr | oduction                                 | 1  |

|---|------|------------------------------------------|----|

|   | 1.1  | Trends in embedded system design         | 2  |

|   | 1.2  | Problem statement                        | 14 |

|   | 1.3  | Requirements                             | 15 |

|   | 1.4  | Contributions                            | 20 |

|   | 1.5  | Outline                                  | 21 |

|   | 1.6  | Summary                                  | 22 |

| 2 | Proj | posed solution                           | 25 |

|   | 2.1  | Predictability                           | 25 |

|   | 2.2  | Abstraction                              | 33 |

|   | 2.3  | Composability                            | 35 |

|   | 2.4  | Automation                               | 37 |

|   | 2.5  | Summary                                  | 39 |

| 3 | SDF  | RAM memories and controllers             | 41 |

|   | 3.1  | Introduction to SDRAM                    | 41 |

|   | 3.2  | Formal model                             | 44 |

|   | 3.3  | Memory efficiency                        | 47 |

|   | 3.4  | Memory controllers                       | 50 |

|   | 3.5  | Summary                                  | 56 |

| 4 | Prec | lictable SDRAM back-end                  | 59 |

|   | 4.1  | Overview of predictable SDRAM controller | 59 |

|   | 4.2  | Memory patterns                          | 61 |

|   | 4.3  | Memory efficiency bound                  | 66 |

### CONTENTS

|    | 4.4   | Latency bound                              | 69  |

|----|-------|--------------------------------------------|-----|

|    | 4.5   | Memory pattern generation                  | 72  |

|    | 4.6   | Architecture and synthesis                 | 84  |

|    | 4.7   | Experimental results                       | 85  |

|    | 4.8   | Summary                                    | 94  |

| 5  | Cre   | lit-Controlled Static-Priority arbitration | 97  |

|    | 5.1   | Arbiter requirements                       | 98  |

|    | 5.2   | Formal model                               | 98  |

|    | 5.3   | Definition of CCSP arbitration             | 101 |

|    | 5.4   | Arbiter analysis                           | 107 |

|    | 5.5   | $\mathcal{LR}$ server                      | 113 |

|    | 5.6   | Hardware implementation                    | 120 |

|    | 5.7   | Architecture and synthesis                 | 125 |

|    | 5.8   | Experimental results                       | 127 |

|    | 5.9   | Summary                                    | 138 |

| 6  | Con   | posable resource front-end                 | 141 |

|    | 6.1   | Overview of approach                       | 142 |

|    | 6.2   | Formal model                               | 144 |

|    | 6.3   | Timing analysis                            | 144 |

|    | 6.4   | Architecture and synthesis                 | 148 |

|    | 6.5   | Experiments                                | 157 |

|    | 6.6   | Summary                                    | 168 |

| 7  | Con   | figuration                                 | 169 |

|    | 7.1   | Formal model                               | 170 |

|    | 7.2   | Memory pattern generation                  | 171 |

|    | 7.3   | Normalization of requirements              | 173 |

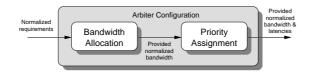

|    | 7.4   | Arbiter configuration                      | 175 |

|    | 7.5   | Denormalization of allocation              | 179 |

|    | 7.6   | Requirement verification                   | 180 |

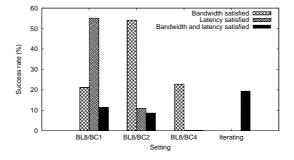

|    | 7.7   | Experimental results                       | 182 |

|    | 7.8   | Summary                                    | 183 |

| 8  | Rela  | ited work                                  | 185 |

|    | 8.1   | Resource arbitration                       | 185 |

|    | 8.2   | SDRAM controllers                          | 188 |

|    | 8.3   | Composable service                         | 190 |

| 9  | Con   | clusions and future work                   | 193 |

| -  | 9.1   | Conclusions                                | 194 |

|    | 9.2   | Future work                                | 196 |

| Ri | hliom | raphy                                      | 199 |

| ы  | onogi | ahul                                       | 1)) |

xii

### CONTENTS

| C | About the author                                                                   | 41) |

|---|------------------------------------------------------------------------------------|-----|

| С |                                                                                    | 219 |

| B | System XML specificationB.1Architecture specificationB.2Use-case specification     |     |

| A | Glossary         A.1       List of abbreviations         A.2       List of symbols |     |

#### xiii

CONTENTS

xiv

# List of Figures

| 1.1  | Example design flow comprised of a partitioning, platform exploration, mapping, and a verification stage.                                              | 2  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | A JPEG decoder application consisting of three tasks.                                                                                                  | 4  |

| 1.2  | Starting and stopping applications causes use-case transitions.                                                                                        | 5  |

| 1.4  | The design productivity gap.                                                                                                                           | 5  |

| 1.5  | The platform template considered in this thesis.                                                                                                       | 7  |

| 1.6  | Processing element and resource communicating via a standard protocol.                                                                                 | 9  |

| 1.7  | Multiple processing elements sharing a resource.                                                                                                       | 9  |

| 1.8  | Tasks are mapped to processing elements, data structures to memories, and communication channels to the interconnect as a part of the mapping process. | 11 |

| 1.9  | The SDRAM architecture consists of banks, rows, and columns.                                                                                           | 13 |

|      | Four systems demonstrating all combinations of the predictability and                                                                                  |    |

|      | composability properties.                                                                                                                              | 19 |

| 1.11 | The proposed predictable and composable memory controller                                                                                              | 20 |

| 2.1  | Overview of predictable memory controller.                                                                                                             | 26 |

| 2.2  | The behaviors of some important SDRAM commands.                                                                                                        | 27 |

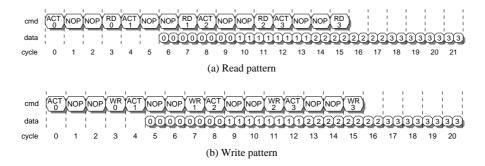

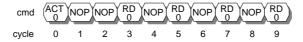

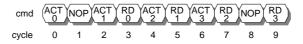

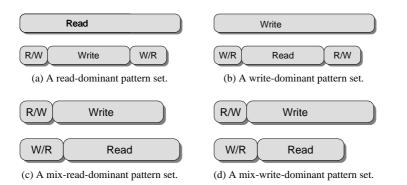

| 2.3  | Read pattern and write patterns with burst length 8 for a DDR2-400                                                                                     | 29 |

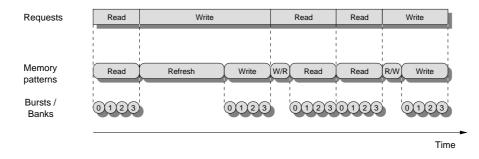

| 2.4  | Mapping from requests to patterns to SDRAM bursts                                                                                                      | 29 |

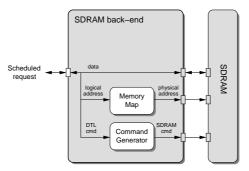

| 2.5  | Overview of the predictable SDRAM back-end                                                                                                             | 30 |

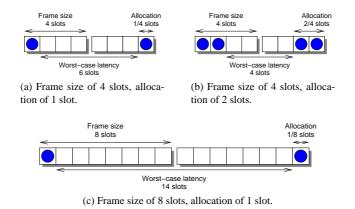

| 2.6  | Example of coupling between allocation granularity, latency, and allo-<br>cated bandwidth.                                                             | 31 |

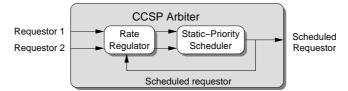

| 2.7  | Overview of a CCSP arbiter with two requestors.                                                                                                        | 32 |

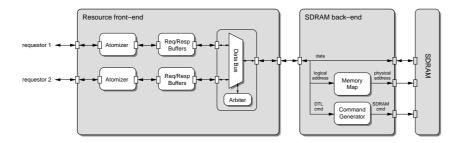

| 2.8  | A predictable SDRAM controller supporting two requestors.                                                                                              | 33 |

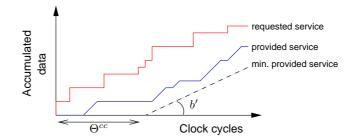

| 2.9  | The $\mathcal{LR}$ server abstraction.                                                                                                                 | 34 |

### LIST OF FIGURES

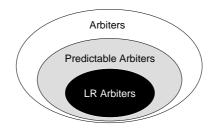

|            | $\mathcal{LR}$ arbiters are a subset of predictable arbiters                                                                                      | 34       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|

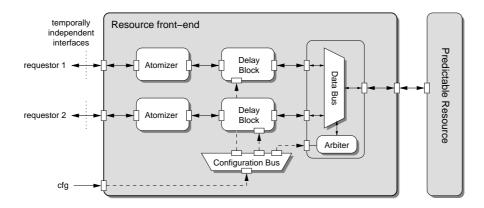

|            | porting two requestors.                                                                                                                           | 37       |

| 2.12       | Simplified overview of the automated configuration flow.                                                                                          | 38       |

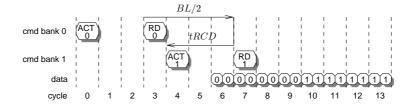

| 3.1        | The SDRAM architecture.                                                                                                                           | 43       |

| 3.2<br>3.3 | Example of SDRAM timing constraints                                                                                                               | 44       |

|            | misaligned                                                                                                                                        | 49       |

| 3.4        | The most important building blocks of a general SDRAM controller                                                                                  | 51       |

| 3.5        | Illustration of a continuous memory map                                                                                                           | 53       |

| 3.6        | memory map.                                                                                                                                       | 54       |

| 3.7        | Worst-case for a requestor reading sequential addresses using a continu-                                                                          | υ.       |

|            | ous memory map                                                                                                                                    | 54       |

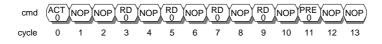

| 3.8        | Worst-case command sequence for a request consisting of four bursts                                                                               | ~ ~      |

| 3.9        | using a continuous memory map                                                                                                                     | 55<br>55 |

|            | A requestor reading sequential addresses using an interleaved memory                                                                              | 55       |

|            | map                                                                                                                                               | 56       |

| 4.1        | Example pattern sets illustrating the four different dominance classes.                                                                           | 65       |

| 4.2        | Illustration of how the dominance class of a pattern set changes as $t_{read}$                                                                    |          |

| 4.3        | is incremented or decremented                                                                                                                     | 65<br>66 |

| 4.4        | Refresh efficiency accounts for refresh patterns.                                                                                                 | 67       |

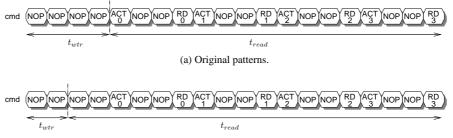

| 4.5        | Read/write efficiency accounts for switching patterns                                                                                             | 68       |

| 4.6        | Bank and conflict efficiencies remove overhead within read and write                                                                              |          |

| 47         | patterns, leaving only data bursts.                                                                                                               | 69       |

| 4.7        | Data efficiency accounts for data that is not useful to requestors, leaving only requested data bursts.                                           | 70       |

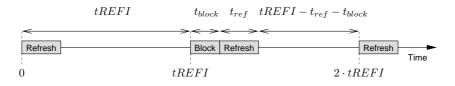

| 4.8        | The minimum distance between two refresh patterns.                                                                                                | 71       |

| 4.9        | Adding NOPs to the beginning of an access pattern may reduce the length                                                                           |          |

| 4.10       | of a switching pattern.                                                                                                                           | 74       |

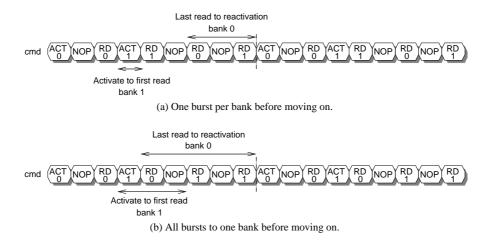

| 4.10       | Issuing all bursts to a bank before moving on to the next gives more time<br>between activate and reads/writes, and more time to precharge before |          |

|            | reactivating.                                                                                                                                     | 75       |

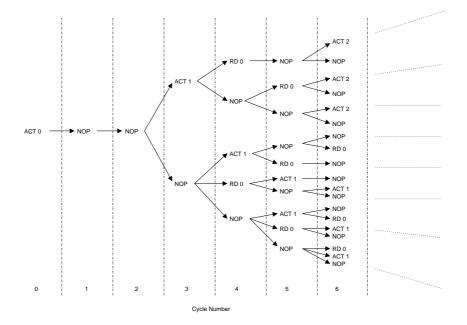

| 4.11       | The branch and bound algorithm creates pattern by exploring a tree of                                                                             |          |

|            | SDRAM commands.                                                                                                                                   | 77       |

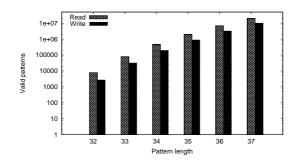

| 4.12       | Number of valid patterns fitting our design decisions at $BC = 2$ for a                                                                           | 70       |

| 4 13       | DDR2-400 SDRAM device                                                                                                                             | 79<br>80 |

|            | Prematurely scheduled activate commands result in longer access patterns.                                                                         | 81       |

|            | Conceptual illustration of the bank scheduling algorithm for $BC = 1$ .                                                                           | 82       |

|            |                                                                                                                                                   |          |

xvi

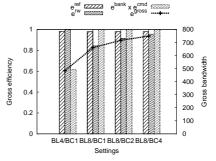

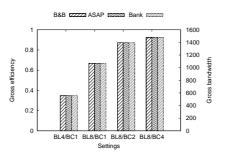

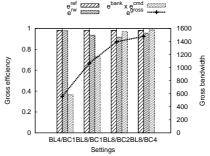

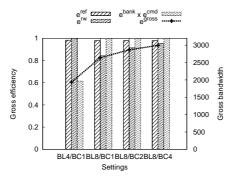

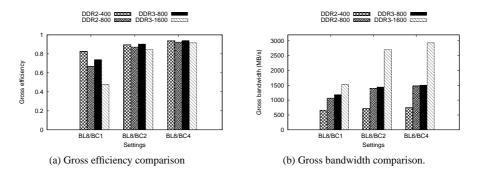

| 4.16       | Memory efficiency results for DDR2-400                                                               | 88  |

|------------|------------------------------------------------------------------------------------------------------|-----|

| 4.17       | Memory efficiency results for DDR2-800.                                                              | 89  |

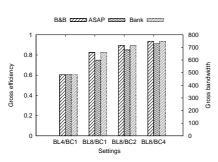

| 4.18       | Bank scheduling gross efficiency breakdown for DDR3-800                                              | 90  |

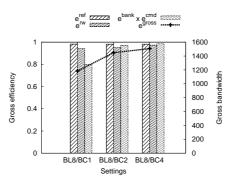

|            | Bank scheduling gross efficiency breakdown for DDR3-1600.                                            | 91  |

|            | Gross efficiency and gross bandwidth comparisons between different DDR                               | 2   |

|            | and DDR3 memories.                                                                                   | 92  |

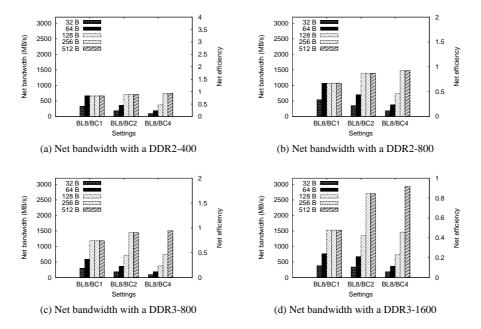

| 4.21       | Bound on net bandwidth for different memories and request sizes                                      | 93  |

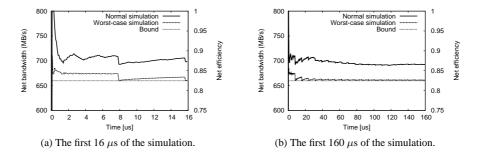

| 4.22       | Net bandwidth plotted over time for a DDR2-400 memory with and with-                                 |     |

|            | out worst-case switches.                                                                             | 94  |

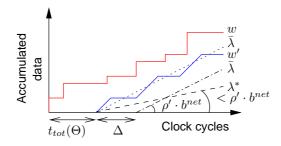

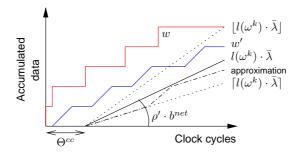

| 5.1        | A requested service curve, $\boldsymbol{w},$ a provided service curve, $\boldsymbol{w}',$ and repre- |     |

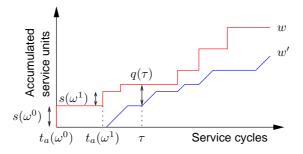

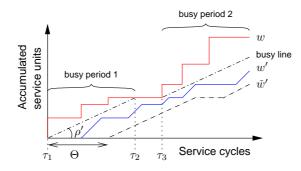

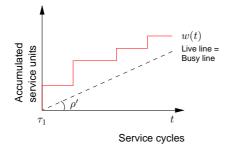

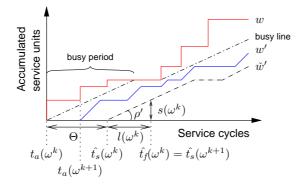

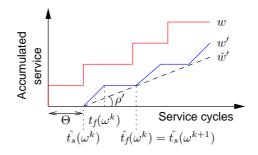

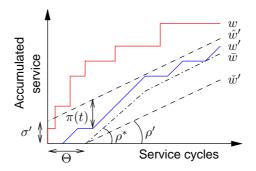

|            | sentations of the related concepts.                                                                  | 100 |

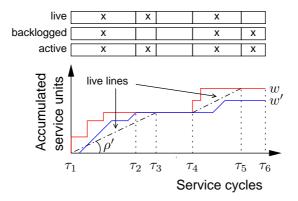

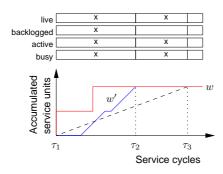

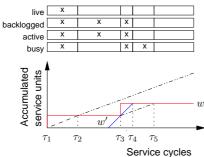

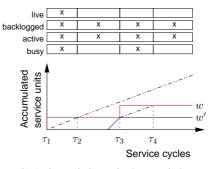

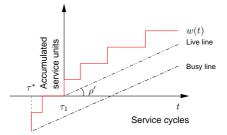

| 5.2        | Service curves showing the relation between being live, backlogged, and active.                      | 103 |

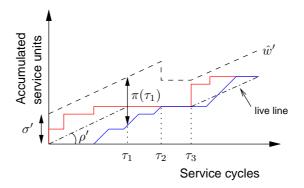

| 5.3        | The upper bound on provided service, $\hat{w}'$ , is not necessarily monotoni-                       | 100 |

| 0.0        | cally non-decreasing.                                                                                | 104 |

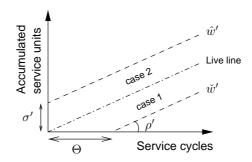

| 5.4        | Illustration of the two cases in Theorem 5.1.                                                        | 112 |

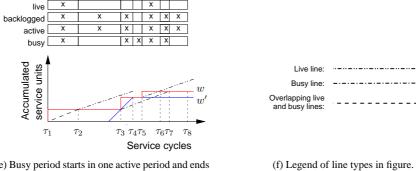

| 5.5        | Example service curves in a $\mathcal{LR}$ server.                                                   | 113 |

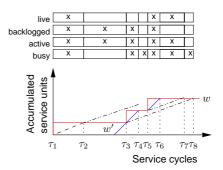

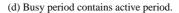

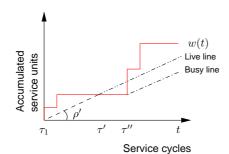

| 5.6        | Relations between busy periods and active periods.                                                   | 115 |

| 5.7        | Example of the cases in Lemma 5.13.                                                                  | 118 |

| 5.8        | The architecture of the CCSP arbiter.                                                                | 125 |

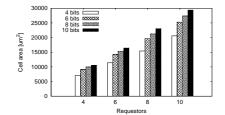

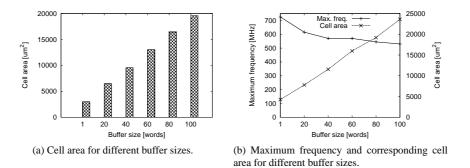

| 5.9        | Synthesis results for the CCSP arbiter.                                                              | 127 |

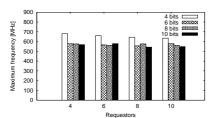

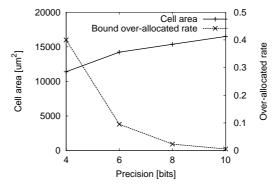

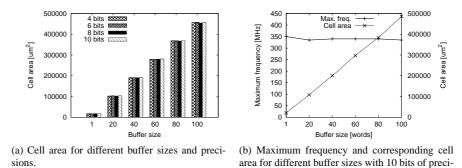

|            | The trade-off between over-allocation and cell area.                                                 | 128 |

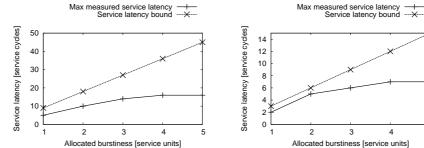

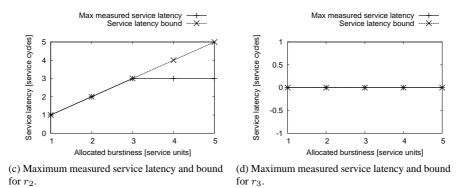

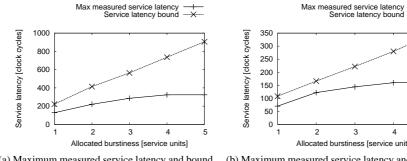

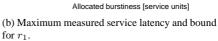

|            | Maximum measured latency and bound, expressed in service cycles, for                                 |     |

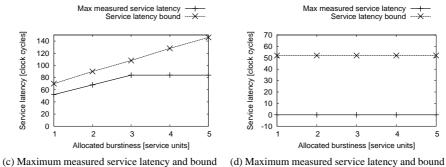

|            | the requestors in the use-case.                                                                      | 132 |

| 5.12       | Maximum measured latency and bound, expressed in clock cycles at 200                                 |     |

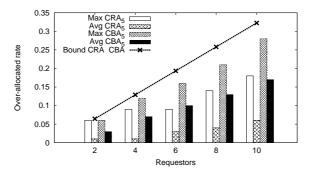

|            | MHz, for the requestors in the use-case.                                                             | 134 |

| 5.13       | Over-allocated rate for the CRA and CBA strategies.                                                  | 135 |

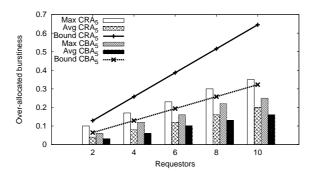

|            | Over-allocated burstiness for the CRA and CBA strategies                                             | 136 |

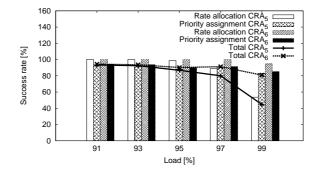

|            | Successful allocations and priority assignments for CRA and CBA                                      | 136 |

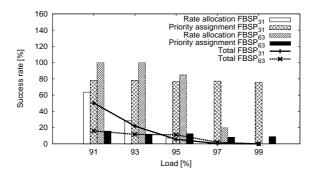

|            | Success rate when increasing precision with CRA.                                                     | 137 |

|            | Success rate when increasing precision with FBSP.                                                    | 138 |

| 6.1        | Temporally independent interfaces are created by delaying responses and                              |     |

|            | flow control                                                                                         | 143 |

| 6.2        | Illustration of worst-case starting time and finishing time in a $\mathcal{LR}$ server.              | 145 |

| 6.3        | The trade-off between service latency and net bandwidth                                              | 147 |

| 6.4        | An instance of the proposed architecture supporting two requestors                                   | 149 |

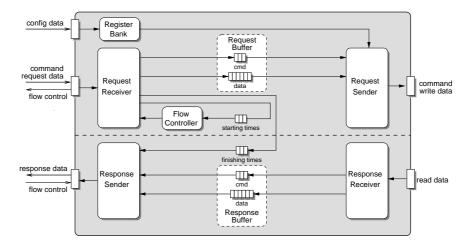

| 6.5        | Delay Block architecture.                                                                            | 150 |

| 6.6        | Diverging finishing times prevented by discrete approximation of the completion latency.             | 152 |

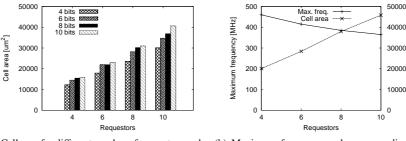

| 6.7        | Synthesis results for the Atomizer.                                                                  | 152 |

| 6.8        | Synthesis results for the Delay Block.                                                               | 155 |

| 0.8<br>6.9 | Synthesis results for the Data Bus with a CCSP arbiter.                                              | 150 |

| 0.9        | Synthesis results for the Data Dus will a CCSF afonter                                               | 137 |

### LIST OF FIGURES

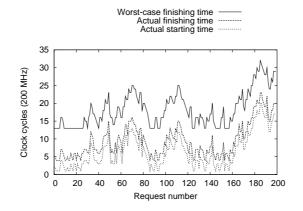

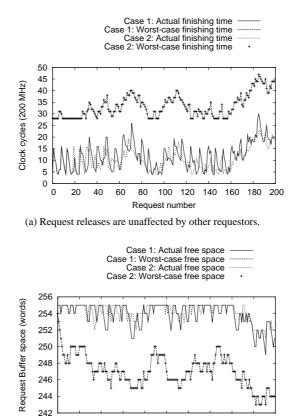

| 6.10 | The first 200 requests of $r_2$ in the SRAM use-case                                | 159 |

|------|-------------------------------------------------------------------------------------|-----|

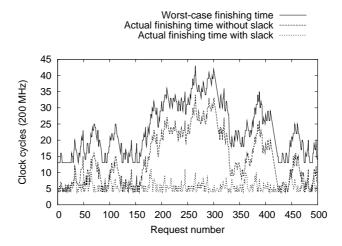

| 6.11 | Atoms finish before the computed bound, since they are served non-                  |     |

|      | preemptively                                                                        | 160 |

| 6.12 | SRAM controller behaving in a composable manner                                     | 162 |

| 6.13 | Using a work-conserving arbiter to distribute unallocated bandwidth may             |     |

|      | significantly reduce finishing times.                                               | 164 |

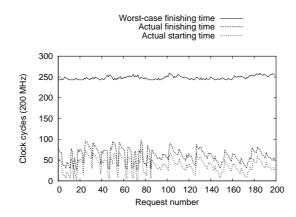

|      | The first 200 requests of $r_2$ in the SDRAM use-case                               | 165 |

| 6.15 | SDRAM controller behaving in a composable manner                                    | 167 |

|      |                                                                                     |     |

| 7.1  | Overview of the automated configuration flow                                        | 170 |

| 7.2  | Configuration of CCSP and FBSP consists of a bandwidth allocation step              |     |

|      | and a priority assignment step.                                                     | 176 |

| 7.3  | $\mathcal{LR}$ servers cannot capture service provided with multiple rates to a re- |     |

|      | questor                                                                             | 178 |

| 7.4  | The percentage of use-cases with bandwidth and latency requirements                 |     |

|      | satisfied using pattern generators with fixed and iterating burst counts            | 183 |

|      |                                                                                     |     |

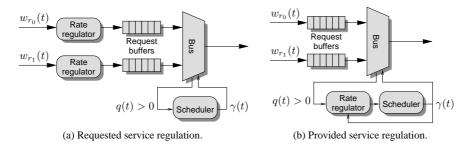

| 8.1  | Two arbiters regulating requested service and provided service, respec-             |     |

|      | tively.                                                                             | 187 |

|      |                                                                                     |     |

### xviii

### List of Tables

| 3.1 | List of relevant timing parameters for a 64 Mb x16 (512 Mb) DDR2-400 memory device. | 45  |

|-----|-------------------------------------------------------------------------------------|-----|

| 3.2 | Comparison of timing constraints in nanoseconds and clock cycles for a              | 10  |

| 5.2 | DDR2-400 and a DDR3-1600.                                                           | 50  |

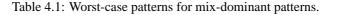

| 4.1 | Worst-case patterns for mix-dominant patterns.                                      | 71  |

| 4.2 | List of relevant timing parameters for some different 64 Mb x16 (512                |     |

|     | Mb) memory devices with page sizes of 2 KB                                          | 86  |

| 4.3 | Length of generated patterns for the DDR2-400 memory                                | 87  |

| 4.4 | Length of generated patterns for the DDR2-800 memory                                | 88  |

| 4.5 | Length of generated patterns for the DDR3-800 memory                                | 90  |

| 4.6 | Length of generated patterns for the DDR3-1600 memory                               | 91  |

| 5.1 | Reference to figure showing combinations of liveness, business, and back-           |     |

|     | log                                                                                 | 116 |

| 5.2 | Requestor configuration and service latency bounds.                                 | 129 |

| 5.3 | Bandwidth and service latency results.                                              | 130 |

| 5.4 | Bandwidth and service latency results with malfunctioning requestor us-             |     |

|     | ing a regular static-priority arbiter.                                              | 131 |

| 6.1 | SRAM use-case specification and configuration.                                      | 158 |

| 6.2 | SDRAM use-case specification and configuration.                                     | 165 |

| 7.1 | Use-case specification.                                                             | 171 |

| 7.2 | Output from pattern generation stage.                                               | 172 |

| 7.3 | Output from normalization stage.                                                    | 175 |

| 7.4 | Results from the bandwidth allocation stage.                                        | 178 |

|     |                                                                                     | -   |

### LIST OF TABLES

| 7.5 | Results from priority assignment stage                                | 179 |

|-----|-----------------------------------------------------------------------|-----|

| 7.6 | Output from denormalization stage.                                    | 180 |

| 7.7 | Allocated bandwidths and service latencies together with their corre- |     |

|     | sponding bounds.                                                      | 181 |

| 7.8 | Output from normalization stage with $BC = 2.$                        | 182 |

|     |                                                                       |     |

| A.1 | List of symbols.                                                      | 210 |

XX

## List of Algorithms

| 4.1 | Pseudo-code of ASAP scheduling algorithm.                  | 80  |

|-----|------------------------------------------------------------|-----|

| 4.2 | Pseudo-code of the bank scheduling algorithm.              | 82  |

| 6.1 | Mechanism for discrete approximation of completion latency | 153 |

| 7.1 | Optimal priority assignment algorithm.                     | 179 |

|     |                                                            |     |

LIST OF ALGORITHMS

xxii

### CHAPTER 1

### Introduction

People in modern society are surrounded by computers. This is hard to believe, considering that the electronic computer was a rare and simple calculator the size of a house little over half a century ago. Since then, we have seen an amazing development that turned these machines into computational marvels that contribute to most aspects of our daily lives. Computers became faster and cheaper, and found their way into our homes. They also became smaller and more energy efficient, resulting in portable laptop computers that accompany us when traveling. However, the majority of computers in our daily lives are not the general personal computers we use at work, school, or in the office. Instead, these are the embedded systems that are built for a particular purpose, such as our mobile phones, MP3-players, televisions, DVD-players, and navigation systems. Examples of embedded systems outside the consumer electronics domain involve the many computers inside washing machines, cars, and airplanes. The impressive development of embedded systems is not without drawbacks. As the systems become increasingly powerful and integrate more and more functionality, they also become more difficult to produce. More advanced devices consist of more hardware and software components that must be designed, integrated and verified. To stay ahead of the competition, companies have to design these complex systems in a very short time [45]. A particular challenge with embedded systems design is that they often have timing requirements, as failure to produce the right result at the right time may cause an application to malfunction.

We begin this thesis in Section 1.1 by discussing trends in embedded system design, followed by an introduction to the intended application domains and considered platforms. We then explain the problem of mapping these applications on the platform and verifying that all timing requirements are satisfied. This results in the problem statement of this thesis, presented in Section 1.2, which focuses on these issues in a main system component: the memory controller. Section 1.3 then explains how predictability, abstraction, composability, and automation reduce the mapping and verification effort of embedded systems, and introduces them as requirements on our solution. The contributions of this work are summarized in Section 1.4, before we present an outline of the rest of the thesis in Section 1.5. Lastly, the contents of the chapter are summarized in Section 1.6.

### **1.1** Trends in embedded system design

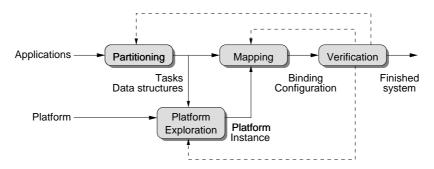

This section discusses some general aspects of embedded system design to create understanding for the different steps and the complexities involved in designing the embedded systems that surrounds us in our daily lives, such as smart phones and navigation systems. Challenges are highlighted, as well as past and current trends to help us extrapolate future problems in the field. The contents of this section revolve around the example embedded system design flow shown in Figure 1.1. The first part of the discussion considers applications, which are the input to the partitioning step in the design flow.

Figure 1.1: Example design flow comprised of a partitioning, platform exploration, mapping, and a verification stage.

### 1.1.1 Applications

The functionality provided by an embedded system is determined by its applications. An application is an independent program that performs a well-defined function for the user, such as playing audio or video content. Trends show that the amount of application software in embedded systems is rapidly increasing [45]. This evolution towards systems with more and more functionality is visible in both the consumer electronics and the automotive domains. Already a decade ago, it was shown that the amount of software in high-end consumer electronic products, such as televisions, video recorders and stereo sets, increased exponentially with an annual growth rate of about 40% [24]. Currently, convergence in application domains causes the number of applications in consumer electronic and mobile devices to increase. A prime example of this development is that the

#### 1.1. TRENDS IN EMBEDDED SYSTEM DESIGN

functionality of previously separate devices, such as MP3 players, movie players, cell phones, digital cameras, game consoles, and personal-digital assistants, are all coming together in a single hand-held device, called a smart phone. The large number of applications in these devices covers a vast space from multimedia decoding to Internet and gaming [45]. As a result of this trend, the computational load of smart phones grows exponentially and doubles every five years [108]. A similar trend of increased functionality is also visible in the automotive domain, although for different reasons. Traditional automotive systems have been implemented as federated architectures. This means that applications, such as engine control system, braking system, and multimedia system, are mapped on nearly autonomous distributed application subsystems, consisting of electronic control units (ECU), networks, sensors and actuators. A state of the art car is a complex distributed system with up to 70 ECUs [85]. For cost, dependability and weight reasons, there is a transition towards integrated architectures, where multiple applications share a common hardware base [85]. Future automotive systems are hence also expected to be highly integrated systems, executing many applications.

Apart from being functionally correct, applications may also have different types of *real-time requirements*. Some applications have *latency requirements*, which means that the result of certain computation must be finished within a specified time, called a deadline. This type of requirement is common in control applications that need to react quickly to incoming events. Other applications are pipelined and have *throughput requirements* instead of latency requirements. In this case, it is less important how long it takes to perform the pipelined computation, as long as a result is being produced often enough to sustain the required throughput. An example of an application with a throughput requirement is a video decoder that must be able to present a new video frame on a television screen with a rate of 100 Hz. This means that a new image must be displayed on the screen every 10 ms. The time to decode a frame may, however, be greater than 10 ms if the decoding process is pipelined.

Real-time requirements exist in a number of different classes. In this work, we distinguish three such classes [15], being hard real-time requirements, firm real-time requirements, and soft real-time requirements. Applications with hard real-time requirements are often *safety critical* and are primarily found in the health-care, automotive and aerospace domains. The real-time requirements of hard real-time applications, such as the brake system in a car, must always be satisfied to ensure safety of the passengers. To guarantee that hard real-time requirements are satisfied even in the presence of hardware failure, some architectures even include redundant hardware. Some applications, such as a Software-Defined Radio [77], have firm real-time requirements. Missing a firm deadline is *highly undesirable* and may result in failure to comply with a given standard, and may even violate the functional correctness of the System-on-Chip (SoC) [32, 103]. Firm real-time requirements, unlike their hard counterpart, are not safety critical, and costly measures, such as hardware redundancy, are not taken to exclude the possibility of missing a deadline. This type of requirement is hence more prevalent in domains where applications are not safety-critical, such as consumer electronics. The temporal behavior of soft real-time applications, such as media decoders, are not critical to preserve the functional correctness of the SoC. Missing a soft deadline results in quality degradation of the application output, such as causing visual artifacts in decoded video or clicks in audio playback. Although this is perceived as annoying by the user, it may be acceptable as long as it does not occur too frequently [1]. There are also applications without real-time requirements, such as a JPEG decoder or a graphical user interface. These applications do not have any timing requirements, but must still execute fast enough to be perceived as responsive by the user.

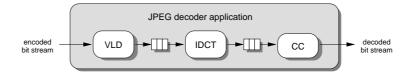

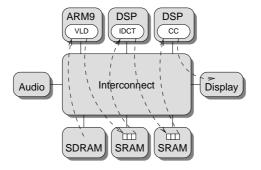

The partitioning step in Figure 1.1, partitions applications into smaller *tasks* that communicate through shared data structures. The JPEG decoder in Figure 1.2 is an example of a partitioned application. It is partitioned into three communicating tasks, being variable-length decoding (VLD), inverse-discrete cosine transform (IDCT), and color conversion (CC). The reason to partition an application is to enable parallel execution by binding the tasks to different Processing Elements (PEs) and the shared data structures to memories. This allows computations to be done faster, increasing application performance if the overhead of communication and synchronization is limited [46]. This has been demonstrated for the example JPEG decoder in [36]. As an alternative to increasing performance of a single processing element, parallel execution uses multiple processing elements that run at a lower clock frequency, reducing power consumption [117].

Figure 1.2: A JPEG decoder application consisting of three tasks.

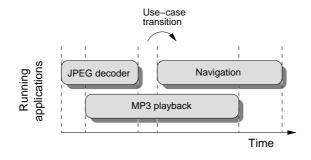

Multiple applications may execute at the same time and we refer to a set of concurrently running applications as a *use-case*. The number of use-cases in a system varies greatly, but is growing rapidly and is already in the hundreds for a high-end television. This impressive growth is intuitively understood by considering that the number of possible use-cases in a system *increases exponentially* with the number of applications. Applications can be dynamically started and stopped at any time, triggering a *use-case transition*. This is shown in Figure 1.3, where five use-cases are created as three applications start and stop their executions.

### 1.1.2 Platform-based design

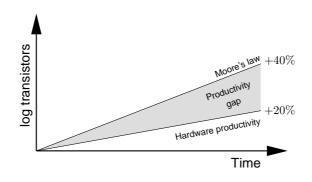

Technological advances in the semiconductor industry continuously increase the achievable density of very large-scale integrated circuits [24]. This development has followed a trend known as Moore's law [75, 76] for more than four decades. Moore's law predicts that the number of transistors that can be integrated on a chip will double every 24 months. This prediction remains valid today and is considered a self-fulfilling prophecy, as the semiconductor industry strives towards its continuation.

Figure 1.3: Starting and stopping applications causes use-case transitions.

Previously, a system was distributed over multiple chips connected on a printed circuit board. However, the increasing transistor density has enabled more and more components to be integrated on a single chip. This has resulted in a transition towards SoC solutions, where an entire system is implemented on a single chip. This development has not only reduced the size of the resulting systems, but also power dissipation and ultimately cost [95]. The increasing transistor density has many advantages and paved way for many of the complex embedded systems we enjoy today. However, the benefits of Moore's law do not come without their share of associated challenges. One of the most prominent challenges concerns design productivity [18]. According to Moore's law, the number of transistors on a chip doubles every 24 months, corresponding to an annual increase of 40%. In contrast, the hardware productivity of VLSI designers only increases annually with 20% [95]. This results in an exponentially increasing hardware productivity gap, as illustrated in Figure 1.4. A consequence if this trend is that designers are unable to make efficient use of the additional transistors provided by developments in process technology without just replicating regular structures, such as memories. Resolving this gap has been identified as one of the grand design challenges in the International Technology Roadmap for Semiconductors (ITRS) [49].

Figure 1.4: The design productivity gap.

The design productivity problem has led to adoption of *reuse methodologies*, where pre-designed and pre-verified components are reused between products [95]. However, productivity gains from reusable Intellectual Property (IP) components alone are not enough to close the productivity gap and reduce cost, due to the large associated integration effort. Additionally, a *platform-based design* approach has been proposed that promotes reuse at a higher level of abstraction [95]. A platform comprises a set of hardware and software components, specific to a particular application domain [49]. The platform software is not application code, but rather middleware (software for hardware), operating system, and compilers, required to program the platform. This may hence involve operating system kernel, hardware drivers, communication and synchronization libraries, and resource managers. The purpose of the platform is to serve as a starting point for products in the intended domain and differentiation is achieved by integrating additional components, either in hardware or software [49, 115]. Which components to add are determined during the platform exploration step in Figure 1.1. The purpose of this step is to find a suitable *platform instance* for the tasks of the considered applications that satisfies all design requirements. A drawback of reusing platforms across an application domain is that the resulting designs are slower and more expensive in terms of area and power than customized solutions. The reason is that the platform is more general than what is required for a particular design and may be slightly over-designed to leave room for future products [58]. On the other hand, platform-based design increases design productivity and reduces time-to-market, resulting in increased revenue.

In the past years, platforms for embedded systems have been progressing towards multi-processor systems-on-chip (MPSoC) architectures. This transition is motivated by diminishing returns from instruction-level parallelism, and that it is no longer possible to increase performance of a processor by increasing the clock frequency, due to power and thermal constraints [2, 44, 54]. To further increase performance without adhering to these constraints, industry has moved towards exploiting task-level parallelism by executing tasks on multiple processors [44, 96]. This trend is well-known and has been observed in many homes, since most personal computers, both stationary and portable, are now shipped with up to four processors on a single die [44]. Similarly, the number of processors on SoCs in both consumer electronics [59] and mobile phones [108] are increasing with every generation. However, the required processing power in portable consumer SoCs is expected to increase with three orders of magnitude over the next ten years, while power consumption must remain largely unaffected to maintain battery life time [50]. To satisfy this requirement, we need highly parallel heterogeneous platforms with a single or a few general purpose processors and many processing elements, to strike a good balance between performance, cost, power consumption and flexibility [34, 45, 50, 54, 108, 117]. Processing elements in this context correspond to application-specific processors or hardware accelerators that efficiently realize computationally intensive functions in hardware. The general purpose processors and the peripherals used in these architectures are expected to maintain constant complexity over time. However, ITRS indicates that the number of processing elements on a chip will increase by an order of magnitude over the next ten years [50], pushing parallel computing to its limits. The combination adding more processing elements and increasing heterogeneity results in an overall trend towards *increasing system complexity* that is expected to persist in the coming decades.

#### **1.1.3** Platform architecture

In Section 1.1.1, we mentioned that the number of applications in embedded systems is increasing. We then explained in Section 1.1.2 how increased customer demand for more applications and pressure to reduce cost and time-to-market caused embedded systems to move from being single-processor designs to being based on reusable heterogeneous multi-processor platforms. In this section, we discuss what the architectures of these platforms may look like. The discussion revolves around a general architecture template, shown in Figure 1.5. The considered architecture template applies to industrial heterogeneous multi-processor platforms, such as NXP's Nexperia [28, 34, 59], STI's Cell Broadband Engine [54], BroadCom MediaDSP [96], and Texas Instruments OMAP [34].

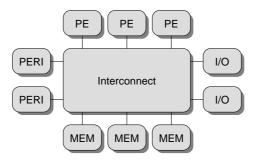

Based on the design trends explained in Section 1.1.2, we consider a platform architecture that consists of many Processing Elements (PEs). The processing elements in a platform typically consist of one or a few general-purpose RISC processors, such as ARM [12] or MIPS [73] cores. These processors orchestrate the execution on the platform by starting and stopping applications and configuring components during use-case transitions. It is also possible that some of these are high-performance processors that are used to speed up execution of code that is either legacy or inherently sequential [46]. The bulk of the computation in the platform is carried out by a large number of applicationspecific instruction-set processors , such as Digital Signal Processors (DSPs), vector processors, or very-long instruction-word processors, targeting a particular application domain. However, they may also be hardware accelerators, efficiently implementing a single computationally intensive function, such as a Fast-Fourier Transform or inversediscrete cosine transform.

Figure 1.5: The platform template considered in this thesis.

Apart from processing elements, the platform also contains memories. There are often many different types of memories, representing different cost and performance trade-offs. On-chip Static RAMs (SRAMs) are often used to store instructions or data local to the CPUs and PEs, either in form of caches or scratchpads. Being on-chip,

SRAMs have the benefit of being faster to access than off-chip memories, but they are often limited to less than a megabyte (MB) to reduce cost. In addition to local memories, there are centralized memories (MEM) that are typically shared by multiple processing elements. SRAMs may be used to implement these centralized memories, especially if local memories cannot be accessed by remote CPUs or PEs. However, many platforms have a central interface to an off-chip Synchronous Dynamic RAM (SDRAM). An advantage of SDRAMs is that a memory cell is implemented with a single transistor and a capacitor, as opposed to the six transistors required by an SRAM. SDRAMs are furthermore manufactured in large volumes in an optimized process technology. Together, these factors allow them to provide a large storage capacity, up to several gigabytes (GB), at relatively low cost. This makes SDRAMs an important component in any cost-sensitive SoC with applications using large data sets, such as video decoders. Both SRAMs and SDRAMs are volatile memories, which means that they lose the stored data whenever they are switched off. For this reason, it is common to also have non-volatile memory to store instructions and data required to boot the system. These days, this is most commonly done using flash memories. Finally, the platform contains peripherals (PERI), such as mice, keyboards, speakers and displays, and I/O devices providing connectivity to other systems. Common types of connectivity involve USB, UART, HDMI, PCI, I<sup>2</sup>E, or Ethernet.

Communicating components are connected using an interconnection fabric that can be direct wires, switches, or buses. Decreasing feature size has created a need for multihop interconnects, since it is not always possible to cross a chip in a single clock cycle. Complex SoCs hence require bridged buses or networks-on-chips [26], which are multihop interconnects that allow multiple transactions to be served in parallel.

The different hardware components, i.e. processing elements, memories, peripherals, I/O devices, and interconnect, may run at different clock frequencies. This is required either to achieve different power and performance trade-offs using dynamic voltage and frequency scaling, or because the maximum clock frequency of a component is limited. To cope with different clock frequencies, communicating components are bridged using a clock domain crossing, typically implemented using asynchronous first-in-first-out (FIFO) buffers. The considered system is hence globally-asynchronous locally-synchronous (GALS) [79].

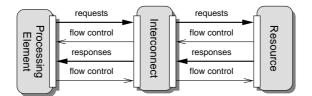

IP components in the architecture communicate by sending read and write transactions on ports. The transactions consist of requests and responses, as shown in Figure 1.6. The components communicate using a protocol, such as the Device Transaction Level (DTL) protocol [88] used by Philips and NXP, or Advanced eXtensible Interface (AXI) protocol [13] promoted by ARM. These protocols often feature a flowcontrol mechanism, as illustrated by the flow-control signals in Figure 1.6. This mechanism is typically implemented by a two-phase valid / accept handshake between the sender and receiver. The benefit of flow control is that it allows a receiving component to stall the sender if it is not ready to accept a request or a response, which is useful to prevent a buffer overflow, or to implement clock domain crossings. Throughout the figures in this thesis, standard DTL/AXI ports are colored white, while grey ports indicate other types of interfaces.

#### 1.1. TRENDS IN EMBEDDED SYSTEM DESIGN

Figure 1.6: Processing element and resource communicating via a standard protocol.

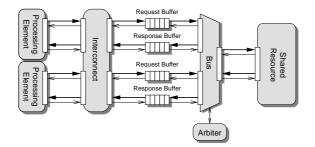

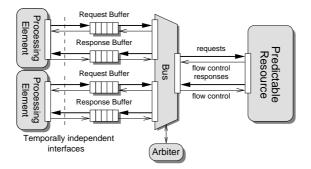

Resources, such as memories and peripherals, are often shared between multiple processing elements, since area, power and pin constraints prevent them from being duplicated. If a resource is shared, arriving requests are stored in a Request Buffer, located in front of the resource. Access to the resource is provided by a bus, controlled by a resource arbiter. The resource processes the request and stores a response in the Response Buffer of the corresponding processing element when it is finished. This is illustrated in Figure 1.7. Contemporary platforms contain a large variety of resource arbiters with different properties. One common example is Time-Division Multiplexing (TDM), which shares the resource in time among the processing elements according to a fixed periodic schedule. An advantage of this arbiter is that the service provided to a processing element is known at design time and is completely independent of others. Another example is round-robin arbitration [80], which cycles between processing elements trying to access the resource. This arbiter tries to be fair by treating all processing elements equally. In contrast, a static-priority arbiter provides differentiated service by always scheduling the processing element with the highest priority. This enables low latency to be provided to applications with tight deadlines, while applications with loose deadlines, or no deadlines, access the resource with a longer latency.

Figure 1.7: Multiple processing elements sharing a resource.

### 1.1.4 Mapping

Mapping is the process of binding applications to the platform instance, such that all functional and non-functional requirements are satisfied. The mapping process hence

takes place after applications have been partitioned and a suitable platform instance has been found, as shown in Figure 1.1. The mapping process consists of two parts. The first part deals with binding tasks and data structures to IP components in the platform instance, and the second with computing IP parameters and configurations. We proceed by discussing these steps and their associated challenges in more detail.

In the binding step, all tasks are assigned to processing elements, and shared data structures to either local or centralized memories. This process is illustrated in Figure 1.8, as the JPEG decoder application is mapped on an instance of the considered platform. The three tasks are mapped to different processing elements and the buffers for inter-task communication are mapped in centralized SRAMs. The encoded bit stream is read from an SDRAM and the decoded output is written to a display controller. The binding is a non-trivial problem, since processing elements have different performance and power consumption and memories have different capacities and access latencies. This results in a large design space that grows with the increasing system complexity, as more and more components are added to SoC platforms [49]. However, there are no industrial-strength tools that automatically derive suitable bindings, leading to that the embedded system industry often performs this step manually. Fortunately, the scope of the problem is somewhat mitigated by the increased specialization of processing elements in heterogeneous platforms. A particular implementation of a task may hence be limited to a subset of the processing elements, or even to a single core [59, 108]. Imagine, for example, if an IDCT task has to be mapped to a platform and an implementation is available as highly optimized C-code for a particular type of DSP. In this case, the binding is limited only to DSPs of this type unless alternative implementations are developed. Once a satisfactory binding is found, the bandwidth and latency requirements for all resources, such as interconnect and memories, can be derived. In this thesis, we use the term *requestor* to represent a component that performs resource access on behalf of an application. This corresponds to a port on a processing element connected to the resource through a communication channel. A partitioned application is hence associated with multiple requestors with requirements that may be very diverse in terms of bandwidth, latency, and real-time classification.

The second part of the mapping process is computing parameters and configuration settings for all IP components, such as memory controllers, interconnect and arbiters. IP parameters, such as buffer sizes, are used to instantiate components at design time. Configuration settings, on the other hand, may be different per use-case and are programmed at run time. Finding these parameters and configuration components is challenging, since all bandwidth and latency requirements of the requestors must be satisfied for all use-cases. In practice, parameters and configuration settings are often determined by trial-and-error using simulation-based techniques [45]. Transaction-level models (TLM) that capture the temporal behavior of the system may be used to speed up simulations [34], making the search for appropriate parameters more feasible, possibly at the expense of accuracy. Simulation-based techniques are predominant over analytical approaches, since the impact of changing the configuration parameters on the bandwidth and latency of a requestor is often not well understood. This problem is particularly difficult when there are multiple arbiters, often with different characteristics, interacting

Figure 1.8: Tasks are mapped to processing elements, data structures to memories, and communication channels to the interconnect as a part of the mapping process.

in the platform [108]. The configuration step is expected to be increasingly difficult as more and more heterogeneous components, executing increasingly diverse concurrent applications, are added to the platforms.

### 1.1.5 Verification

The purpose of the verification process is to assert that a system meets its specification and hence that all application requirements are satisfied. The verification process starts when a mapping has been determined in the mapping stage, as shown in Figure 1.1. The mapping is considered successful if all application requirements are satisfied. Otherwise, if verification fails, it is time to consider a different task partitioning, a different mapping, or a different platform instance, as indicated by the dashed back-arrows in the figure.

Verification is typically done by system-level simulation of the applications executing on the platform instance. The simulation speed of a complete system is very slow. For this reason, verification is sometimes performed using transaction-level models of the components, enabling the accuracy of the verification to be traded for increased simulation speed. Simulation-based verification of real-time requirements is complicated by resource sharing, which causes *scheduling interference* between requestors, as they have to wait for each other before accessing the resource. Interference makes the temporal behavior of concurrently executing applications inter-dependent, resulting in three problems. The first problem is that it is not sufficient to verify that the requirements of each application are satisfied when executing individually. Instead, all concurrently executing applications have to be verified together for all use-cases, causing the verification complexity of the system to *increase exponentially* with the number of applications [37]. However, system-level simulation of all use-cases is far too slow to be feasible in practice. As a result, industry often resorts to reducing the coverage and verifying only a subset of use-cases that have the tightest requirements [34, 103]. The second problem is that verification of a use-case cannot begin until all applications it comprises are available. Timely completion of the verification process hence depends on the availability of the applications, which may be developed by different teams both inside and outside the company. The last problem with application dependencies is that use-case verification becomes a *circular process* that must be repeated if an application is added, removed, or modified [60]. Together these three problems contribute to making the integration and verification process a dominant part of SoC development, both in terms of time and money. Currently, verification engineers currently outnumber designers with a ratio of two to one for complex designs and the effort in system-level verification is expected to increase in the future [49].

An alternative to simulation-based verification is to analytically verify that requirements are satisfied using a formal performance analysis framework, such as network calculus [25] or data-flow analysis [100]. These frameworks can be used to derive hard performance guarantees on latency or throughput of an application, provided that worstcase execution times of its tasks are known. Firm performance guarantees, on the other hand, can be analytically derived based on execution time estimates. However, in this case it is important to know the quality of the estimates and the assumptions under which they are valid. Formal methods are not necessarily faster than simulation-based techniques, considering that the run-time of mapping and verification algorithms can be very long. Formal methods do, however, guarantee coverage of all possible initial states, input sequences, and interactions with other requestors in shared resources, assuming conservative execution times for all tasks. This contrasts to the poor coverage achieved by simulation. The time required to develop formal performance models is not negligible, but these models can be reused together with the software or hardware block they model. Verification of real-time requirements using simulation-based techniques, on the other hand, cannot be reused. The problem with formal verification is that it requires performance models of the software, the hardware, and the mapping [15, 62]. Suitable application models, such as data-flow graphs, exist, but are not yet widely adopted by industry. Most industrial hardware has furthermore not been designed with formal analysis in mind. There have been recent advances in the research community, where some IP components have been proposed together with corresponding performance models [39]. However, a satisfactory solution has not yet been developed for SDRAM memories. This prevents formal analysis techniques from being applied to many platforms, since SDRAMs are essential to satisfy large storage requirements at a reasonable cost. The reason SDRAM memories are difficult to combine with formal analysis is due to a combination of a complex temporal behavior that is inherent to their architecture, and contradictory requestor requirements. The next section elaborates on these problems.

#### **1.1.6 SDRAM and real-time requirements**

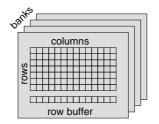

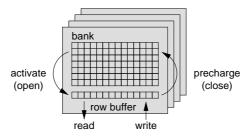

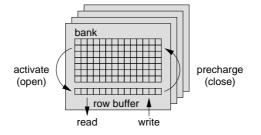

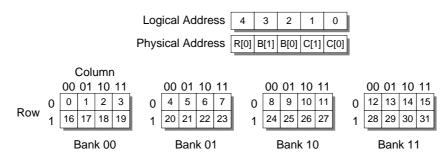

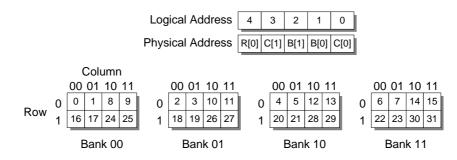

SDRAM memories are challenging to use in systems with real-time requirements because of their internal architecture. An SDRAM memory comprises a number of banks, each containing a memory array with a matrix-like structure, consisting of rows and columns [51]. A simple illustration of this architecture is shown in Figure 1.9. Each bank has a row buffer that can hold one open row at a time, and read and write operations are only allowed to the open row. Before opening a new row in a bank, the contents of the

#### 1.1. TRENDS IN EMBEDDED SYSTEM DESIGN

currently open row are copied back into the memory array. The elements in the memory arrays are implemented with a single capacitor and a resistor, where a charged capacitor represents a one and an empty capacitor a zero. The capacitor loses its charge over time due to leakage and must be refreshed regularly to retain the stored data.

Figure 1.9: The SDRAM architecture consists of banks, rows, and columns.

The SDRAM architecture causes the offered bandwidth and the time to serve a memory request to depend on three things. First, there is a dependency on the row targeted by the request and the rows that are currently open in the banks. The reason is that a request targeting an open row can be served immediately, while a request targeting a closed row must wait until the current open row has been closed and the required row has been opened. The overhead from opening and closing rows results in additional latency, as well as idle cycles on the data bus. The latter implies a reduction of the offered bandwidth. The second dependency is on the direction (read/write) of the current and previous request. The reason for this dependency is that the data bus is bi-directional and requires a number of clock cycles to change direction from read to write or write to read, again adding latency and wasting bandwidth. The last dependency is on the temporal alignment with respect to refresh operations, since a refresh operation requires tens of clock cycles during which no data can be transferred on the data bus. Together, these three dependencies create large variations in the time required serve a read or a write request. The first two dependencies are especially problematic, since they involve previous requests that may have been issued by other requestors sharing the resource. This creates resource interference between requestors, where the time required by the resource to serve a scheduled request from one requestor depends on other requestors. These effects make it very difficult to bound the bandwidth offered by the memory and the latency of memory requests at design time, which is required to support firm and hard real-time requirements.

We proceed by elaborating on the requirements of SDRAM requestors, and explain what makes them contradictory and difficult to satisfy. SDRAM requestors are categorized as either *latency critical* or *latency tolerant*. Latency-critical requestors require low-latency memory accesses to reduce the number of stall cycles on the processing elements. This is typical for processing elements supporting only a few outstanding transactions and that store data in a remote memory, such as an SDRAM. When no more transactions can be issued, the processing element blocks until a response has been returned, potentially resulting in long stalls [54]. This problem is often mitigated by using a cache to store commonly used data locally, significantly reducing the average memory access latency for applications with good locality. However, many processing elements still spend a significant number of clock cycles waiting for data, due to long latencies in the interconnect and memory controller. This problem got increasingly severe throughout the single-processor era, since processor speed increased faster than memory speed. In fact, both processor and memory speeds increased exponentially, but with different exponents, causing the difference between the two to also increase exponentially [118]. This observation has resulted in the theory that the performance of many applications will eventually be dominated by the memory latency, a situation that is known as hitting the memory wall [118]. The effects of the memory wall can be observed in transactionbased workloads and high performance scientific computing [68], where processors can stall up to 95% of the time. The recent step to multi-processor platforms has reduced the clock frequencies of processors [2], which should mitigate the effects of the memory wall. However, the cumulative memory bandwidth requirement of all processing elements is still increasing, adding a new dimension to the problem.

Some applications, such as media processing, can often be implemented in a pipelined fashion. The requestors of these applications are more latency-tolerant, but require guaranteed bandwidth to sustain their throughput requirements. In this case, higher bandwidth enables higher resolutions and support for more functionality, such as additional tasks that improve the quality of the output. However, external memory bandwidth is a *scarce resource* in many platforms. The reason is that an SDRAM controller is an expensive component both in terms of area and power consumption. Adding more memory controllers, or making the SDRAM interface wider, requires more pins. More pins further increases both the area and power consumption, and may also require a more expensive packaging. Using multiple memory controllers is hence often not an option, making it important to use the existing SDRAM bandwidth as efficiently as possible.

The requirements of latency-critical and latency-tolerant requestors are challenging to satisfy, since low latency and high offered bandwidth are inherently contradictory properties for SDRAMs. The memory is efficiently utilized by limiting the number of switches between reads and writes and using large requests to make better use of an open row. Providing low latency to critical requestors, on the other hand, is achieved by letting them switch directions immediately and preempt less important requestors, potentially closing the open rows they are using. Both of these actions reduce latency for critical requestors at the expense of a reduction of the bandwidth offered by the SDRAM.

### **1.2 Problem statement**

The high-level problem addressed in this thesis is to design a memory controller that satisfies the real-time requirements of applications in embedded systems, thereby reducing the mapping and verification effort. More specifically, the proposed memory controller should address the diversity of contemporary platforms by supporting different types of memories (SRAM and SDRAM in particular) and arbiters. The memory controller must

#### 1.3. REQUIREMENTS

use the memory bandwidth efficiently, since it is a scarce resource that must be carefully utilized. To reduce the mapping effort, the memory controller should be supported by tooling that *automatically determines instantiation parameters and configuration settings* for all components in the architecture, such that all application requirements are satisfied. The memory controller should *improve verification coverage* by enabling formal verification of real-time requirements. It should furthermore *reduce the verification complexity* by enabling independent verification of applications using either formal methods or simulation-based techniques.

# **1.3 Requirements**