## High-Level Power Estimation and Optimization of DRAMs

Karthik Chandrasekar

## Hoog-niveau Approximatie en Optimalisatie van DRAM Vermogen

Karthik Chandrasekar

# High-Level Power Estimation and Optimization of DRAMs

### **Proefschrift**

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.ir. K.C.A.M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op dag 03 Oktober 2014 om 15.00 uur

> door Karthik Chandrasekar

Ingenieur (ir.)

Master of Science (M.Sc.) in Computer Engineering

geboren te Chennai, India

Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. K.G.W Goossens

Copromotor:

Dr. K.B. Åkesson

### Samenstelling promotiecommissie:

Rector Magnificus, voorzitter

Prof.dr. K.G.W. Goossens, Technische Universiteit Delft, promotor

Dr. K.B. Åkesson, Czech Technical University in Prague, copromotor

Prof.dr. N. Wehn,

Prof.dr. J. Pineda de Gyvez,

Prof.dr. K.L.M. Bertels,

Prof.dr. H.J. Sips,

Dr. S.D. Cotofana,

Technische Universiteit Eindhoven

Technische Universiteit Delft

Technische Universiteit Delft

Technische Universiteit Delft

Prof. dr. C.I.M. Beenakker, Technische Universiteit Delft, reservelid

The work in this thesis was supported by the COMCAS EU project (CA 501).

### Copyright ©2014 Karthik Chandrasekar

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means without the prior written permission from the copyright owner.

## Acknowledgments

I would like to thank my promoter, Prof. Kees Goossens, for being a great advisor and teacher during my PhD. He gave me invaluable guidance and pivotal feedback throughout and continuously drove me to do better and better.

I also wish to express my gratitude to Dr. Benny Akesson, my PhD supervisor for always appreciating every small idea and work that I proposed and spending incalculable hours evaluating and reviewing them.

I would also like to convey my sincere thanks to Dr. Christian Weis for his always ready to help attitude and unlimited ideas on DRAM-related research. In collaborating with him, not only did I gain significant knowledge of DRAMs but also a good friend. This collaboration would not have been as fruitful, if not for Prof. Norbert Wehn, who constantly encouraged and inspired us to improve our work. I cannot thank him enough for all his help. I would also like to specially thank Mathias Jung for sparing his time and effort in taking this collaboration forward and for inviting me to different social events in Kaiserslautern.

I would also like to communicate my appreciation to Prof. Koen Bertels for always being enthusiastic and willing to help the students in his group. I also want to deeply thank the current and former members of the Memory Team at TU Eindhoven, Sven Goossens, Manil Gomony, Yonghui Li, Tim Kouters and Jasper Kuijsten for all the numerous discussions, meetings, reviews and feedback on various aspects of my PhD work. I would also like to thank members of the CompSoc Team from TU Delft and TU Eindhoven Anca, Andrew, Aqeel, Ashkan, Davit, Jude, Martijn, Pavel and Shube for being great team players and good friends. I would also like to appreciate Lidwina, Marja and Rian for their immeasurable support and assistance throughout my PhD.

I would also like to thank my office mates at Eindhoven (in alphabetical order), Alexandre, Francesco, Hamid, Rosilde, Sebastian and Umar for all the crazy times both at work and outside. I would also like to thank all my friends in Delft and Eindhoven, Gokul, Chocka, Shena, Mahi, Silesh, Arvind, Ram, Sangi, Ganesh, Santi and others who made my stay in the Netherlands fun and memorable.

I wish to acknowledge the role of Prof. Venkateswaran Nagarajan of WARFT, who has been my true Guru and mentor and motivated me to take up a PhD.

I am very grateful to my parents and my sister who have been the source of my strength throughout my PhD with their constant encouragement and love.

## Summary

Embedded systems have become an integral part of our life in the last few years in multifarious ways, be it in mobile phones, portable audio players, smart watches or even cars. Most embedded systems fall under the category of consumer electronics, such as televisions, mobile devices, and wearable electronics. With several players competing in this market, manufacturers of embedded systems continue to add more functionality to these devices to make them more user friendly, and often equip them with a very high resolution display and graphics support, and better computing and Internet capabilities. Unfortunately, they are often constrained by tight power/energy budgets, since battery capacity does not improve at the same rate as computing power. While there is clearly much progress to be made in harnessing all the possibilities of embedded systems, limitations in battery capacities, thermal constraints and power/energy budgets surely hinder this progress. Although technology scaling has traditionally addressed both the power minimization and high-performance requirements, with Moore's law nearing its limits, the development of energy-efficient system designs has become critically important. Thus, to be able to continue to provide new and improved features in embedded systems, design-time and run-time power management and minimization holds the key. As a consequence, power optimization has become one of the most defining aspects of designing modern embedded systems.

To design such high-performance and energy-efficient embedded systems, it is extremely important to address two basic issues: (1) accurate estimation of power consumption of all system components during early design stages and (2) deriving power optimization solutions that do not negatively impact system performance.

In this thesis, we aim to address these two issues for one of the most important components in modern embedded systems: DRAM memories. Towards this, we propose a high-precision DRAM power model (DRAMPower) and a set of performance-neutral DRAM power-down strategies.

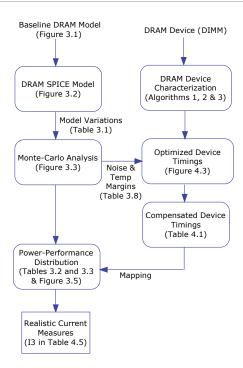

DRAMPower is a high-level DRAM power model that performs high-precision modeling of the power consumption of different DRAM operations, state transitions and power-saving modes at the cycle-accurate level. To further improve the accuracy of DRAMPower's power/energy estimates, we derive better than worst-case and realistic measures for the JEDEC current metrics instead of vendor-provided worst-case measures from device datasheets.

Towards this, we modify a SPICE-based circuit-level DRAM architecture and power model and derive better than worst-case current measures under nominal operating conditions applicable to a majority of DRAM devices (>97%) with any given configuration (capacity, data width and frequency). Besides these better than worst-case current measures, we also propose a generic post-manufacturing power and performance characterization methodology for DRAMs that can help identify the realistic current estimates and optimized set of timing measures for a given DRAM device, thereby further improving the accuracy of the power and energy estimates for that particular DRAM device.

To optimize DRAM power consumption, we propose a set of performance-neutral DRAM power-down strategies coupled with a power management policy that for any given use-case (access granularity, page policy and memory type) achieves significant power savings without impacting its worst-case performance (bandwidth and latency) guarantees.

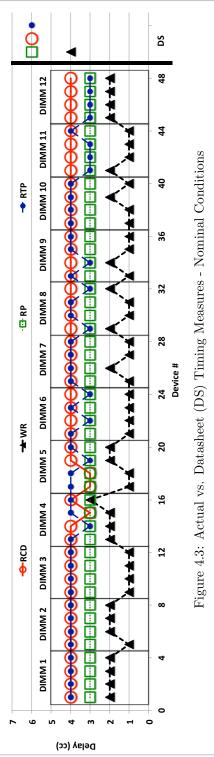

We verify the pessimism in DRAM currents and four critical DRAM timing parameters as provided in the datasheets, by experimentally evaluating 48 DDR3 devices of the same configuration. We further derive optimal set of timings using the performance characterization algorithm, at which the DRAM can operate successfully under worst-case run-time conditions, without increasing its energy consumption. We observed up to of 33.3% and 25.9% reduction in DRAM read and write latencies and 17.7% and 15.4% improvement in energy efficiency.

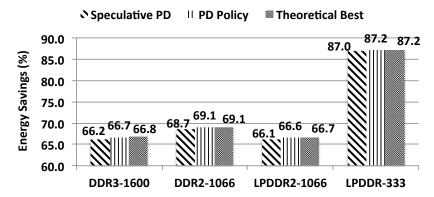

We validate DRAMPower model against a circuit-level DRAM power model and verify it against real power measurements from hardware for different DRAM operations. We observed between 1-8% difference in power estimates, with an average of 97% accuracy. We also evaluated the power-management policy and power-down strategies and observed significant energy savings (close to theoretical optimal) at very marginal average-case performance penalty without impacting any of the original latency and bandwidth guarantees.

## Samenvatting

Embedded systemen zijn de laatste jaren een integraal onderdeel van ons leven geworden; je komt ze tegen op enorm veel verschillende plaatsen, zoals in mobiele telefoons, draagbare muziekspelers, smart watches en zelfs in auto's. De meeste embedded systemen vallen binnen de consumenten elektronica, zoals bijvoorbeeld, televisies, mobiele apparaten, en draagbare elektronica. Verschillende spelers concurreren op deze markt, waardoor fabrikanten van embedded systemen continue steeds meer functionaliteit toevoegen aan deze apparaten om ze gebruiksvriendelijker te maken. Daarnaast worden ze vaak uitgerust met een scherm en ondersteuning voor zeer hoge resolutie graphics, en steeds beter wordende reken- en internetmogelijkheden.

Jammer genoeg worden fabrikanten vaak beperkt door krappe vermogens / energiebudgetten, aangezien de batterijcapaciteit niet zo snel vooruit gaat als het bruikbare rekenvermogen. Hoewel er duidelijk veel voortgang is geboekt in het exploiteren van alle mogelijkheden van gentegreerde system, ondervindt men toch hinder van de beperkingen van de maximale batterijcapaciteit, werkingstemperatuur en vermogens/energiebudgetten. Technologieschaling betekende traditioneel gezien zowel een vermogensminimalisatie als een prestatieverbetering voor veeleisende systemen, maar omdat de wet van Moore tegen zijn limieten aan loopt, wordt de ontwikkeling van energie-efficinte systeemontwerpen van cruciaal belang. De sleutel tot het kunnen blijven verbeteren en uitbreiden van de functionaliteit van embedded systemen, is het beheren en minimaliseren van het opgenomen vermogen, zowel in de ontwerpfase als tijdens de levensduur van het systeem.

Voor het ontwerp van energie-efficinte gentegreerde systemen met hoge prestaties is het zeer belangrijk om twee basisproblemen te adresseren: (1) nauwkeurige approximatie van het opgenomen vermogen van alle systeemcomponenten tijdens de vroege ontwerpfases en (2) vermogensoptimalisatieoplossingen zonder negatieve effecten op de systeemprestaties.

In dit proefschrift adresseren we deze twee problemen voor een van de belangrijkste componenten in moderne embedded systemen: DRAM geheugens. We introduceren een nauwkeurig DRAM vermogensmodel (DRAMPower), en een set prestatie-neutrale DRAM power-down strategien.

DRAMPower is een hoog-niveau DRAM vermogensmodel, dat zeer nauwkeurig het opgenomen vermogen van verschillende DRAM operaties, toestandsovergangen en energiebesparende modi modelleert, op een cycle-nauwkeurige tijdschaal. Om de precisie van DRAMPowers vermogen/energieapproximaties te verbeteren, leiden we realistische beter-dan-worst-case waarden af voor de JEDEC stromen, die de door de fabrikanten aangeleverde worst-case waarden uit de datasheet vervangen.

Om dit te realiseren passen we een SPICE-gebaseerd circuitniveau DRAM architectuur- en vermogensmodel aan, en we leiden hieruit af wat de beter-danworst-case stroomwaarden onder nominale omstandigheden zijn. Deze zijn toepasbaar op de meerderheid van de DRAM geheugens (>97%) met een willekeurige configuratie (opslagcapaciteit, databusbreedte, en klokfrequentie).

Naast deze beter-dan-worst-case stroomwaarden introduceren we ook een generieke post-productie vermogens- en prestatiekarakterisatiemethode voor DRAM geheugens die kan helpen bij het identificeren van realistische stroomwaarden en een geoptimaliseerde set van timings voor een specifieke DRAM chip, waardoor de nauwkeurigheid van de vermogens- en energieapproximatie voor deze chip verbeterd wordt.

Om het opgenomen vermogen van DRAM te optimaliseren, stellen we een set met prestatie-neutrale DRAM power-down strategien voor, gekoppeld aan een vermogensmanagementpolicy, die voor iedere gegeven use case (lees- schrijfgranulariteit, page policy en geheugentype) een significante vermogensbesparing oplevert, zonder daarbij af te doen aan de worst-case prestatie-garanties (bandbreedte en latency).

We verifiren dat de gespecificeerde DRAM stromen en vier kritische DRAM timing parameters in de datasheets pessimistisch zijn, door empirisch 48 DDR3 identieke chips te evalueren. Daarnaast leiden we een optimale set timings af met behulp van het prestatiekarakterisatiealgoritme. Bij het gebruik van deze timings functioneert het DRAM nog steeds in worst-case omstandigheden, zonder dat het energieverbruik stijgt. We zien dat een reductie tot respectievelijk 33.3% en 25.9% van de DRAM lees- en schrijflatency mogelijk is, in combinatie met een verbetering van de energie-efficintie van respectievelijk 17.7% en 15.4%.

We verifiren de correcte werking van DRAMPower door een vergelijking met een DRAM model op circuit-niveau, en een vergelijking met echte hardwaremetinging van verschillende DRAM operaties. We observeren een verschil van 1-8% in de vermogensschattingen, met een gemiddelde nauwkeurigheid van 97%. We evalueren ook de vermogensmanagementpolicy en power-down strategien en zien daarbij significante energiebesparingen (dicht bij het theoretische optimum) tegen een zeer marginale average-case presatatieafname, zonder effect op de originele latency- en bandbreedtegaranties.

### Table of contents

| Li | st of | Table  | s                                               | xviii |

|----|-------|--------|-------------------------------------------------|-------|

| Li | st of | Figur  | es                                              | xix   |

| 1  | Intr  | oducti | ion                                             | 1     |

|    | 1.1   | Proble | em Statement                                    | 1     |

|    |       | 1.1.1  | Background: Generic DRAM Architecture           | 2     |

|    |       | 1.1.2  | Problem I: DRAM Power Modeling                  | 5     |

|    |       | 1.1.3  | Problem II: Run-Time DRAM Power Optimization    | 7     |

|    | 1.2   | Propo  | sed Solutions                                   | 9     |

|    |       | 1.2.1  | Improved DRAM Power Modeling and Estimation     | 9     |

|    |       | 1.2.2  | Performance-Neutral Power Optimization of DRAMs | 12    |

|    | 1.3   | Contr  | ibutions                                        | 15    |

|    | 1.4   | Organ  | nization of this Thesis                         | 18    |

| 2  | Cyc   | le-Acc | curate Power Modeling of DRAMs                  | 19    |

|    | 2.1   |        | ed Work                                         | 20    |

|    | 2.2   | Backg  | ground on DRAM currents                         | 21    |

|    | 2.3   | Our A  | Approach                                        | 22    |

|    | 2.4   |        | ling Basic Operations                           | 24    |

|    |       | 2.4.1  | Activate and Precharge Command Power            | 25    |

|    |       | 2.4.2  | Read and Write Command Power                    | 28    |

|    |       | 2.4.3  | Background, IO and Termination Power            | 31    |

|    | 2.5   | Model  | ling State Transitions                          | 32    |

|    |       | 2.5.1  | Transition into Precharge Power-down            | 32    |

|    |       | 2.5.2  | Transition into Active Power-down               | 33    |

|    |       | 2.5.3  | Refresh Transition                              | 35    |

|    |       | 2.5.4  | Self-Refresh Mode Transition                    | 36    |

|    |       | 2.5.5  | Transaction and Trace Power Computation         | 38    |

|    | 2.6   | Adapt  | ting to Mobile and Wide IO DRAMs                | 39    |

|   | 2.7 | DRAMPower Tool                                          |

|---|-----|---------------------------------------------------------|

|   |     | 2.7.1 DRAMPower Tool Flow                               |

|   |     | 2.7.2 Command Scheduler                                 |

|   | 2.8 | Conclusion                                              |

| 3 | Var | iation-Aware Power Estimation of DRAMs 45               |

|   | 3.1 | Introduction                                            |

|   | 3.2 | Sources of Variation                                    |

|   | 3.3 | Background - DRAM Modeling in SPICE 47                  |

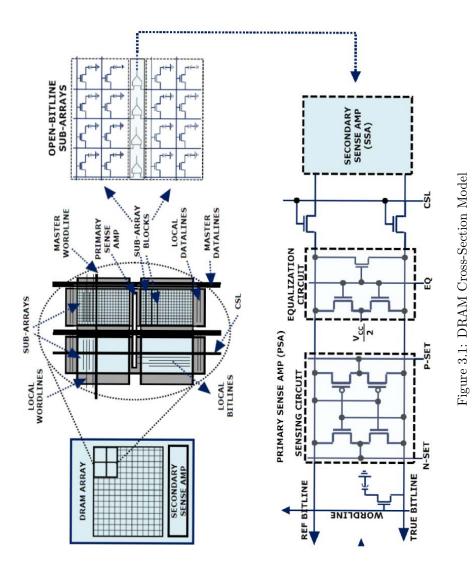

|   |     | 3.3.1 Baseline DRAM Cross-Section Model 47              |

|   |     | 3.3.2 DRAM Cross-Section SPICE Simulations 49           |

|   | 3.4 | Baseline Monte-Carlo Analysis                           |

|   | 3.5 | System Parameters Impact on Variation                   |

|   | 3.6 | DRAM Memory Characterization                            |

|   |     | 3.6.1 Requirements and Solutions                        |

|   |     | 3.6.2 DRAM Characterization Algorithms 60               |

|   |     | 3.6.3 Conservative Voltage-Temperature Compensations 68 |

|   | 3.7 | Related Work                                            |

|   | 3.8 | Conclusions                                             |

| 4 | Ver | ification & Validation of DRAMPower67                   |

|   | 4.1 | Introduction                                            |

|   | 4.2 | Experimental Setup                                      |

|   | 4.3 | Experiments                                             |

|   |     | 4.3.1 Verifying DRAM Performance Variations             |

|   |     | 4.3.2 Verifying DRAM Power Variations                   |

|   |     | 4.3.3 Verifying and Validating DRAMPower                |

|   | 4.4 | Conclusion                                              |

| 5 | Rea | d-Time DRAM Power-Down Strategies 87                    |

|   | 5.1 | Introduction                                            |

|   | 5.2 | Related Work                                            |

|   | 5.3 | Background                                              |

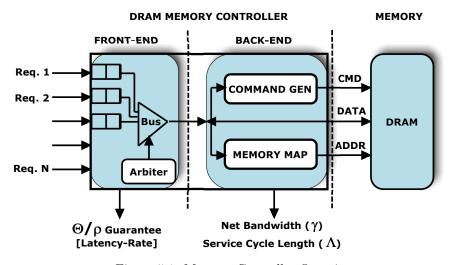

|   |     | 5.3.1 Memory Controller                                 |

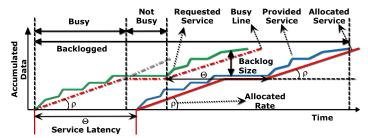

|   |     | 5.3.2 Arbiters and Latency-Rate Servers 91              |

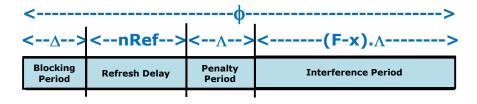

|   |     | 5.3.3 Deriving Memory Controller Guarantees 93          |

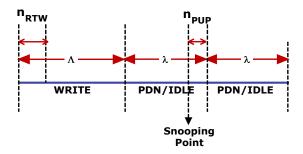

|   | 5.4 | Real-Time Power-Down Strategies                         |

|   |     | 5.4.1 Conservative Strategy                             |

|   |     | 5.4.2 Aggressive Strategy                               |

|   | 5.5 | Impact of Speculative Strategies                        |

|   | 5.6 | Power Management Policy                                 |

|   | 5.7 | Experiments and Results                                 |

|   |     | 5.7.1 Power-Management Policy                           |

|   |     | 5.7.2 Experimental Setup                                |

|   |     |                                                         |

|              |      | 5.7.3 Impact on Performance Guarantees    |

|--------------|------|-------------------------------------------|

|              |      | 5.7.4 Power-Saving Efficiency             |

|              | 5.8  | Conclusion                                |

| 6            | Cor  | aclusions and future work                 |

|              | 6.1  | Conclusions                               |

|              | 6.2  | Future work                               |

| A            | Pow  | ver Measurements                          |

|              | A.1  | Current Measures - Datasheet vs. Hardware |

|              | A.2  | DRAMPower Evaluation                      |

|              |      | A.2.1 Activation - Precharge Scaling      |

|              |      | A.2.2 Read / Write Scaling                |

|              |      | A.2.3 Bank Interleaving - Reads / Writes  |

|              |      | A.2.4 Impact of State Transitions         |

| В            | List | of Publications                           |

| $\mathbf{C}$ | Abo  | out the Author                            |

| K. Chandrasekar | High-Level Power Estimation and Optimization of DRAMs |

|-----------------|-------------------------------------------------------|

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

## List of Tables

| 1.1 | Micron DDR3-800 Timing Constraints                                   | 4   |

|-----|----------------------------------------------------------------------|-----|

| 1.2 | Distribution of Current Consumption                                  | 6   |

| 1.3 | Accuracy of State-of-the-art power models vs. DRAMPower              | 12  |

| 2.1 | DDR3 Current Measures                                                | 22  |

| 2.2 | Transaction Lengths                                                  | 38  |

| 2.3 | Average Power Consumption of Basic Memory Operations                 | 41  |

| 3.1 | Transistor Process Parameter Variations                              | 52  |

| 3.2 | Variation Impact on Timing Measures $@+85^{\circ}C$ and $1.425V$     | 53  |

| 3.3 | Variation Impact on Current Measures @ $+85^{\circ}$ C and $1.575$ V | 54  |

| 3.4 | System Parameters Vs. Currents                                       | 56  |

| 3.5 | Multi-Parameter Impact on Currents                                   | 57  |

| 3.6 | Test Sets                                                            | 59  |

| 3.7 | Impact of Noise and Temperature on Timings                           | 63  |

| 3.8 | Conservative Margins                                                 | 64  |

| 4.1 | Test Measures and Results                                            | 72  |

| 4.2 | Impact on Read Latency and Bandwidth                                 | 73  |

| 4.3 | Impact on Write Latency and Bandwidth                                | 73  |

| 4.4 | DIMM Current Measures under worst-case operating conditions          | 77  |

| 4.5 | Impact on Current Measures                                           | 78  |

| 4.6 | Comparison of DRAMPower and Micron against Measurements              | 86  |

| 5.1 | Difference in Worst-Case Bandwidth and Latency                       |     |

| 5.2 | Energy Consumption using different policies                          | 105 |

| K. Chandrasekar | High-Level Power Estimation and Optimization of DRAMs |

|-----------------|-------------------------------------------------------|

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

|                 |                                                       |

## List of Figures

| 1.1  | Mobile Platform Power Consumption (Adapted from [14])              | 2  |

|------|--------------------------------------------------------------------|----|

| 1.2  | DRAM Organization in the System context                            | 3  |

| 1.3  | Probability Density Function of Current Measures                   | 6  |

| 1.4  | Energy Consumption of DRAM Operations                              | 8  |

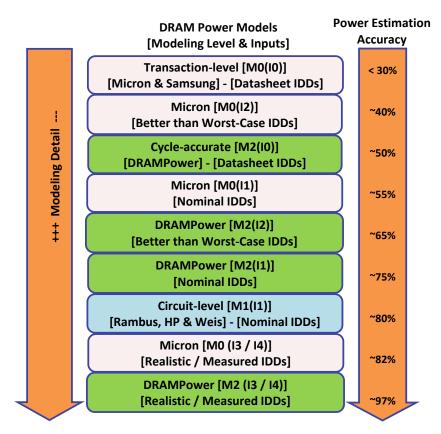

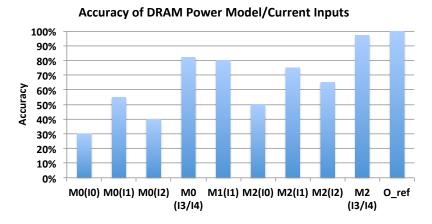

| 1.5  | DRAM Power Models vs. Accuracy                                     | 13 |

| 1.6  | Accuracy of DRAM Power Models and Current Measures                 | 13 |

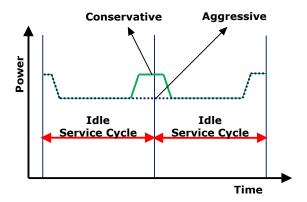

| 1.7  | Conservative vs. Aggressive Power-Down Strategies                  | 15 |

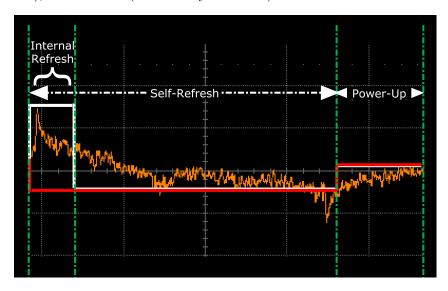

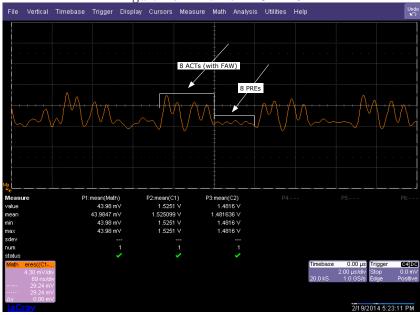

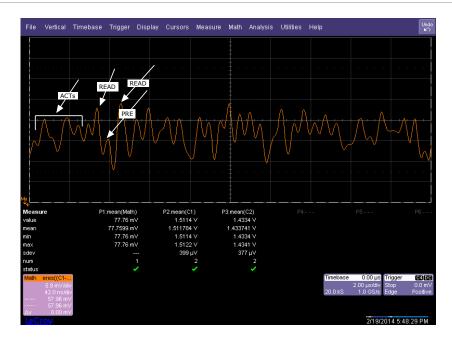

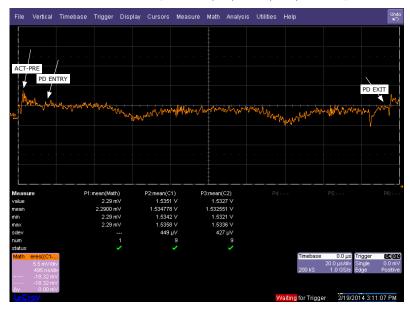

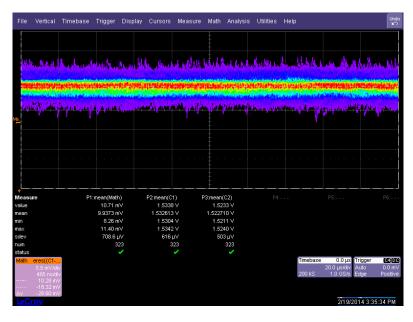

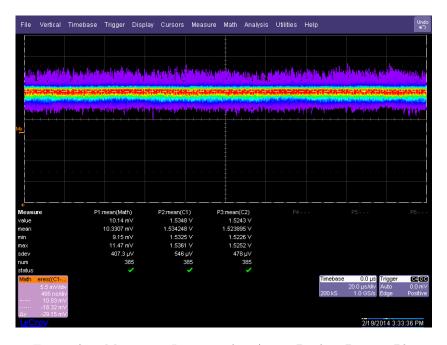

| 2.1  | Micron (Red) vs. DRAMPower (White) vs. Measurements (Orange)       | 23 |

| 2.2  | Basic Power Components in a Read Transaction of length nTL $$ . $$ | 25 |

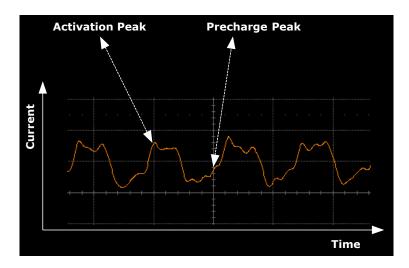

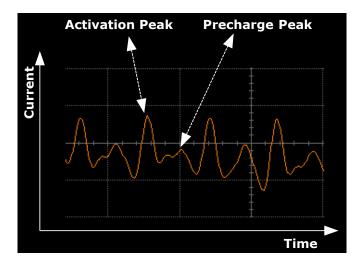

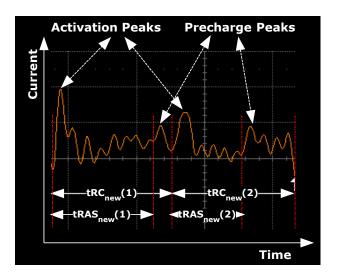

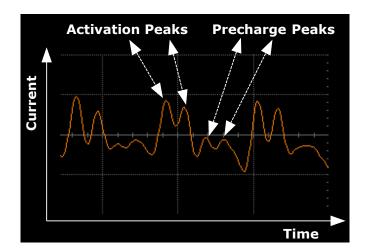

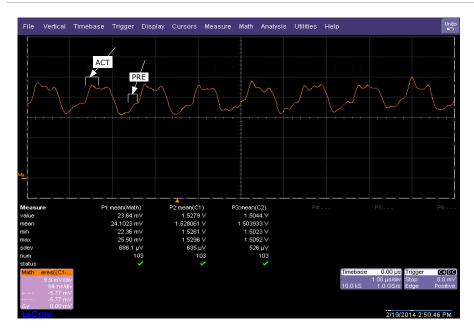

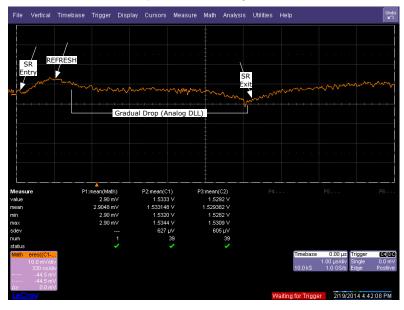

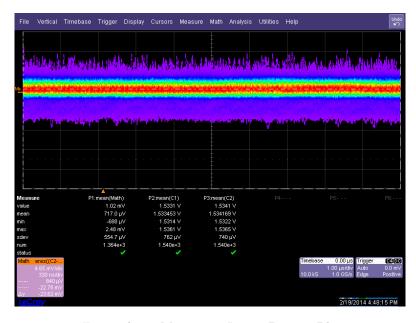

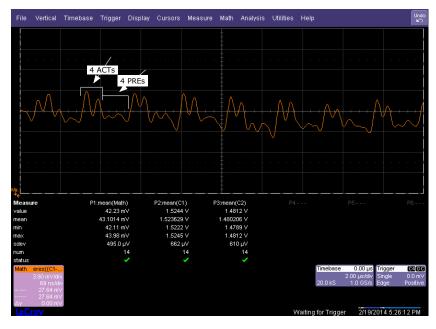

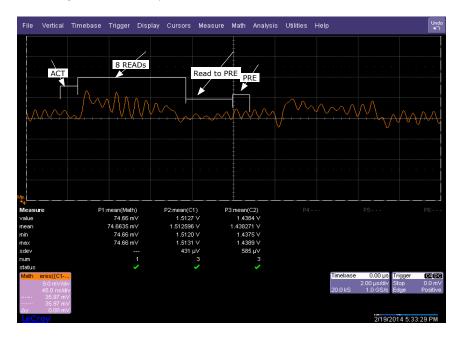

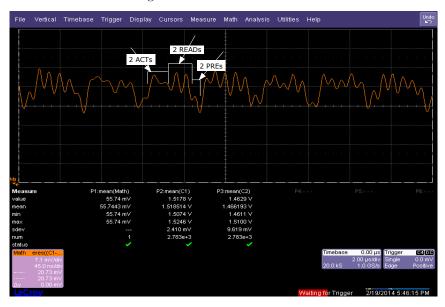

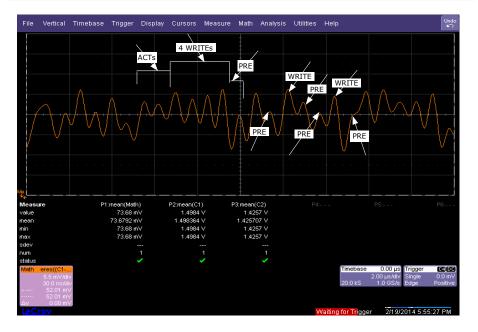

| 2.3  | ACT-PRE Measurement                                                | 26 |

| 2.4  | ACT-PRE Operation (Spaced Out)                                     | 27 |

| 2.5  | ACT-PRE Scaling                                                    | 28 |

| 2.6  | Two Bank Activation                                                | 29 |

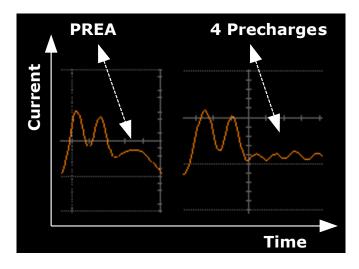

| 2.7  | PREA clarification                                                 | 29 |

| 2.8  | READ/WRITE clarification                                           | 30 |

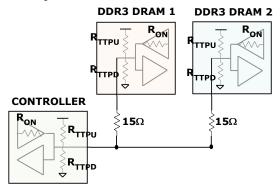

| 2.9  | I/O and Termination Clarification                                  | 31 |

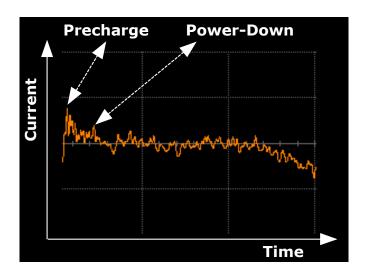

|      | Precharge Power-Down Transition                                    | 33 |

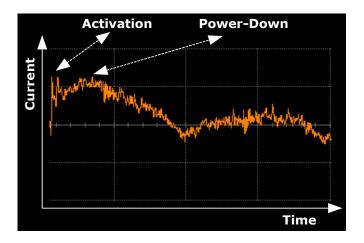

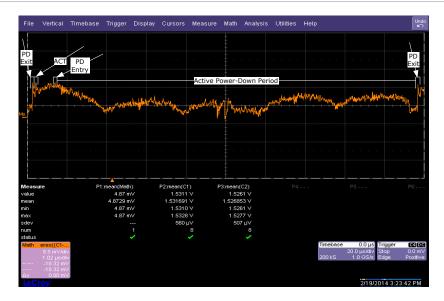

| 2.11 | Active Power-Down Transition                                       | 34 |

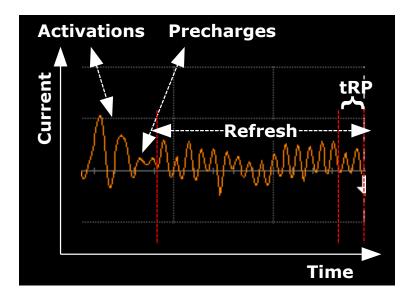

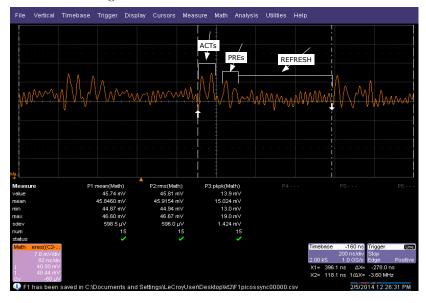

|      | Refresh Transition                                                 | 36 |

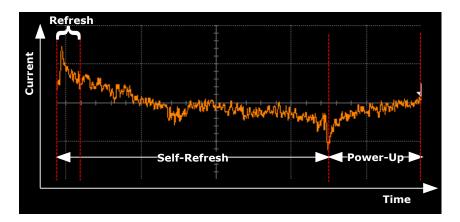

| 2.13 | Self-Refresh Clarification                                         | 37 |

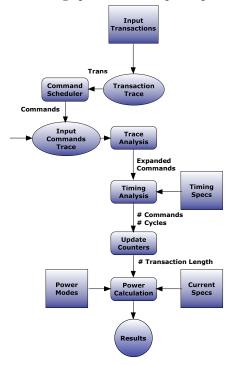

| 2.14 | Phases in DRAMPower Tool Flow                                      | 42 |

| 3.1  | DRAM Cross-Section Model                                           | 48 |

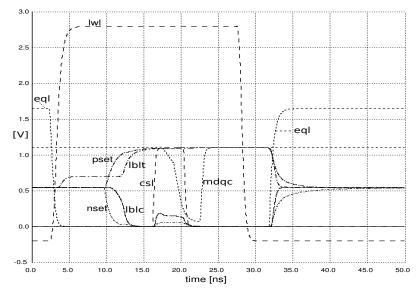

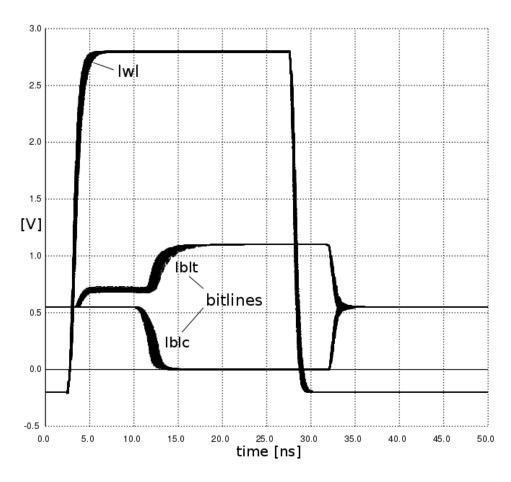

| 3.2  | ACT-RD-PRE behavior in DRAM Cross-Section                          | 50 |

| 3.3  | Variation Impact on Bitline and Wordline                           | 53 |

| 3.4  | Impact on Currents and Timing                                      | 55 |

| 3.5  | Functional Latency Vs. Current Consumption                         | 56 |

| 3.6  | Deriving Optimized DRAM Timings and Realistic Current Measures     | 65 |

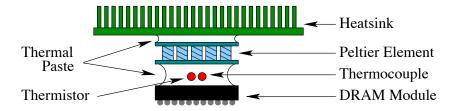

| 4.1  | Heating Setup                                                      | 69 |

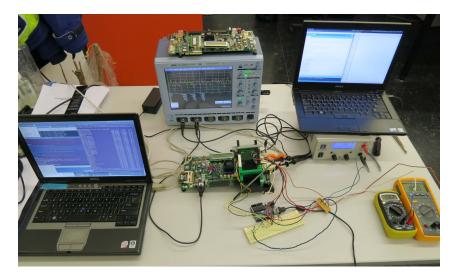

| 4.2  | Experimental Setup                                                 | 69 |

| 4.3  | Actual vs. Datasheet (DS) Timing Measures - Nominal Conditions     | 71 |

| 4.4  | Measuring $I_{DD0}$                                                | 75 |

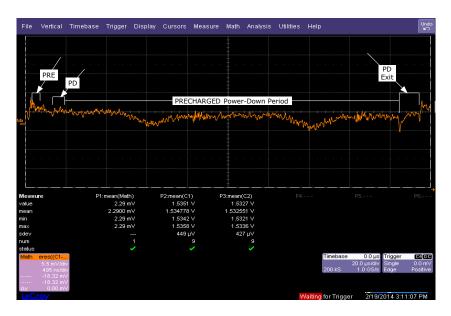

| 4.5 Measuring $I_{DD2P}$ after Precharging                                 |

|----------------------------------------------------------------------------|

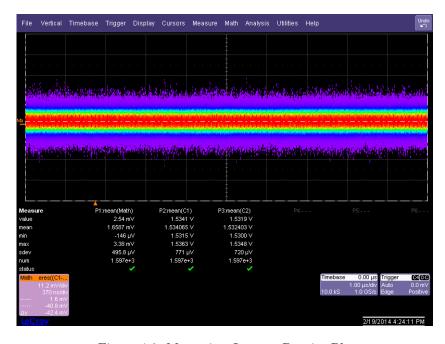

| 4.6 Measuring $I_{DD2P}$ - Density Plot                                    |

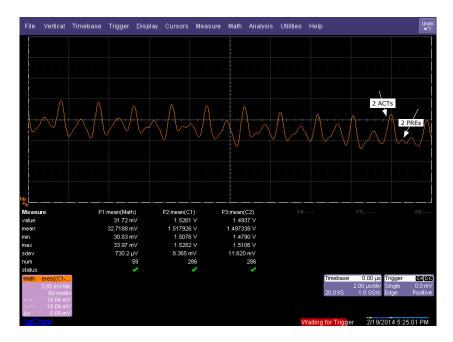

| 4.7 2 Banks - ACT-PRE                                                      |

| 4.8 8 Banks - ACT-PRE                                                      |

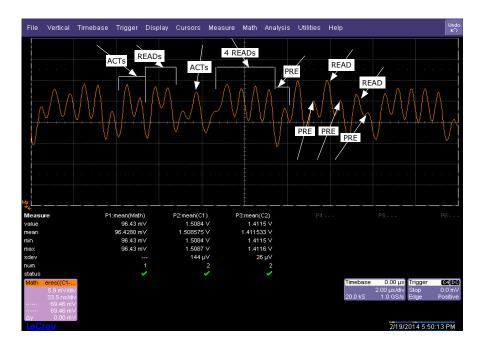

| 4.9 4 Reads - 1 Bank                                                       |

| 4.10 1 Read - 4 Banks                                                      |

| 4.11 ACT - PRE to Precharged Power-Down 85                                 |

| 4.12 ACT - PRE to Self-Refresh                                             |

| 4.13 Accuracy of DRAMPower & Micron Model using Measured $I_{DDs}$ . $$ 84 |

| 5.1 Memory Controller Overview                                             |

| 5.2 Latency-Rate Server                                                    |

| 5.3 Deriving Worst-Case Maximum Access Time Guarantee $(\Phi)$ 97          |

| 5.4 Snooping Point in Aggressive Power-Down                                |

| 5.5 Energy Savings vs. No Power-Down                                       |

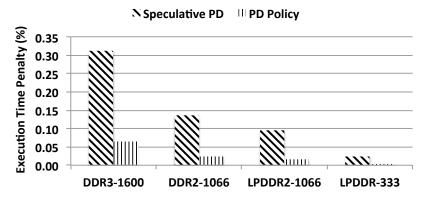

| 5.6 Power-Down vs. Speculative Execution Time Penalty 106                  |

| A.1 Measuring $I_{DD1R}$                                                   |

| A.2 Measuring $I_{DD1W}$                                                   |

| A.3 Measuring $I_{DD2N}$ after Precharging                                 |

| A.4 Measuring $I_{DD2N}$ - Density Plot                                    |

| A.5 Measuring $I_{DD3N}$ with 1 Active Bank                                |

| A.6 Measuring $I_{DD3N}$ with 1 Active Bank - Density Plot 127             |

| A.7 Measuring $I_{DD3N}$ with 8 Active Banks                               |

| A.8 Measuring $I_{DD3N}$ with 8 Active Banks - Density Plot 128            |

| A.9 Measuring $I_{DD3P}$                                                   |

| A.10 Measuring $I_{DD3P}$ - Density Plot                                   |

| A.11 Measuring $I_{DD4R}$                                                  |

| A.12 Measuring $I_{DD4W}$                                                  |

| A.13 Measuring $I_{DD5}$                                                   |

| A.14 Measuring $I_{DD6}$ with Precharging                                  |

| A.15 Measuring $I_{DD6}$ - Density Plot                                    |

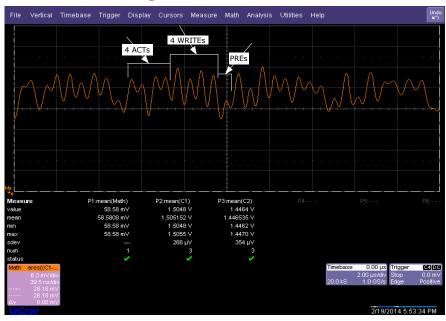

| A.16 4 Banks - ACT-PRE                                                     |

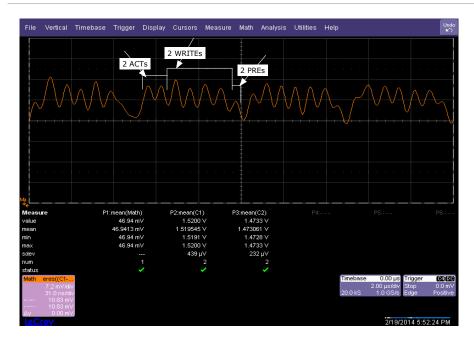

| A.17 8 Reads - 1 Bank                                                      |

| A.18 4 Writes - 1 Bank                                                     |

| A.19 8 Writes - 1 Bank                                                     |

| A.20 1 Read - 2 Banks                                                      |

| A.21 1 Read - 8 Banks                                                      |

| A.22 1 Write - 2 Banks                                                     |

| A.23 1 Write - 4 Banks                                                     |

| A.24 1 Write - 8 Banks                                                     |

| A.25 ACT to Active Power-Down                                              |

| A.26 ACT - PRE to Refresh                                                  |

### CHAPTER 1

### Introduction

Most modern battery-driven consumer electronics, including tablets, mobile phones, and wearable electronics, can be categorized as embedded systems. With each new generation and version of these devices, manufacturers continue to equip them with better computing, visualization and internet capabilities [15, 16], which often hurt their power consumption. Since battery capacities have not improved at the same rate as computing power [49], efficient design-time and run-time power management and minimization techniques are of highest importance in designing embedded systems.

To address these issues, embedded system designers rely on couple of features: (1) accurate power estimation of all system components and (2) efficient power optimization solutions that do not harm performance.

In this thesis, we propose solutions to address both of these two issues for one of the most important components in the system: DRAM memories. Modern embedded systems often include DRAMs [8,9], to optimize system's performance (for instance in display buffers to get better frame rate), but have an adverse effect on its power and energy consumption [2,19,20] (up to 25% increase [14]). To address this, we propose: (1) a high-precision DRAM power model called DRAMPower that uses realistic current measures as inputs and (2) a set of performance-neutral DRAM power-optimization strategies.

Using the DRAM power model, we identify critical DRAM operations and states that contribute significantly to DRAM power consumption and with the performance -neutral power-optimization strategies, we reduce their impact on overall power consumption.

### 1.1 Problem Statement

Although JEDEC [10] and DRAM vendors have continuously improved DRAM architectures [11–13] in terms of bandwidth and power efficiency, the incessantly increasing demand for higher memory performance (bandwidth) and capacity has

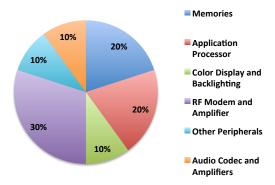

meant continued significance of DRAMs in overall system power consumption [19], even when idle [20,21]. With larger and faster DRAMs being incorporated with every new generation of mobile phones and tablets, DRAM power consumption in mobile devices is likely to match that of mobile processors [14]. Figure 1.1 depicts the ratios of power consumption of different components in a generic mobile platform as observed by Siemens and Infineon [14]. As depicted, memories are seen to consume as much power as an application processor.

Figure 1.1: Mobile Platform Power Consumption (Adapted from [14])

As expected, DRAMs have become a crucial target for power optimization both in the industry [14,19,22–24] and academia [25–37], with solutions ranging from system-level power management down to the circuit-level optimizations, targeting both active and idle power consumption. Refining the earlier statement, the two key factors defining energy-efficient use of DRAMs in embedded systems are: (1) accurate power/energy consumption estimation of DRAMs and (2) efficient power/energy optimization of DRAMs. Together these form the primary focus of this thesis work. Towards this, we propose: (1) a high-precision power model of DRAMs (DRAMPower) and (2) a set of performance-neutral DRAM power optimization strategies.

Before discussing the problems and the proposed solutions in detail, we briefly describe the basics of the DRAM architecture, organization and operations.

### 1.1.1 Background: Generic DRAM Architecture

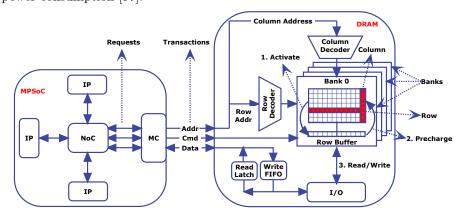

DRAMs are independent memory devices which for instance, can be used as shared storage between several IPs in a System-on-Chip (SoC) through a DRAM memory controller. DRAMs have a defined architecture, interface, and a set of operating modes. Each of the IPs in an SoC can read or write data into DRAMs by sending read or write requests to the DRAM memory controller, which translates these requests into memory transactions with a set of DRAM commands, data and target memory address. Below, we describe basic DRAM organization, commands and operations. Internally, DRAMs are organized in banks of rows and columns,

as shown in Figure 1.2. A bank includes memory elements (cells) arranged in a matrix structure and a row buffer (with sense amplifiers) to store contents of an active memory row. The banks in a DRAM operate in a parallel and pipelined fashion. However, since they all share a single I/O and command bus, only one bank can perform an I/O operation at a particular instance in time and only one DRAM command may be issued to the memory per clock cycle.

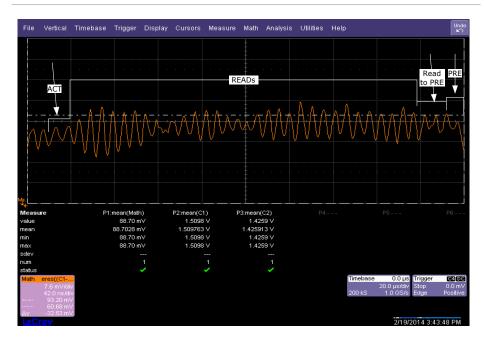

To read contents from the memory, an Activate command (#1 in Figure 1.2) is first issued by the memory controller (MC in the figure) to the DRAM, which opens the requested row and copies data from the DRAM cells in the corresponding row into the row buffer. Then, any number of Read or Write commands (#3 in Figure 1.2) can be issued to read out or write into specific columns in the row buffer. Subsequently, a Precharge command (#2 in Figure 1.2) is issued and the contents of the row buffer are stored back into the corresponding memory row. Reads and writes can also be issued with an auto-precharge flag to automatically precharge as soon as the request completes. The number of read/write commands in a transaction is called Burst Count (BC), and the amount of data read out or written into by each command is given by the Burst Length (BL) (e.g. 8 words for DDR3), where each word is defined by the data width of a given device. Furthermore, a memory transaction may also be interleaving over more than one bank, given by the degree of Bank Interleaving (BI). The product of BL, BC and BI parameters determines the data access granularity with which the memory controller accesses the memory and has a large impact on both performance and power consumption [97].

Figure 1.2: DRAM Organization in the System context

If any row is active, the memory is said to be in the *active* state, else it is in the *precharged* state. Switching between a read and a write command, or vice versa, takes a few clock cycles to allow the data bus to switch the I/O direction. Further, to retain data in the memory, all rows in the DRAM need to be refreshed at regular intervals, which is done by issuing a *Refresh* command. Internally, a refresh is a set of activates and precharges to the same row in different banks.

In addition to issuing these commands, it is also possible to transition to power-down state by disabling the clock at run time to reduce power consumption, if the memory is idle. However, the memory must be powered up whenever a refresh command is issued. It is also possible to retain the memory contents without refreshing by employing the Self-Refresh power-saving state, which refreshes the memory at significantly lower power consumption than explicit refreshes.

For proper DRAM operation, the commands discussed above must be issued by the memory controller to the DRAM in a specific order, while satisfying the associated minimal timing constraints (for DDR2 [102] and for DDR3 [103]). For instance, between issuing an Activate command and a Read command, the minimum timing constraint of nRCD cycles should be respected. Some of these constraints that need to be satisfied when issuing commands to a DDR3-800 memory [99] are specified in Table 1.1:

| Table 1.1: Micron DDR5-800 1 ming Constraints |                                                   |               |  |  |  |  |

|-----------------------------------------------|---------------------------------------------------|---------------|--|--|--|--|

| Constraint                                    | Description (Minimum Time between)                | Time (cycles) |  |  |  |  |

| nRC                                           | Two ACTs to the same bank                         | 20            |  |  |  |  |

| nRAS                                          | An ACT and a PRE to the same bank                 | 15            |  |  |  |  |

| nRCD                                          | An ACT and a RD/WR to the same bank               | 5             |  |  |  |  |

| nRP                                           | A PRE and an ACT to the same bank                 | 5             |  |  |  |  |

| nWTR                                          | A RD and a WR to the same bank and row            | 4             |  |  |  |  |

| nRTP                                          | ARD and a PRE to the same bank                    |               |  |  |  |  |

| nCCD                                          | nCCD Two consecutive RDs or WRs                   |               |  |  |  |  |

| nRRD                                          | nRRD Two ACTs to different banks                  |               |  |  |  |  |

| nCL                                           | nCL Two RDs to the same bank                      |               |  |  |  |  |

| nWR                                           | <i>nWR</i> A RD and a WR to the same bank and row |               |  |  |  |  |

| nFAW                                          | nFAW A RD and a WR to the same bank and row       |               |  |  |  |  |

| nRFC                                          | nRFC A REF and an ACT                             |               |  |  |  |  |

Table 1.1: Micron DDR3-800 Timing Constraints

These timing constraints specified by the datasheets are the minimal timings between two commands. However, most DRAM controllers do not always issue commands as soon as these minimal constraints are satisfied. Instead, they schedule commands based on different command-scheduling and row-buffer management policies, where the actual duration between any two issued commands may be greater than the minimum. For instance, the memory controller may employ an open-page policy [50] and delay issuing a precharge to a bank until there is a row-miss on the subsequent access to that bank.

In general, memory controllers employ the open-page policy or the close-page policy [50] based on the assumed presence or absence of data locality in the target application. The former policy keeps the row buffer active to reduce the access time for subsequent accesses to the same memory row in the same bank by not issuing a *Precharge* command at the end of a transaction. The latter policy immediately closes the active row buffer at the end of every bank access with a *Precharge* command, for faster accesses to any other location in the memory in the subsequent transaction.

### 1.1.2 Problem I: DRAM Power Modeling

This section addresses the first of the two problems to be addressed in this thesis: accurate power/energy estimation of DRAMs.

To enable efficient power management, system designers rely on power consumption information provided by DRAM vendors and/or power models developed by DRAM vendors. These power measures/models are required to address three important issues: (1) to design efficient power supplies for DRAMs, (2) to estimate power/energy usage by the DRAMs used in a system and (3) to derive design-time and run-time power optimization policies to reduce DRAM power consumption. The reason for employing these measures/models to address these three issues is their accuracy. In this work, the accuracy of a given power model is evaluated by comparing its power/energy estimates against real power measurements from a given DRAM device for different DRAM operations.

JEDEC requires all DRAM vendors to furnish a set of standardized current measures in DRAM device datasheets corresponding to different combinations of standard memory transactions, to obtain approximate power consumption estimates. Although these current measures are adequate to enable designing of suitable power supplies for DRAMs (Issue 1), they are insufficient for accurate power/energy consumption estimation (Issue 2) and efficient DRAM power management (Issue 3), since they do not represent power consumption of individual DRAM operations.

To resolve this issue, DRAM vendors including Micron and Samsung supplement these datasheet current measures with high-level power models [17,18] that include equations to break the datasheet current measures down to measures corresponding to individual DRAM transactions and to obtain a more fine-grained account of power consumption in DRAMs. Although these models provide better details of DRAM power consumption compared to bare datasheet current measures, they have been shown to be *imprecise in their modeling* of the different individual DRAM operations, state transitions and power-saving modes [38–40]. This highlights *the need for high precision modeling*.

Besides the issue of precision in power modeling, the input datasheet measures used by these power models reflect worst-case current measures for all DRAM devices manufactured with the same configuration (frequency, speed-bin and revision) by a vendor [45, 98–100]. These measures include substantial margins in current measures to address the impact of design-time process-variations and run-time variations in operating temperature and power-supply noise [89]. As a result, the datasheet current measures can differ significantly from the actual observed current measures, when measured on any given DRAM device. Hence, using datasheet current measures reduces the accuracy of their power and energy estimates for a given DRAM device. These high-level models employ basic algebraic functions to model power consumption, hence, the worse the accuracy of the input, the worse the accuracy of the output.

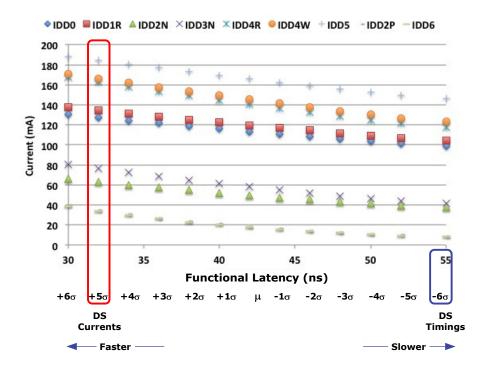

To highlight the significant difference between the worst-case datasheet current

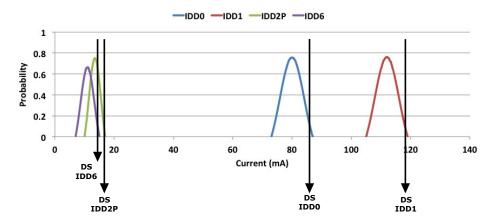

measures and the nominal current measures of the manufactured lot, we present the average data ( $\mu$ ) and the standard deviation ( $\sigma$ ) in Table 1.2 that shows the impact of process variations on a few DRAM currents [103] as observed by a memory vendor in the production analysis data of a lot of 11,000 DDR3 1Gb memories with 533 MHz frequency and x8 width, manufactured at 70nm.

| Current    | Nominal (Average) | $\sigma\%$ | Datasheet (Worst Case) |

|------------|-------------------|------------|------------------------|

| Type       | $\mu$ $(mA)$      |            | $\mu + 5\sigma(mA)$    |

| $I_{DD0}$  | 79.1              | 1.4        | 84.7                   |

| $I_{DD1}$  | 111.1             | 1.2        | 117.8                  |

| $I_{DD2P}$ | 13.1              | 7.1        | 17.7                   |

| $I_{DD6}$  | 9.2               | 12         | 14.8                   |

Table 1.2: Distribution of Current Consumption

This distribution data is represented as probability density function of the different currents in Figure 1.3. In the figure, the reported datasheet (DS) measures are indicated for each current measure. These datasheet measures reflect worst-case case measures for the all devices that are sold from a particular DRAM generation and revision. Such worst-case measures are used to improve the yield of the manufactured devices. The devices that have worse current measures than the datasheet measures are generally rejected from the lot. These correspond to the device in the  $+6\sigma$  range.

Figure 1.3: Probability Density Function of Current Measures

This current distribution data shows very large difference between the datasheet (DS) current measures and the nominal ( $\mu$ ) current values (by a factor of  $5\sigma$ ), up to 36% and 60% for the low-power modes (power-down:  $I_{DD2P}$  and self-refresh:  $I_{DD6}$ ) and up to 7% for the activate-precharge ( $I_{DD1}$ ) current and 6% for the activate-read-precharge ( $I_{DD1}$ ) current [103]. With DRAM memories now being

manufactured at technologies below 50nm, these current variations are only expected to worsen, and so is the accuracy of the power models employing these datasheet measures.

To address this issue of worst-case current measures, DRAM vendor RAM-BUS [22], Hewlett Packard Research Labs [101], and academic contributors such Weis et al. [46, 47], Keeth et al. [48], have proposed employing detailed circuit-level models of DRAMs to obtain nominal power and energy consumption estimates. By employing such circuit-level models, not only is it possible to (1) model DRAM operations and state transitions more precisely than the high-level current measures-based models, but also to (2) derive more accurate power estimates by using nominal (average-case) current measures in place of the worst-case datasheet measures.

However, there are a few issues in employing these circuit-level models. Firstly, the underlying DRAM architectures employed by these models may not accurately reflect the design choices and optimizations across different DRAM vendors. Furthermore, to make sure the required modifications reflect architectural differences, one needs to have a detailed understanding of the circuit-level behavior of DRAMs, making it very inconvenient for system designers to employ these models. To add to this issue, DRAM vendors do not provide extensive circuit-level details of their DRAM architectures and designs, which makes it extremely difficult to adapt these models to reflect real designs. Finally, although the nominal current measures may be closer to real measurements (for most devices) than the worst-case measures, they only serve as approximate indicative measurements and can still differ from the actual current measures of a given DRAM device by a large extent. Also, using nominal measures only covers 50% of the DRAM devices in the lot.

Considering the difficulties in employing and adapting the circuit-level models, the only feasible alternative is to *employ current measures-based power models* similar to those by Micron and Samsung, but with improved precision in their modeling of the different DRAM transactions, along with realistic or 'better than worst-case' current values for a device configuration, instead of the worst-case measures.

### 1.1.3 Problem II: Run-Time DRAM Power Optimization

This section addresses the second of the two problems to be addressed in this thesis: performance-neutral power optimization of DRAMs.

Most modern embedded systems employ DRAMs as a high-bandwidth low-cost memory solution to store active application code and data to enhance system performance. However, DRAMs also significantly impact system power and energy consumption (increase of up to 25% in mobile phones) [14, 19], even when they are idle [20, 21] and are prime candidates for efficient run-time power management and optimization to reduce their energy consumption.

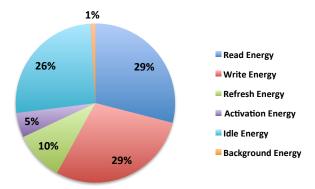

Figure 1.4 depicts DRAM energy consumption components when the DRAM is idle 50% of the time and switching between reads and writes (using a closed-

page policy) interspersed with the occasional refresh, for 1Gb DDR3-800 modules from Micron. As can be noticed from the pie chart, idle energy (energy consumed in the precharged idle standby state) contributes to more than 25% of the total energy consumption at 50% idleness, highlighting the need for optimization of power consumption during idle periods.

Figure 1.4: Energy Consumption of DRAM Operations

Besides the design-time circuit-level and architectural optimizations for power and energy-efficient DRAM designs employed by JEDEC and DRAM vendors, run-time high-level power optimization solutions are required for efficient system designs. Towards this, innumerable propositions have been made [14, 19, 22–37] to optimize DRAM power consumption, obtaining different degrees of power reduction, often with a corresponding negative impact on performance. With the ever-increasing demand for higher memory bandwidth, employing power optimization strategies that trade off performance for power becomes counter-productive. To optimize DRAM power consumption, two primary avenues are explored: (1) reducing active power by optimizing power consumption of DRAM accesses and refreshes and, (2) reducing standby power by optimizing power consumption when the memory is idle.

To reduce active power consumption, general approaches target: (1) minimizing row-buffer misses and (2) reducing read-write switches. The main goal of these approaches is to improve the average DRAM performance by reducing the overall number of DRAM operations and as a byproduct, reduce the DRAM energy consumption. However, these optimizations can also impact worst-case latencies of individual DRAM transactions, due to: (1) inefficient handling of open rows and (2) re-ordering of transactions.

To reduce standby power consumption, DRAMs have the option of using either (1) power-down or (2) self-refresh modes to power-off the device [103] or (3) frequency scaling to minimize idleness. Unfortunately, the powering-off mechanisms, if speculatively used, may impact performance due to their power-up latencies [103]. Also frequency scaling may impact the latency of individual DRAM operations, due to the slowing down of the memory.

This calls for DRAM power optimization strategies that can efficiently employ any of these approaches, while avoiding or hiding any resulting performance loss. Such guaranteed performance is often required by applications with strict performance requirements (such as high-performance real-time systems), which demand worst-case guarantees from every component in the embedded system and cannot tolerate any impact on the same.

### 1.2 Proposed Solutions

To address both the accurate DRAM power modeling and performance-neutral DRAM power optimization problems, we propose the following:

- 1. DRAM power modeling There are two issues to address here: (a) Improved precision in power modeling and (b) Employing *realistic* or *better than worst-case* current values as inputs.

- To address the first issue, we propose high-level cycle-accurate high-precision power model of DRAMs. To address the second issue, we propose to adapt a circuit-level SPICE model to reflect the architecture of a particular DRAM configuration and:

- I. Derive better than worst-case current measures that are applicable for a majority of DRAM devices in a particular generation ( $\geq 97\%$ ), in place of datasheet measures, which are extremely pessimistic. These 'better than worst-case' measures are obtained by introducing device level variations in the circuit-level DRAM model and performing Monte-Carlo analysis to derive  $\pm 6\sigma$  distribution of current measures (that reflect impact of process variations). From this distribution, we select the current measures applicable to  $\geq 97\%$  of the devices ( $+3\sigma$  data point).

- II. Combine it with a post-manufacturing DRAM power and performance characterization methodology to determine more *realistic* current measures for a particular given DRAM device, which may lie anywhere in the  $\pm 6\sigma$  distribution of current measures.

- 2. DRAM power optimization We propose a couple of performance-neutral DRAM power-down strategies with a run-time power management policy that reduce memory power consumption, while preserving the original worstcase performance guarantees.

### 1.2.1 Improved DRAM Power Modeling and Estimation

When it comes to DRAM power modeling and estimation, the accuracy of power estimation can improve with: (1) An increase in the level of detail (precision) employed in modeling the power consumption of a particular DRAM operation (like activation, precharge, refresh, power-down etc.) and (2) A higher degree

of accuracy of the inputs employed by the models (such as its current measures, design specifications etc.).

In this work, we establish the accuracy of a given power model by comparing its power/energy estimates against real power measurements from a given DRAM device, thereby evaluating both the power model's detail of modeling different DRAM operations/transactions and its assumptions on the DRAM current measures it uses as inputs.

In this context, we first establish a generic metric to evaluate the accuracy of a DRAM power model. Let  $M_{(i,j)}$  denote a Power Model i and its modeling of operation j and  $I_{(i,j)}$  denote its current inputs for the particular operation (e.g. worst-case or nominal currents). The resultant output can be derived as  $O_{(i,j)}$ , as shown in Equation (1.1). Accordingly, the power model's accuracy for the particular operation  $A_{(i,j)}$  can be given by Equation (1.2), where  $O_{(ref,j)}$  gives the reference power consumption estimate obtained from direct power measurements on a particular DRAM device for the particular operation j. The aggregate average of this accuracy measure over all DRAM operations (J), indicates the overall accuracy of the power model as given by Equation (1.3), where J is the set of all important DRAM operations. In general, since worst-case currents represent the entire lot of DRAM devices of a particular generation and configuration and nominal currents represent 50% of the devices of the lot, the accuracy of models using these current measures is likely to be higher for the proportion of population they represent.

$$O_{(i,j)} = M_{(i,j)}(I_{(i,j)})$$

(1.1)

$$A_{(i,j)} = 1 - |1 - (O_{(i,j)}/O_{(ref,j)})|$$

(1.2)

$$A_{(i)} = \left(\sum_{j \in J} A_{(i,j)}\right) / \mid J \mid \tag{1.3}$$

As stated before, the state-of-the-art transaction-level models based on current measures such as those from Micron, are imprecise in their modeling of different DRAM operations and state transitions and employ worst-case current measures as inputs, whereas the circuit-level power models [22, 47, 48, 101] may not accurately reflect the architectural distinctions between different DRAM generations, across DRAM vendors and their design optimizations. As a result, both these models are expected to fair poorly in their accuracy metric.

Considering the issues with employing circuit-level models, the only feasible alternative is to employ high-level power models similar to those by Micron and Samsung, which are based on JEDEC-specified currents that reflect individual vendor's architectural differences, but with (1) improved precision in modeling of the different DRAM operations  $(M_{(i,j)})$  and (2) use of 'better than worst-case' and 'realistic' current measures  $(I_{(i,j)})$  instead of the worst-case datasheet current measures, to obtain more accurate power consumption estimates  $(O_{(i,j)})$ .

To improve the modeling precision, we propose a *high-level power model of DRAMs* referred to as *DRAMPower*, which models the power consumption of different DRAM operations, state transitions and power-saving modes with high precision and analyzes memory command timings at cycle-accurate level, resulting in more accurate power estimates compared to transaction-level models.

To address the issue of assumptions on input currents, we propose to adapt a circuit-level model to reflect the architectural details of a given DRAM configuration and:

- (I) Derive better than worst-case current measures that are applicable to > 97% of the devices with the particular configuration ( $+3\sigma$  of the population).

- (II) Combine it with a generic post-manufacturing DRAM power and performance characterization methodology that identifies *realistic* current estimates for any given DRAM device of any configuration.

Both the solutions for power modeling and assumptions on current inputs, improve the accuracy of the power and energy estimates of DRAMPower. We further employ the actual measured current values for a given DRAM device as inputs to DRAMPower, and show a very high degree of accuracy in its power estimates over different DRAM operations, in comparison to real measurements from hardware.

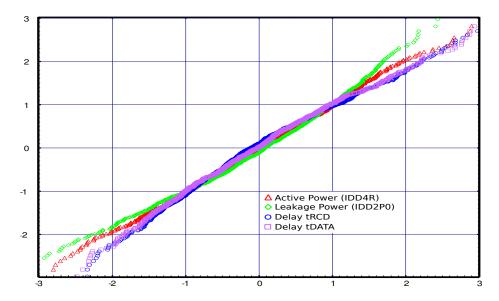

In Table 1.3, we depict the modeling detail and current inputs employed by the state-of-the-art power models, viz., Micron (M0) and Weis et al., (M1), as we improve DRAMPower's (M2) accuracy by introducing high-precision cycle-accurate modeling and use of 'better than worst-case' current measures (I2 [+3 $\sigma$ ]) in place of Datasheet current measures (I0 [+5 $\sigma$ ]) and nominal current measures (I1 [ $\mu$ ]). These comparisons are valid for >97% of the DRAM devices of a given configuration.

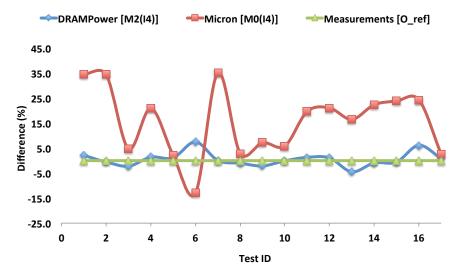

Additionally, we also propose a post-manufacturing power and performance characterization mechanism to obtain more realistic current measures (I3) for a given DRAM device. These realistic current measures are identified at the peak performance of the given device, and are much closer to the real current measures of the device, if it were to be operated at its peak performance. To fairly assess the accuracy of the high-level power models (Micron and DRAMPower), we also employ measured current  $(I_{DD})$  values (I4) for a given DRAM device as inputs to both these models (M0/I4 and M2/I4, respectively), and then compare their power estimates over different DRAM operations to real measurements from hardware  $(O_{ref})$ , thereby performing a fair comparison between the three sets of power estimates. These comparisons are also shown in Table 1.3.

In Figure 1.5, we present an overview of the different levels of detail and current measures employed by different DRAM power models (including DRAM-Power) and the relative degree of accuracy of their power and energy consumption estimates compared to real power measurements from hardware on a 512MB DDR3-800 DIMM using 1Gb-Micron DDR3-800 devices. As shown in the figure, the accuracy of DRAMPower improves by employing 'better than worst-case' current measures ( $I_{DDs}$ ) [53] in place of the worst-case datasheet current measures,

|                   |                |                  | Better than    |                |

|-------------------|----------------|------------------|----------------|----------------|

|                   | Datasheet      | Nominal          | Worst-Case     | Measured       |

|                   | $I_{DDs}$ (I0) | $I_{DDs}$ (I1)   | $I_{DDs}$ (I2) | $I_{DDs}$ (I4) |

|                   | (Chapter 2)    | (Chapter 3)      | (Chapter 3)    | (Chapter 4)    |

| Trans-Level(M0)   | Micron [17]    |                  |                | Micron         |

| Circuit-Level(M1) |                | Weis et al. [46] |                |                |

| Cycle-Acc.(M2)    | DRAMPower      |                  | DRAMPower      | DRAMPower      |

| Applicable        |                |                  |                |                |

| Population %      | 100%           | 50%              | 97%            | 1 device       |

| Standard          |                |                  |                |                |

| Deviation         | $+5\sigma$     | $\mu$            | $+3\sigma$     | $-5\sigma$     |

Table 1.3: Accuracy of State-of-the-art power models vs. DRAMPower

to achieve power estimation accuracy closer to that of the circuit-level models. It further improves the accuracy of its power estimation by employing nominal (I1) and realistic currents (I3) which are closer to the real measures from a given device. Finally, when employing measured currents (I4), it achieves around 97% accuracy compared to power measures from hardware over different DRAM operations. Micron's model also improves its accuracy when employing I4 to achieve around 82% accuracy.

In Figure 1.6, we present an overview of the DRAM power models (M0 to M2) and the current measures they employ (I0 to I4) and their relative degree of accuracy in terms of power estimates compared to real measurements from hardware ( $O_{ref}$ ). As can be noticed in the figure, DRAMPower (M2) using 'better than worst-case' current measures (I2) is shown to be more accurate compared to existing power model/current measure combinations (M0(I0) and M1(I1)) for >97% of the devices. For a particular DRAM device under consideration, DRAMPower using realistic current measures (I3) and measured current values (I4) improves in terms of power estimation accuracy and still evaluates better than the Micron model.

### 1.2.2 Performance-Neutral Power Optimization of DRAMs

DRAM power management mechanisms target two power modes: active and idle, since both are equally important to optimize. Active power management, solutions range from exploiting locality to re-ordering transactions, and reducing refreshes, all of which primarily target minimizing the number of DRAM operations and as a consequence reduce the overall energy consumption. Although these solutions improve performance and reduce power consumption on average, they can also impact worst-case latencies of individual DRAM transactions, since: (1) the memory rows are kept open for long, and (2) re-ordering of transactions can delay individual transactions.

Conservative strategies, such as the one proposed by Goossens et al. in [96],

Figure 1.5: DRAM Power Models vs. Accuracy

Figure 1.6: Accuracy of DRAM Power Models and Current Measures

can be employed to optimize average-case performance without affecting worst-case guarantees, while reducing active energy consumption. Such worst-case performance guarantees are required by applications with high-performance and real-time performance requirements that must not be violated. Additionally, as a result of reducing overall DRAM accesses, the active power optimization policies tend to increase DRAM idleness and these idle periods must also be optimized for reduced power consumption.

When it comes to idle power management, most solutions employ either the power-down or the self-refresh power saving modes to power off the device when it is idle [24,55–58] or scale down the DRAM frequency to minimize idleness [23,59–61]. The down-side to using these power saving modes is that they can negatively impact both the average-case performance and worst-case latencies of transactions due to their power-up latencies, if speculatively used. Frequency scaling also incurs a performance penalty due to overhead involved in the process and hence, also can affect both average-case and worst-case performance.

In comparison to active power management, idle power optimization poses a bigger challenge, since not only can the speculative use of power saving modes reduce system performance, but can also increase the overall energy consumption. Hence, there is a need to derive idle power optimization strategies that can efficiently employ any of the power saving modes to reduce idle power consumption without affecting the original worst-case performance guarantees, while avoiding or minimizing any impact on average-case performance.

Considering the challenges in reducing idle power consumption in DRAMs, with the aim of deriving performance-neutral run-time power optimization strategies, we propose: (1) a conservative and an aggressive DRAM power-down strategy and (2) a power management policy for DRAM memory controllers that employs one of these two strategies at run time, preserving the original worst-case performance guarantees while achieving significant power savings.

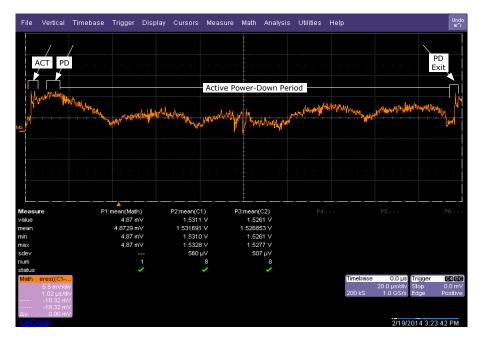

The conservative and aggressive power-down strategies exploit the idle memory service cycles identified by real-time DRAM arbiters like Round-Robin and TDM, to initiate use of the power-down mode and differ primarily in their decision to power-up the memory.

While the conservative strategy acts cautiously and powers up the DRAM by the end of every arbiter service cycle (time period required by the DRAM to serve a request), the aggressive strategy actively merges contiguous idle service cycles to keep the memory in the powered-down state for longer continuous periods, as depicted in Figure 1.7. It does so by snooping the arbiter/bus at the front-end of the memory controller to look ahead for upcoming requests to the memory before deciding to power-up. It must be noted that the aggressive strategy, as a result of the snooping, also manages to power-up the memory in time for the next request to be served without affecting the requester's (memory client) original worst-case memory performance (latency and bandwidth) guarantees.

While the conservative strategy avoids any latency penalties, the aggressive policy efficiently bounds and hides the penalties within the original guaranteed

1.3. Contributions 15

Figure 1.7: Conservative vs. Aggressive Power-Down Strategies

latency, thereby avoiding any impact on the worst-case guaranteed performance. However, the aggressive strategy cannot always be applied for all use-cases and does marginally impact the average-case performance, which the conservative strategy avoids. To assure that both these strategies are used correctly without impacting the worst-case performance guarantees, we also propose a power management policy for the memory controller that evaluates both these power-down strategies for their applicability and potential for energy savings, for a given system use case, based on different memory access parameters such as access granularity, page policy and memory service cycle durations and applicable power-down modes.

This power management policy assures that the power-down strategies do not violate the original DRAM performance guarantees. For instance, for a given use case, if the power-up penalty of the aggressive policy cannot be hidden within the original latency bounds, it chooses to employ conservative power-down, ensuring no violation of the original performance guarantees. Thus, together, both the power management policy and the two power-down strategies are worst-case performance-neutral.

Both the power-down strategies and the power management policy can be employed together with any of the real-time memory controllers presented in [62–67]. Hence, by employing the proposed performance-neutral power-down strategies with the run-time power management policy, the memory controller can effectively and efficiently power-down the DRAM memory when it is idle, without impacting the original DRAM worst-case performance guarantees.

#### 1.3 Contributions

As highlighted in the previous sections, the goal of this thesis work is two-fold. (1) To derive accurate DRAM power and energy consumption estimates. (2) To derive efficient DRAM power optimization solutions without trading off worst-case performance for lower power consumption.

Towards this, we propose two major solutions: (1) A high-level cycle-accurate high precision DRAM power model that uses better than worst-case or realistic current measures to achieve accurate power and energy consumption estimates. (2) A run-time power management policy and two DRAM power-down strategies to optimize DRAM idle power consumption without affecting its worst-case performance guarantees. There are five significant contributions of this thesis:

#### 1. High-Precision DRAM Power Modeling

We propose a high-level cycle-accurate DRAM power model (DRAMPower) that enables high-precision power consumption modeling of different DRAM operations, state-transitions and power-saving modes. Towards this, we employ cycle-level DRAM command information, analyze the actual timings between the commands and accurately account for the power consumed during memory state-transitions (Chapter 2). We identify the differences in our modeling approach to existing power models based on current measures.

#### 2. Variation-Aware DRAM Power Estimation

To further improve the accuracy of DRAMPower's power/energy estimates, we derive better than worst-case measures for the JEDEC current metrics instead of vendor-provided worst-case measures from device datasheets. Towards this, we modify an NGSPICE-based circuit-level DRAM architecture and power model to accommodate the effects of design-time and run-time variations and derive a distribution of current measures (Chapter 3) applicable to all DRAM devices with any given configuration (capacity, data-width and frequency). From these measures we derive better than worst-case current estimates applicable to a majority (>97%) of the manufactured devices with that configuration (+3 $\sigma$  values in the distribution).

We then propose a generic post-manufacturing power characterization methodology for DRAMs to derive *realistic* current estimates for a given DRAM device. To do so, we assess a DRAM's actual performance characteristics and identify the equivalent impact on power consumption. When employing this methodology, we empirically determine the actual impact of manufacturing process-variations for a given DRAM device, thereby identifying the excess margins for this device, in the datasheet current measures (Chapter 3). As a consequence of this effort, we also identify the best-case performance metrics for a given DRAM device, enabling its optimized usage, both in terms of performance and power consumption.

#### 3. Open-Source DRAMPower Tool

The DRAMPower model has been released as an open source DRAM power and energy estimation tool at www.drampower.info [68] for fast and accurate DRAM power and energy estimation for DDR2/3/4, LPDDR/2/3 and Wide IO DRAM memories based on JEDEC standards.

1.4. Contributions

The tool can be employed at two levels of abstraction: (1) Command-level and (2) Transaction-level. To facilitate use of transaction-level traces, DRAMPower includes an optional DRAM command scheduler (developed by Yonghui Li at TU Eindhoven [132]), which dynamically schedules and logs DRAM commands, corresponding to the incoming memory transactions, as if it was a regular memory controller. It assumes a closed-page policy, employs FCFS scheduling across transactions and uses ASAP scheduling for DRAM commands. The tool supports all basic DRAM memory commands including read, write, refresh, activate and precharge, besides the power-down and self-refresh modes.

#### 4. Validating DRAMPower

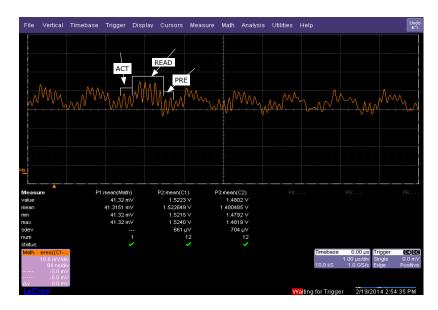

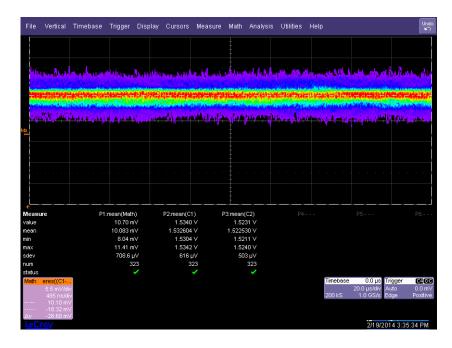

We validate the DRAMPower model against power measurements from real hardware (for a DDR3 DIMM) and compare its power estimates against those of Micron's power model [17]. Towards this, we employ measured current values from a DDR3 DIMM as inputs to DRAMPower and Micron's model. We determine these measures by implementing the standardized JEDEC current measurement test loops and measuring voltage drop across a shunt resistor. We then implement several test cases covering different DRAM operations, and state-transitions, and compare the power estimates of DRAMPower against those of the Micron model and the actual measurements from hardware (Chapter 4).

With these experiments, we highlight the significance of high-precision modeling in Chapter 2 by comparing DRAMPower against Micron's model.

#### 5. Performance-Neutral DRAM Power Optimization

We propose two DRAM power-optimization strategies to power-down the DRAM when it is not in use, while making sure that the worst-case performance guarantees of the DRAM memory are not affected. To do so, we employ a performance-neutral run-time power management policy that ensures that both these strategies are used correctly and efficiently without violating any latency/bandwidth bounds. The power management policy on its part evaluates both the power-down strategies for their applicability and potential for energy savings, based on the selected memory access granularity, memory page policy and memory service cycle durations. The two power-down strategies only differ in their powering-up policy and frequency of powering-up, with the aggressive strategy reducing the number of power-ups to the minimum required number and yet powering-up the memory in time for the next request (Chapter 5).

Together, these five important contributions successfully achieve the goals of this thesis and play a part in energy-efficient usage of DRAMs.

# 1.4 Organization of this Thesis

The rest of thesis is organized as follows:

Chapter 2 describes the details of the proposed DRAM power model (DRAM-Power), its modeling differences compared to other power models based on current measures (especially Micron's) and the adaptations made to it to address most DRAM generations from DDR2 to DDR4, LPDDR to LPDDR3 and Wide IO DRAMs. The chapter also briefly discusses the tool-flow, command scheduler and command trace analysis of the open-source DRAMPower tool.

Chapter 3 describes the proposed post-manufacturing DRAM power and performance characterization methodology that identifies the excess margins in DRAM current and performance measures in the datasheets for any given DRAM device. This chapter also describes the modifications made to the baseline NGSPICE model to incorporate impact of process variations on DRAM power and performance, and derives better than worst-case current measures for a majority of DRAM devices in a generation with a given configuration.

Chapter 4 includes the tests and experiments used to verify and validate DRAMPower against real hardware measurements and compares its estimates against those of Micron's model.

Chapter 5 describes the proposed performance-neutral power optimization strategies and the power-management policy that enables optimization of idle DRAM power without impacting the original performance guarantees. The chapter describes the latency and bandwidth guarantees provided by real-time DRAM memory controllers and analyses the impact of the proposed power-down strategies on these measures, highlighting their worst-case performance neutrality.

Chapter 6 describes the conclusions drawn from this work and sheds light on possible future extensions to improve this work, both in terms of power estimation and optimization.

# CHAPTER 2

# Cycle-Accurate DRAM Power Modeling

DRAM memories contribute significantly to the overall system power and energy consumption and require effective power management for their energy-efficient use. The key prerequisite to their efficient power/energy management is to use accurate DRAM power and energy consumption estimates. Hence, system designers require high-precision power models that accurately estimate power and energy consumption of the different DRAM operations, state transitions and power-saving modes.

All DRAM vendors furnish a set of standard current measures corresponding to different combinations of memory operations specified by JEDEC. These measures are employed by high-level power models, which break them down into measures corresponding to individual DRAM operations. However, existing high-level power models lack precision in their modeling of the different DRAM operations, and hence do not report accurate power measures. Alternatively, circuit-level power models can be employed for power estimation, since they perform accurate modeling of these operations, transitions and modes. However, the underlying DRAM architectures employed by these circuit-level models do not accurately reflect architectural distinctions between different DRAM generations, and vendor-specific designs, and need to be extensively adapted to reflect similar configuration as a particular DRAM device, timing behavior and current consumption.