# MSc THESIS

## Memory Pattern Generation based on Specification and Environment

Williston Sterchi Hayes Jr.

#### Abstract

Guaranteeing hard real-time requirements in systems with multiple requestors accessing a single memory is a difficult task due to variable access times of SDRAMs. This problem has been solved with the use of the Predator memory controller, which is able to put a bound on worst-case latency and worst-case bandwidth. This controller uses precomputed sequences of SDRAM commands, called memory access patterns, in order to interact with SDRAMs. However, these patterns are difficult to construct due the complexity of SDRAM timing parameters and constraints. Thus, three heuristicbased pattern generation algorithms are developed that explore the trade-offs between run time and bandwidth offered. In the end, the approach selected provides adequate bandwidth while still offering a low run time. This pattern generator has been integrated into the Predator memory controller design flow.

ES-MS-2009-0614000

## Memory Pattern Generation based on Specification and Environment

### THESIS

submitted in partial fulfillment of the requirements for the degree of

### MASTER OF SCIENCE

in

### EMBEDDED SYSTEMS

by

Williston Sterchi Hayes Jr. born in San Francisco, The United States of America

Embedded Systems Department of Computer Science and Engineering Faculty of Mathematics and Computer Science Eindhoven University of Technology

### by Williston Sterchi Hayes Jr.

### Abstract

Guaranteeing hard real-time requirements in systems with multiple requestors accessing a single memory is a difficult task due to variable access times of SDRAMs. This problem has been solved with the use of the Predator memory controller, which is able to put a bound on worst-case latency and worst-case bandwidth. This controller uses precomputed sequences of SDRAM commands, called memory access patterns, in order to interact with SDRAMs. However, these patterns are difficult to construct due the complexity of SDRAM timing parameters and constraints. Thus, three heuristic-based pattern generation algorithms are developed that explore the trade-offs between run time and bandwidth offered. In the end, the approach selected provides adequate bandwidth while still offering a low run time. This pattern generator has been integrated into the Predator memory controller design flow.

| Laboratory        | : | Embedded Systems                         |

|-------------------|---|------------------------------------------|

| Committee Members | : |                                          |

| Advisor:          |   | Henk Corporaal, Electronic Systems, TU\e |

| Member:           |   | Benny Åkesson, Electronic Systems, TU\e  |

| Member:           |   | Kees Goossens, SAI, NXP                  |

ii

# Contents

| Lis      | st of | Figures vi                    | iii |

|----------|-------|-------------------------------|-----|

| Lis      | st of | Tables                        | ix  |

| Ac       | knov  | vledgements                   | xi  |

|          |       |                               |     |

| 1        | Intr  | oduction                      | 1   |

|          | 1.1   | Application Requirements      | 1   |

|          | 1.2   | Considered Systems - Platform | 2   |

|          | 1.3   | Problem Statement             | 3   |

|          | 1.4   | Goal                          | 4   |

|          | 1.5   | Contributions                 | 4   |

|          | 1.6   | Outline                       | 4   |

| <b>2</b> | SDF   | RAM                           | 7   |

|          | 2.1   | Architecture                  | 7   |

|          | 2.2   | Commands                      | 8   |

|          | 2.3   | Timing Constraints            | 10  |

| 3        | Mer   | nory Efficiency               | 13  |

|          | 3.1   | Peak Bandwidth                | 13  |

|          | 3.2   | Data Efficiency               | 13  |

|          | 3.3   | Bank Efficiency               | 14  |

|          | 3.4   | Switching Efficiency          | 15  |

|          | 3.5   | Refresh Efficiency            | 15  |

|          | 3.6   | Net Bandwidth                 | 15  |

| 4        | Mer   | nory Controllers              | 17  |

|          | 4.1   | Arbiter                       | 17  |

|          | 4.2   | Memory Mapping                | 18  |

|          | 4.3   | Command Generator             | 21  |

|          | 4.4   | Types of Memory Controllers   | 21  |

| <b>5</b> | Mer   | nory Patterns 2               | 25  |

|          | 5.1   | Pattern Overview              | 25  |

|          | 5.2   | Types of Patterns             | 26  |

|          | 5.3   | Pattern Dominance             | 27  |

|          | 5.4   |                               | 29  |

|          | 5.5   |                               | 31  |

|          | 5.6   | Optimality                    | 32  |

| 6            | Algorithm Approaches                                   | <b>35</b> |

|--------------|--------------------------------------------------------|-----------|

|              | 6.1 Pattern Generation Design Decisions                | 35        |

|              | 6.2 Branch and Bound                                   | 39        |

|              | 6.3 As Soon As Possible Scheduling                     | 43        |

|              | 6.4 Bank Scheduling                                    | 45        |

|              | 6.5 Results                                            | 46        |

| 7            | Algorithm Context                                      | 49        |

|              | 7.1 Tooling Flow Overview                              | 49        |

|              | 7.2 Integration of Pattern Generator                   | 51        |

|              | 7.3 Non-allocated Bandwidth Calculations               | 54        |

|              | 7.4 Experimental Results                               | 55        |

| 8            | Conclusion                                             | 61        |

| 9            | Future Work                                            | 63        |

|              | 9.1 3D Stacking                                        | 63        |

|              | 9.2 Optimal Pattern Generation                         | 63        |

|              | 9.3 Low Power Considerations                           | 63        |

|              | 9.4 Future SDRAM Iterations                            | 64        |

| Bi           | bliography                                             | 65        |

| A            | List of relevant DDR timing constraints and parameters | 67        |

| В            | Glossary                                               | 69        |

| С            | Latency Equation Derivations                           | 71        |

| D            | Requestor Specification                                | 73        |

| $\mathbf{E}$ | DDR Memory Specification                               | 75        |

# List of Figures

| 1.1                                    | General overview of the considered system.                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                                  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4               | SDRAM Bank Architecture                                                                                                                                                                                                                                                                                                                                                                                      | 8<br>9<br>9                                                                        |

| 3.1                                    | Visual representation of bank efficiency. Blank slots in the command bus represent NOP commands                                                                                                                                                                                                                                                                                                              | 14                                                                                 |

| 4.1<br>4.2<br>4.3                      | Architecture of a memory controller                                                                                                                                                                                                                                                                                                                                                                          | 17<br>18                                                                           |

| $4.4 \\ 4.5$                           | itself.                                                                                                                                                                                                                                                                                                                                                                                                      | 19<br>20                                                                           |

| 4.6                                    | (top) compared to an interleaving memory map (bottom)                                                                                                                                                                                                                                                                                                                                                        | 21                                                                                 |

| 4.7                                    | (top) compared to an interleaving memory map (bottom)<br>Illustration showing reordering of commands to reduce data bus direction<br>changes. The top figure shows the requests in order, the bottom figure<br>shows the requests reordered                                                                                                                                                                  | 21<br>22                                                                           |

| $5.1 \\ 5.2$                           | Sequence of various patterns                                                                                                                                                                                                                                                                                                                                                                                 | 25                                                                                 |

| 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8 | commands.       .       .         Write pattern for DDR2-400 SDRAM.       .       .         Switching patterns being used between read and write patterns.       .       .         Illustration of read dominance.       .       .         Illustration of write dominance.       .       .         Illustration of mix dominance.       .       .         Dominance scale viewed on a line.       .       . | 26<br>26<br>27<br>27<br>28<br>28<br>28<br>29                                       |

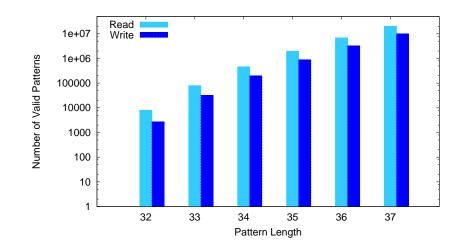

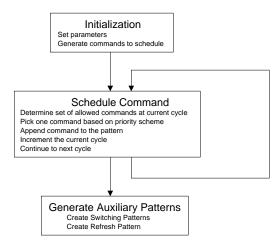

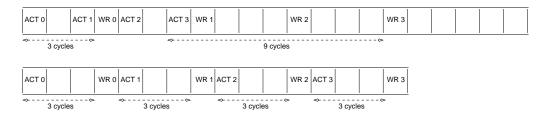

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | Illustration of moving NOPs from back to front of pattern.Example of command tree.Flow diagram of the branch and bound algorithm.Flow diagram of the branch and bound algorithm.Pseudo-code of sanity check optimization.Number of valid patterns at BurstCount 2 for a DDR2-400 SDRAM devicePseudo-code of ASAP algorithm                                                                                   | <ol> <li>37</li> <li>40</li> <li>41</li> <li>42</li> <li>43</li> <li>44</li> </ol> |

| 6.7                                    | Flowchart of the ASAP algorithm                                                                                                                                                                                                                                                                                                                                                                              | 44                                                                                 |

| 6.8  | Example of a pattern generated by the ASAP algorithm (top), and a        |    |

|------|--------------------------------------------------------------------------|----|

|      | pattern generated by the branch and bound algorithm (bottom)             | 44 |

| 6.9  | Pseudo-code of bank scheduling algorithm                                 | 45 |

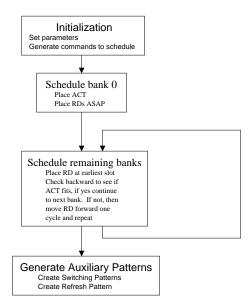

| 6.10 | Flow diagram of the bank scheduling algorithm                            | 46 |

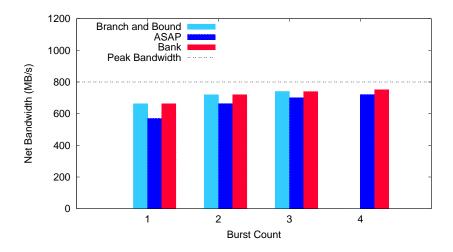

| 6.11 | Comparison of net bandwidth guaranteed by algorithms for a DDR2-400      |    |

|      | SDRAM                                                                    | 47 |

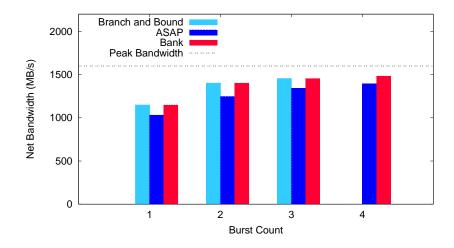

| 6.12 | Comparison of net bandwidth guaranteed by algorithms for a DDR2-800      |    |

|      | SDRAM                                                                    | 47 |

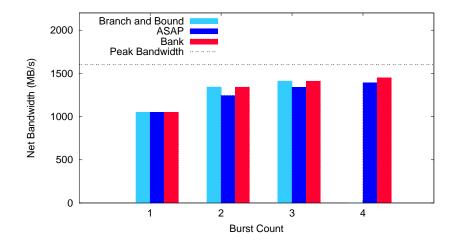

| 6.13 | Comparison of net bandwidth guaranteed by algorithms for a DDR3-800      |    |

|      | SDRAM                                                                    | 48 |

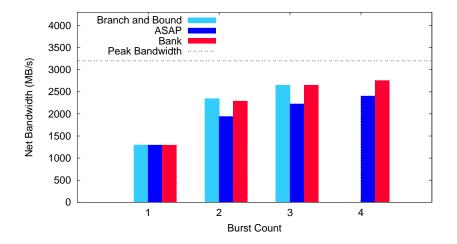

| 6.14 | Comparison of net bandwidth guaranteed by algorithms for a DDR3-1600     |    |

|      | SDRAM                                                                    | 48 |

| 7.1  | Pseudo-code of integrated pattern generator.                             | 52 |

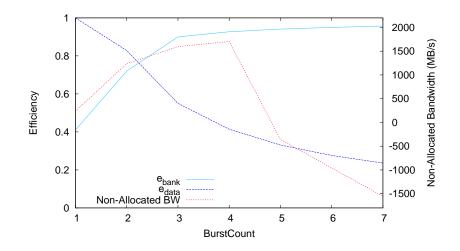

| 7.2  | Trade-off between $e_{data}$ and $e_{bank}$ .                            | 53 |

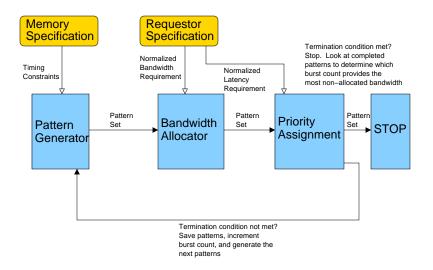

| 7.3  | Flow of integrated pattern generator                                     | 53 |

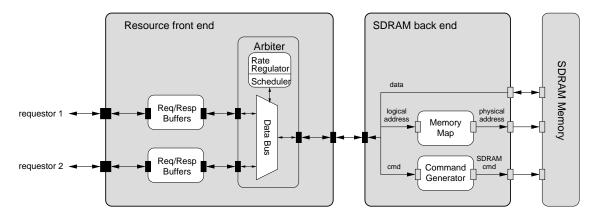

| 7.4  | Illustration of Predator architecture.                                   | 54 |

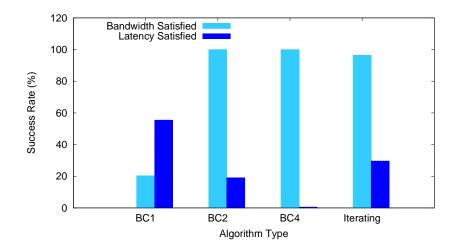

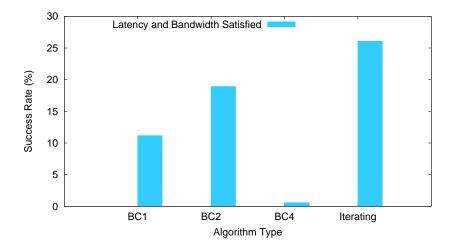

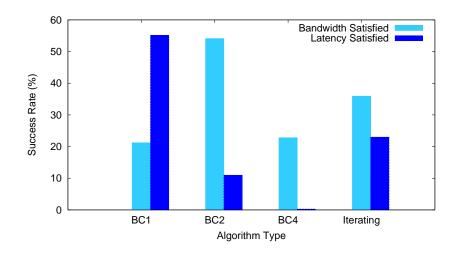

| 7.5  | Comparison of fixed BurstCount generator and an iterating generator with | 01 |

| 1.0  | large request size. The memory specification used is DDR2-400            | 57 |

| 7.6  | Comparison of fixed BurstCount generator and an iterating generator with |    |

|      | large request size. The memory specification used is DDR2-400            | 57 |

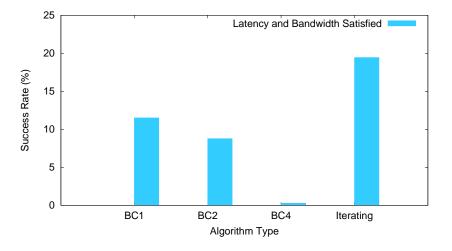

| 7.7  | Comparison of fixed BurstCount generator and an iterating generator with |    |

|      | small request size. The memory specification used is DDR2-400.           | 58 |

| 7.8  | Comparison of fixed BurstCount generator and an iterating generator with |    |

|      | small request size. The memory specification used is DDR2-400            | 58 |

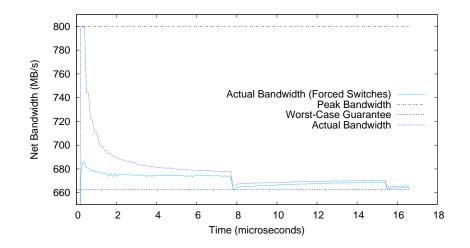

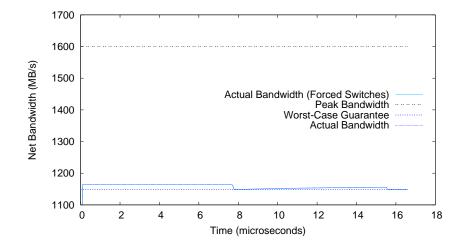

| 7.9  | Average bandwidth over time for a DDR2-400 device by simulation          | 59 |

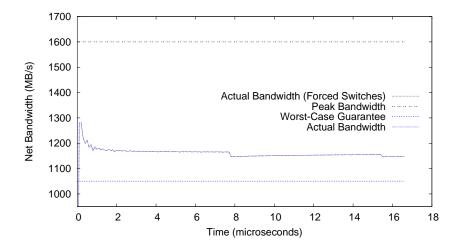

| 7.10 | Average bandwidth over time for a DDR2-800 device by simulation          | 59 |

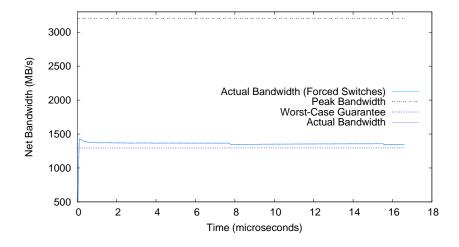

| 7.11 | Average bandwidth over time for a DDR3-800 device by simulation          | 60 |

| 7.12 | Average bandwidth over time for a DDR3-1600 device by simulation         | 60 |

|      |                                                                          |    |

# List of Tables

| 2.1 | Typical characteristics of a DDR SDRAM device                                                                         | 8  |

|-----|-----------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Comparison of timing constraints in nanoseconds and clock cycles for two SDRAM devices.                               | 10 |

| 4.1 | Comparison of characteristics of different memory controllers                                                         | 23 |

|     | Example of normalized bandwidth changing with <i>BurstCount</i> Values of load, request size, and latency requirement |    |

# Acknowledgements

This project has been offered through NXP Semiconductors with cooperation from the Eindhoven University of Technology. I would like to thank Kees Goossens and Benny Åkesson for allowing me to join their team in the System-On-Chip Architecture & Infrastructure group (SAI). I am very grateful to Benny Åkesson for his excellent guidance and help during the course of this project. Without him this project would not have been possible. I am also grateful to Kees Goossens as he provided a lot of insight into the project that allowed me to continually gain a new outlook on the thesis.

I would also like to thank Henk Corporaal for his valuable remarks and considerations made on the project. He always provided an interesting perspective, and encouraged the project's movement.

Additionally, Ad Siereveld and Roelof Salters at NXP are held in gratitude for sharing their deep knowledge of SDRAMs and SDRAM controllers with me. The information received from them helped clarify many problems I encountered in this project.

I would like to thank all of my colleagues at NXP for the various discussions we held and coffees we drank. Matteo Scordino, Ulf Winberg, Frank Ophelders, Dongrui She, Getachew Teshome, Pim Ritzen, Anna Kosek, Tion Kusumo, Jing Jing, Fabio Pania, and Adriano Sanches, you made this a great experience for me.

Williston Sterchi Hayes Jr. Eindhoven, The Netherlands August 31, 2009 In this thesis we present a problem in the domain of real-time embedded systems that utilize SDRAM devices. In Section 1.1, we introduce requirements that applications with real-time requirements running on System-on-Chips (SoCs) have. This will be followed by Section 1.2, where we discuss the platform considered for this thesis. Section 1.3 details the problem of using SDRAM devices with the requirements specified in Section 1.1. Section 1.4 presents our solution to the problem. This is followed by sections detailing our contributions as well as the outline of this thesis.

## **1.1** Application Requirements

As transistors have gotten smaller due to advances in technology, now entire systems can be implemented on a single chip [13]. These SoCs typically have multiple IP blocks, and the gain offered by using SoCs is that the interconnect distance between IP blocks is typically much smaller than that of a traditional system. These shorter interconnects reduce time needed to transfer information from one IP block to another. Additionally, these systems use less power, which is also of great importance to embedded systems as power is a limited resource. We will now discuss the requirements of applications running on SoCs.

Applications running on real-time systems are used in a variety of situations, with each situation requiring different behavior. The first type of application requirements is soft requirements, meaning that if a deadline is not met, there still might be some useful information to be gained [5]. An example of an application with soft real-time requirements is an MPEG-2 decoder. This type of application would require good average-case bandwidth. If frames are not fully processed in time then the picture may appear pixilated or blocky. Yet, one can imagine that a viewer would still prefer to see a blurry picture over no picture at all.

The second type of requirements is hard-real time requirements. Applications which have hard real-time requirements cannot miss their deadlines under any circumstances [10,16]. An example of a system with hard real-time requirements is an anti-lock braking system found in automobiles. These systems require a low worst-case latency. If this latency requirement is not met, then the automobile's wheels may lock up resulting in skidding, and loss of control of the vehicle.

Another aspect of applications running on SoCs is their latency requirements. Some applications have very tight latency deadlines that must be respected, while other types of applications have more lenient deadlines. Both must be accounted for.

In this thesis we focus on applications which have hard real-time requirements. Additionally, we assume that we know nothing about the traffic that is generated, except for bandwidth and latency requirements. Finally, we state that we want to give guarantees on worst-case latency and worst-case bandwidth that are analytically provable.

### **1.2** Considered Systems - Platform

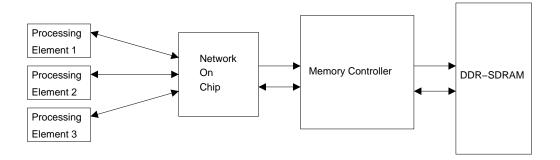

This section details the system that is modeled. We have chosen to represent our system as multiple processing elements utilizing a single memory controller. We define the requesting service from these processing elements to the memory controller as requestors. We consider the case where the memory controller is controlling a DDR-SDRAM [2]. The entire overview can be seen in Figure 1.1.

The reason we represent our system as multiple processing elements using a single memory controller is because this is often required in practical cases. Having multiple memories is not a cost effective way to store data, because it increases power consumption and may require more expensive packaging. Thus, sharing memory decreases chip real estate and power usage, and results in a low cost-per-bit.

Figure 1.1: General overview of the considered system.

#### 1.2.1 Predictability

All SDRAMs are predictable in the sense that they have ranges of times in which data is accessed, however, these ranges are not indicative of normal performance. We hope to place bounds on bandwidth and latency such that we can prove the exact value and make the value useful, i.e. the bounds we place are improved over the absolute worstcase values listed in the specification. The reason why we are concerned about improving worst-case values is that bandwidth is a shared, scarce resource, and has been proven to be a main bottleneck in SoCs [6,12]. Thus, any improvement that can be determined in the worst-case is very useful.

**Definition 1.1 (Predictability)** A predictable resource is one that has a known, useful, worst-case bound.

The way a controller interacts with an SDRAM is by sending commands. These commands take the form of a read command, a write command, and a few other auxiliary commands. These read and write commands return a few words of data, the amount of which depends on a memory parameter.

The reason that placing bounds on latency and bandwidth is difficult is due to the fact that SDRAMs have varying access times depending on the sequence of commands. The amount of time it takes to access a word of data from an SDRAM depends on the current state of the memory. This results in variable bandwidth and latency.

Most memory controllers handle the problem of variable bandwidth and latency in two ways. *Statically scheduled controllers* work by using a fixed, precomputed schedule, in which the bandwidth and latency can be computed at design time, as long as the system is rigid. *Dynamically scheduled controllers* attempt to improve the average-case performance as much as possible, and they do this by creating their schedules at run time, and thus allow for a more flexible environment, at the cost of not being able to place analytic bounds on worst-case latency and bandwidth. Therefore in order to guarantee bounds that are known and useful in the case when we only know the bandwidth and latency requirements of applications, we need a new type of memory controller.

The memory controller we use is called Predator. It is a hybrid memory controller and as such it shares qualities of both statically scheduled and dynamically scheduled controllers, and is being developed at NXP [2]. The benefits of this controller are that it offers a predictable arbitration scheme which allows the bounding of latency. Additionally, it uses memory patterns that allow for the net bandwidth to be bounded. The details of this controller are discussed in Section 4.4.3. An important aspect of this memory controller is the way it interacts with the memory. It does not send individual commands to the memory, but rather it sends fixed-length sequences of commands, called *memory patterns*, to the memory. There exists one type of pattern for reading, one for writing, and 3 others that are introduced in Section 5. The read pattern is used whenever a requestor wishes to retrieve data from the memory, and the write pattern is used when a requestor wishes to store data to the memory.

### **1.3** Problem Statement

The problem that arises from the use of the memory controller mentioned above is that the patterns it uses to interact with the memory are difficult to compute, for numerous reasons.

There are many timing constraints and parameters that must be observed when creating a pattern [8,9]. Some of these constraints are independent of each other, and some are dependent. Therefore, due to the complexity of the constraints, creating these patterns by hand is error prone and time consuming.

A second problem that arises is that we would like to use the same controller on a variety of different SDRAM devices. Incidentally, the timing parameters and constraints listed above are different for every device type. Additionally, the timing parameters are based on the speed of clock being used to time the device. To further complicate the issue, every device has multiple configurations, which also influences the parameters. Therefore this problem further reinforces the idea that creating these patterns by hand is time consuming.

Another issue that occurs is that we must take into account requestor requirements. As we shall see in Section 3, the amount of data being requested by a requestor compared to the amount of data returned by a memory pattern has a significant effect on the overall efficiency, and thus the bandwidth provided by the memory controller.

To address the problems detailed above, we present our goal for this thesis in the following section.

## 1.4 Goal

The goal of this thesis is to create an algorithm that runs at design time, which produces memory patterns that are utilized by Predator. This algorithm should allow for the generation of multiple patterns such that different combinations of patterns can be evaluated for efficiency. The algorithm generates patterns based on a memory specification and requestor bandwidth and latency requirements.

The requirements of the algorithm are that it should take as input a memory specification and requestor requirements. The algorithm should produce memory patterns that provide as much bandwidth as possible, and that the production time of these patterns should not exceed 48 hours.

The benefits of this approach are that it removes the time-consumption and mistake factors out of the pattern generation. Furthermore, having an algorithm instead of performing the computations by hand allows us to apply the generator to future iterations of SDRAM, such as DDR4 and beyond.

### 1.5 Contributions

The contributions offered are that of creating a memory pattern generator which provides high-bandwidth patterns for many different memory types. This generator is integrated into the Predator configuration flow and is used by the hardware implementation.

The work of Eelke Strooisma on the Predator architecture is extended to include the notion of pattern dominance [17].

Three heuristic based approaches were developed for the memory pattern generator and compared against eachother. These approaches explore trade-offs between run time and bandwidth provided.

This pattern generator was integrated into the existing design flow of Predator, and new algorithms were developed to allow the configuration tools to work with any pattern set for any memory.

### 1.6 Outline

This thesis begins by discussing the architecture and run time operation of SDRAM devices in Section 2. In Section 3, concepts for measuring the efficiency of memories are discussed. This is followed by a general discussion of memory controllers, which includes their architecture, operation, and the state of the art in Section 4. Section 5 provides an in-depth look at the definition of memory patterns, how they are used by Predator, and how they may be used to determine the bandwidth provided by the memory controller. Section 6 details the 3 heuristic-based approaches that were created. The Predator design

flow, and how the generator is integrated into that flow, is described in Section 7. In the remaining two sections, conclusions derived from the thesis are discussed, and possible future work is detailed.

6 CHAPTER 1. INTRODUCTION

# 2

## SDRAM

Prior to SDRAMs, data was stored in magnetic rings, which stored bits as the polarity of the magnetic field. This technology was slow and expensive, and thus Robert Dennard began the search for a faster memory type at IBM in 1967 [1].

His idea for improving this older design was to develop a memory cell which was composed of a capacitor and transistor, where the value of a bit is stored as charge in the capacitor. Today, SDRAMs are used in a huge variety of systems such as personal computers, automobiles, and mobile phones. They are used in so many places due to their cost-effectiveness in storing volatile data, as well as their speed.

Over time more modifications were made to the SDRAM to improve its effectiveness. The most significant of these was the introduction of DDR SDRAM. DDR memories provide a word of information twice per clock cycle, thus doubling the maximum rate of data transfer.

### 2.1 Architecture

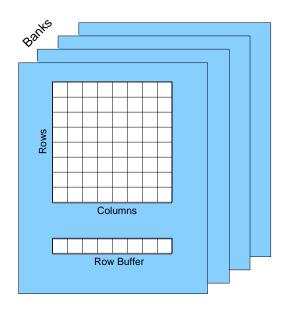

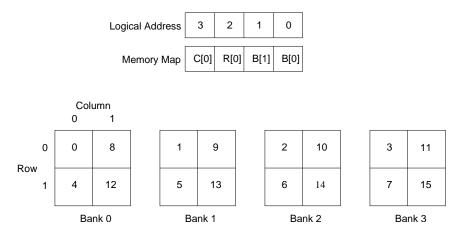

An SDRAM device is composed of multiple banks. Each bank contains an array of memory cells, along with a row buffer, as shown in Figure 2.1. When an incoming request is sent to the SDRAM, the address is decoded into the bank address, row address, and column address based on a memory map. If the request is a read, then the row of data cells specified by the address is loaded into the row buffer. Once it is there, the data can then be read by an external resource. Conversely, if the request is a write, then the address is decoded as before, but the data is sent into the row buffer. After the write has finished loading data into the buffer, it is committed into the actual memory cells.

Using a bank architecture allows for a high degree of parallelism when accessing the SDRAM. Each bank can be considered as a separate memory that happens to share output pins. Each bank can be prepared for reading and writing in a pipelined fashion, which increases bandwidth. Additionally, due to the sharing of pins, the overall output pin count is lower than that of an equivalent capacity memory that does not share pins. Also, as a result of sharing output pins, less power is consumed.

There are two buses in an SDRAM that allow for interaction with other components. The first is the command bus, and it is an input into the SDRAM that is used to specify which type of action the SDRAM should perform. The second bus is a shared, bidirectional data bus. Any data that is transferred to or from the SDRAM must go through this bus.

Typical numbers for current DDR SDRAM memories are shown in Table 2.1.

Figure 2.1: SDRAM Bank Architecture

Table 2.1: Typical characteristics of a DDR SDRAM device.

| Number of banks | 4 or 8        |

|-----------------|---------------|

| Capacity        | 256MB - 8GB   |

| Word widths     | 4, 8, 16 bits |

| Column bits     | ~10           |

| Row bits        | $\sim 15$     |

### 2.2 Commands

In order to interact with the SDRAM, some atomic commands are used. Most importantly, these commands allow for data to be read from the memory and written to the memory, as well some auxiliary commands that are required for proper operation.

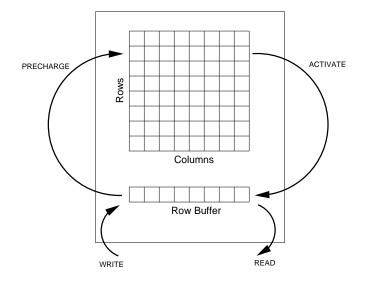

The *activate* command takes a row and bank address as its argument, and then loads the specified row at the specified bank into the row buffer. Once data has been loaded into the row buffer it is allowed to be modified or read from.

The *read* command retrieves one burst of data from an activated row, and a *write* command sends one burst of data to the activated row. This use of these two commands is the only way data may be transferred to or from the memory.

The *precharge* command is the converse of the activate command. It accepts a row and bank address, and commits the row buffer in the specified bank into the specified row in the cell array. There is a special case concerning the read and write commands above, and that is they may be combined with an *auto-precharge*. The way auto-precharge works is that after a read or write command has been submitted to the memory, the bank will be precharged automatically at the earliest opportunity without any explicit command. An example of the activate-precharge loop is shown in Figure 2.2.

Due to the fact that bits in an SDRAM are represented by the charge in a capacitor,

Figure 2.2: SDRAM Activate and Precharge Loop.

and that capacitors are not perfect and leak charge over time, a mechanism for keeping the data valid had to be invented. Hence, a *refresh* command was designed. This command 'refreshes' the data stored in the memory cell arrays of bank by recharging the capacitors that are storing data. This command may only be issued when all banks in the memory have had their row buffers precharged.

There are many timing constraints, as we shall see in the next section, that prevent two commands from being executed directly after each other. This space is then taken up by NOP commands, which stand for *no operation*. These commands essentially let the memory idle while waiting for another command to be scheduled. For clarification in figures, NOP commands are shown as blanks. The remaining commands are abbreviated as follows:

- Activate(Bank, Row) = ACT-Bank

- Read(Bank, Row, Column) = RD-Bank

- Write(Bank, Row, Column) = WR-Bank

- Refresh = REF

- Precharge(Bank, Row) = PRE-Bank

Figure 2.3: Example of a command sequence.

Also noteworthy is that row and column addresses are dropped from commands in their abbreviated form. This is due to the fact that the row and column addresses are not significant with respect to timings and constraints. Only the bank has any effect in this regard.

## 2.3 Timing Constraints

There are many timing constraints and parameters that restrict the commands allowed to be scheduled at a given time. A *memory specification* lists all constraints for a given SDRAM device. The constraints specify the minimum amount of time that must pass between two commands. These constraints are listed in Appendix A. A small example is outlined below.

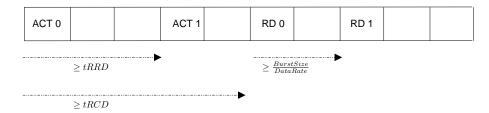

Four of the constraints and parameters are demonstrated in Figure 2.4. When we would like to send an activate command to two different banks, tRRD specifies the minimum amount of time that must pass after the first activate has been executed until the second one may be executed. tRCD specifies the minimum amount of time between an activate command and a read or write command. BurstSize refers to the number of words produced or consumed by the memory per read or write command, and thus is used to determine the granularity of a memory access. DataRate is the number of words on the data bus per clock cycle.

Figure 2.4: Example of *tRRD*, *tRCD*, *BurstSize*, and *DataRate* requirements and parameters.

As we see in Figure 2.4, the second activate may not be scheduled until tRRD cycles after the first activate, and the read command to bank 0 must be tRCD cycles after the activate to bank 0. The minimal delay between read commands is specified as such as we must make sure that a new read command does not interrupt data already being put on the data bus by a previous read command.

Table 2.2: Comparison of timing constraints in nanoseconds and clock cycles for two

SDRAM devices.

|            | DDR2-400 |    | DDR3-1600 |    |

|------------|----------|----|-----------|----|

| Constraint | ns       | сс | ns        | сс |

| tCK        | 5        | 1  | 1.25      | 1  |

| tRC        | 55       | 11 | 45        | 36 |

| tRCD       | 15       | 3  | 10        | 8  |

| tRRD       | 7.5      | 2  | 6         | 5  |

| tRP        | 15       | 3  | 10        | 8  |

An interesting point to take away from these parameters is that they are specified in nanoseconds, and that they do not change very much with successively newer SDRAM devices. This means that as the clock speed increases, the number of cycles needed to satisfy constraints also increases. This is demonstrated in Table 2.2 by listing a small sample of actual constraint values for different memory devices. The DDR2-400 device is assumed to be clocked at its maximum frequency of 200MHz, and the DDR3-1600 device is also assumed to be clocked at its maximum of frequency of 800MHz, which yields a clock cycle of 5ns and 1.25ns respectively.

To make sensible calculations regarding latency and bandwidth, we need to establish a method for determining how efficiently a memory behaves. In this section the efficiency model of Woltjer [18] is presented. This model is used to differentiate types of efficiencies. Once these efficiencies are known, they may be used to calculate the amount of bandwidth provided by an SDRAM memory controller.

## 3.1 Peak Bandwidth

**Definition 3.1 (Peak Bandwidth)** Peak bandwidth is the maximum number of bytes per second that can be transferred on the data bus.

Computing the peak bandwidth is important as this number represents the maximum bandwidth offered by a memory. Inefficiencies introduced by physical characteristics of an SDRAM can significantly lower the actual amount of bandwidth provided to a resource.

If we let DataBusWidth equal the width in bits of the data bus, and ClockFrequency be the frequency of the clock, then we have

$$bandwidth_{peak} = \frac{ClockFrequency\ cycles}{\text{second}} * \frac{2\ \text{bursts}}{\text{cycle}} * \frac{DataBusWidth\ \text{bits}}{\text{burst}} * \frac{1\ \text{byte}}{8\ \text{bits}}$$

(3.1)

As an example, if we had a DDR2-400 SDRAM device running at 200MHz with a 16 bit data bus we have

$$bandwidth_{peak} = \frac{200M \text{ cycles}}{\text{second}} * \frac{2 \text{ bursts}}{\text{cycle}} * \frac{16 \text{ bits}}{\text{burst}} * \frac{1 \text{ byte}}{8 \text{ bits}} = 800 \text{ MB/s}$$

Most memory controllers are unable to provide this amount of bandwidth due to physical characteristics of an SDRAM, such as refresh. In order to properly calculate the worst-case bandwidth offered by a given memory, we must examine areas of SDRAM operation where efficiency is lost.

## 3.2 Data Efficiency

**Definition 3.2 (Data Efficiency)** Data efficiency is the amount of data requested by a component compared to the actual amount of data returned by the memory controller.

Data efficiency is traffic dependent, and therefore cannot be computed at design time unless we know some information about the requestors using the memory controller. Specifically, we need to know the granularity of the memory, as well as the sizes of requests of the resources. Often, the amount of data requested does not exactly match the amount of data actually returned by a memory. This occurs because there can be many types of processing elements performing different actions, that share one memory. Because the requestors' application requirements may be very different, it is possible that the amount of data being requested may also be very different. Thus, frequently a requestor is given more data than it requires, and must throw away the excess. This data that is thrown away is representative of the data efficiency.

As seen in Equation (3.2), the severity of the loss in efficiency is dependent on the request size. Requestors with a small request size using a memory with a large granularity will have extremely poor data efficiency. As we see later in Section 3.6, this translates to poor actual bandwidth as well. Thus, data efficiency can change significantly depending on the resources using the memory controller. Experimentally, it has been observed that a data efficiency of 75% is expected for an MPEG-2 stream [18].

$$e_{data} = \frac{size_{request}}{granularity_{memory}} \tag{3.2}$$

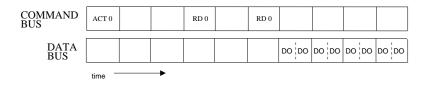

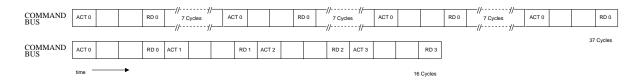

As an example, we examine Figure 3.1 and assume a requestor wants to read 6 words. However, the granularity of this memory is such that it provides 4 words per read burst. Thus, in order to provide 6 words to the requestor, 2 read commands must be sent. Therefore  $e_{data}$  in this case is 6/8, or 75%.

Figure 3.1: Visual representation of bank efficiency. Blank slots in the command bus represent NOP commands.

### **3.3** Bank Efficiency

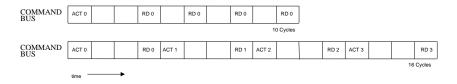

The time taken to access a memory cell is highly variable for SDRAMs. If a read command is sent to a bank which currently has a different row already activated, the controller must first precharge the current row, activate the new row, and then send the read command. This penalty is captured in the bank efficiency. By examining the amount of cycles that data is on the bus, compared to the total number of cycles taken to get that data on the bus, we are able to compute this value. Bank efficiency is dependent on the memory map chosen, as we shall see in Section 4.2. As the bank efficiency is dependent on the addresses of requests, which are not known at design time, we cannot place a useful bound on bank efficiency.

If we examine Figure 3.1, we are also able to compute the bank efficiency of this pattern. In this particular period, we see 4 cycles where there is data on the bus, and that the entire length of this group of commands is 10 cycles long. Therefore the bank efficiency is 40%.

$$e_{bank} = \frac{DataCycles}{TotalCycles} \tag{3.3}$$

### **3.4** Switching Efficiency

SDRAMs require a time buffer between a read and write command, such that the direction of the data bus can be reversed. This often results in cycles where no data can be on the bus. Thus, we must take this drop in efficiency into account by examining the difference between the time taken for a read and write command, compared to the time taken for a read and write commands, plus their respective switching costs. According to Woltjer [18], traffic consisting of 70% reads and 30% writes yields a switching efficiency of 93.8%.

In general, the switching efficiency is not possible to compute at design time as the read to write switching frequency is not known at design time. However, in Section 5 we see how some design decisions allow us to compute this value.

### 3.5 Refresh Efficiency

Every SDRAM must be refreshed periodically in order to maintain the integrity of the stored data. However, in order for a refresh to occur, all activity must cease, and all banks must be precharged. Refresh efficiency is used to determine how much the effectiveness of the memory is changed due to the lost time introduced by the refresh command.

Therefore we compute  $e_{refresh}$  as the amount of time in a period where the memory is not busy with refresh commands.  $t_{ref}$  refers to the amount of time taken for a refresh command to be executed, and  $t_{period}$  is the period in which refreshes are executed.

$$e_{refresh} = 1 - \frac{t_{ref}}{t_{period}} \tag{3.4}$$

Refresh efficiency is not traffic dependent and therefore can be calculated at design time. Due to the very long refresh period (7.8  $\mu s$  at normal operating temperatures) compared to the time taken to execute a refresh command (on the order of 100 ns), the refresh efficiency is usually around 99%.

### 3.6 Net Bandwidth

**Definition 3.3 (Net Bandwidth)** Net bandwidth is the actual amount of bandwidth provided by the memory to requestors.

The concern of applications using this memory controller is directed at the net bandwidth, as this is the amount of bandwidth they are actually provided. It is calculated by simply finding the product of the above efficiencies and the peak bandwidth, with one exception.  $e_{data}$  is not taken into account due to the way bandwidth allocation and requestor requirements are handled by our memory controller. As we shall see in Section 7.1.1,  $e_{data}$  is factored into the requestor's requirements. Thus, the equation for calculating  $bandwidth_{net}$  becomes,

$$bandwidth_{net} = e_{bank} * e_{switch} * e_{refresh} * bandwidth_{peak}$$

(3.5)

# 4

# Memory Controllers

A memory controller is the interface between an SDRAM and the system. By having it as a separate unit, the system utilizing the SDRAM does not need to worry about timing constraints and other details of a specific SDRAM, and can simply treat the device as a general memory.

Specifically, a memory controller is responsible for the following tasks:

- Memory Mapping

- Command Generation

- Command Scheduling

Figure 4.1: Architecture of a memory controller.

The controller works by first accepting some requests from external IP blocks, and then storing them into request buffers. The addresses are then translated into the physical address space by means of a *memory map*, after which they are scheduled by the *arbiter*, and converted to memory commands by the *command generator*. The response from the memory is then sent back to the response buffer, and from there it will be sent back to the requestor.

## 4.1 Arbiter

The arbiter is responsible for determining which outstanding request is allowed to be sent to the memory controller. The logic for choosing which request ought to be scheduled depends on the type of system in which the controller is used. Some systems value low power use, some value high efficiency, and some value soft or hard real-time requirements. The characteristics of requests that the arbiter looks at are the requirements of the requestor, and optionally, the current state of the memory device.

## 4.2 Memory Mapping

A memory map provides a translation between logical memory and physical memory addresses. Thus, to a requestor, a memory looks like one large continuous array, while in reality the memory is organized into separate banks, rows, and columns. The choice of memory mapping is important as it has a large effect on latency and bandwidth, as seen in the following sections.

### 4.2.1 Continuous Memory Map

One type of translation used is called the continuous memory map. It is called such because successive addresses in the logical space are mapped to successive addresses in a single row in a single bank. Thus, the same row is accessed over and over again until the end of the row is met. At this point the mapping may switch to a new bank or to a new row in the same bank. As a result, row activation cost needs only to be incurred once in order to access a significant amount of successive data.

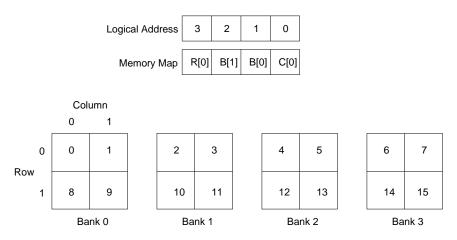

A continuously mapped address space can be seen in Figure 4.2. The memory presented is a highly simplified design for clarity. The memory has 4 banks, each with a 2 by 2 array of memory cells. Therefore 1 bit is needed to represent the column and row respectively, and 2 bits for the bank address. Thus, in total 4 bits are required for the logical address. As can be seen, if the least significant bit of the logical address is mapped to the column address, the next 2 significant bits are mapped to the bank address, and the final bit is mapped to the row address, we achieve a continuous memory map.

Figure 4.2: Illustration of a continuous memory map.

This type of mapping can be very beneficial to bandwidth and latency when the system has a low number of requestors, and the data being considered exhibits data locality. Consider a system with a single requestor, who requests data from consecutive logical addresses, as seen in Figure 4.2. If this requestor wants to send 4 read commands starting at bank 0, row 0, column 0, then we see that the memory controller needs to send an activate command to bank 0, and an activate to bank 1, and 2 reads to each bank. The resulting group of commands is shown in the top graphic in Figure 4.3.

Figure 4.3: Example of commands generated for a continuous memory map (top) and an interleaving map (bottom). The data bus has been wrapped back onto itself.

A significant problem occurs when we examine the sequence of commands generated in the worst-case scenario. We see in the top graphic of Figure 4.6 that when a requestor is trying to access different rows in the same bank, the efficiency of the memory controller drops significantly. This occurs because the minimum time between sending an activate command to the same bank is quite large.

Another issue occurs when the number of requestors begins to grow. The effectiveness drops significantly because of different requestors all sharing the same row buffer in a bank. With high numbers of requestors, the frequency of overwriting a given bank's row buffer increases, and this type of mapping becomes less viable.

As mentioned above, the use of continuous memory maps are limited to use cases where there are a low number of requestors. However, there is a method that may be employed to alleviate this problem, called bank partitioning. Bank partitioning is achieved by funneling requests from different requestors statically into different banks. In this way, the row buffers are not scrambled by interfering requestors assuming there are fewer requestors than the number of banks. However, to do this we must make assumptions regarding the number of requestors. A design goal of this thesis is to not make any assumptions regarding the number of requestors in the system, and thus we have chosen to not employ bank partitioning.

### 4.2.2 Interleaving Memory Map

The alternative type of translation to a continuous memory map is called an interleaving memory map, and is shown in Figure 4.4. This style of translation is called interleaving because successive bursts of accesses in the logical address space are mapped to different banks in the physical address space. Initially, we might expect a performance reduction as every bank must now be activated before it is accessed. However, there is a memory requirement that prevents a read or write command from being issued to the memory immediately after an activate command. Thus, there are some wasted cycles. In an interleaving memory map we can insert an activate command to a different bank while waiting to be allowed to schedule a read or write command. If the requested size of data is large enough, the cost of activating all banks can be ameliorated. Thus, the effectiveness of the interleaving memory map increases as the granularity of the accesses increases.

Figure 4.4: Illustration of an interleaving memory map

Another benefit of great importance to the goals of this thesis is that we want to place a useful bound on worst-case bandwidth. The problem that the continuous memory map suffered from in the worst-case scenario was that the activate to activate constraint on the same bank creates large gaps between the access commands. With the interleaving memory map, we are not concerned about activating the same bank repeatedly, but rather activate different banks. The constraints governing the minimum time between activates to different banks is much less strict than its same bank counterpart, therefore the number of cycles to produce the same amount of data in the worst-case is significantly less when using an interleaving pattern.

Therefore the benefits of this approach are that the latency to access a word is not dependent on the state of the SDRAM, and activate command costs can be reduced. Because this mapping makes no assumptions about the type of data being used, or about the number of requestors in the system, and for the benefits detailed above, the interleaving map has been chosen as the type of memory map to be used.

To demonstrate this benefit we examine two examples. If we compare the length of time for sending 4 read commands with a continuous memory map in the best-case scenario, compared to an interleaving memory map, we see that the continuous map produces the same amount of data with many fewer clock cycles. This is seen in Figure 4.5. This shorter pattern sequence translates to a higher bandwidth for the continuous memory map due to a higher bank efficiency, as shown in Equation (3.3).

However, in Figure 4.6 we compare the length of time for executing 4 read commands with a continuous memory map in the worst-case scenario, against an interleaving memory map, we see a much different result. The worst-case scenario occurs when requests coming into the memory controller wish to read from different rows in the same bank. As we stated in our goals for the thesis, we want to place useful bounds on worst-case bandwidth, therefore we have chosen to use the interleaving memory map, as it provides better worst-case performance.

Figure 4.5: Illustration of best-case scenario when using a continuous memory map (top) compared to an interleaving memory map (bottom)

Figure 4.6: Illustration of worst-case scenario when using a continuous memory map (top) compared to an interleaving memory map (bottom)

## 4.3 Command Generator

The command generator is responsible for producing SDRAM memory commands based on requests in the request buffer, depending on the memory map chosen. The generator may need to be aware of the current state of the SDRAM device. If a requestor is trying to read a word of data from a bank, often the row in the bank is not already in the row buffer, therefore the controller must first activate the row in the bank, and then it may send the actual read command to retrieve the data. The generator must be configured to type of SDRAM device being used, as each type requires different amounts of time between commands.

## 4.4 Types of Memory Controllers

Based on the memory controller components defined previously, this section gives an overview of the various types of memory controllers used today.

#### 4.4.1 Statically Scheduled Memory Controllers

Statically scheduled controllers work by having a predefined order of commands programmed at design time. These controllers are used in systems where there is no unpredictability in the traffic, and thus everything is static. If there is any variation in the read to write ratio of commands, or if the bandwidth requirements change, then the current schedule becomes invalid. In order to remedy this, one can consider creating a static schedule for every use case that the system may encounter, however this number may become very large. To overcome these problems, a new type of controller was developed, and we examine it in the next section.

#### 4.4.2 Dynamically Scheduled Memory Controllers

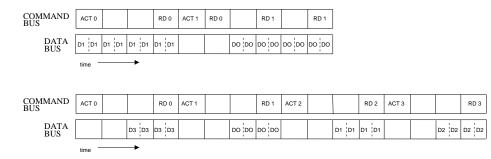

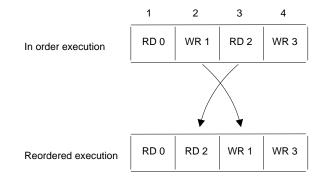

In the above section, we saw that statically scheduled controllers cannot perform well when the traffic in question varies over time. Thus, a new type of controller was invented; the dynamically scheduled memory controller. This controller works by generating commands at run time depending on requests. It then attempts to optimize the actual command schedules based on the current outstanding requests, and this can be done with command reordering [14], a self-optimizing controller [7], and other techniques [15].

Command reordering is mechanism by which a memory controller attempts to improve average-case efficiency. It can accomplish this with command grouping, where the controller groups similar commands together to reduce the number of data bus direction changes, and bank grouping, which means the controller separates requests by bank. Then, each bank determines when it should schedule an outstanding request depending on a selectable policy. Bank reordering has been shown to improve sustained bandwidth by up to 144% over a system without reordering when applied to realistic synthetic benchmarks [14]. An example of command grouping in shown in Figure 4.7. This example demonstrates how two commands can be reordered to improve efficiency. In the upper figure we see that if the controller were to execute these requests in order, that there would be 3 changes in data bus direction, whereas after commands are reordered, there is only one change in direction. This offers a significant increase in bandwidth, however, the amount of time until command 2 is executed has now been increased.

Figure 4.7: Illustration showing reordering of commands to reduce data bus direction changes. The top figure shows the requests in order, the bottom figure shows the requests reordered.

Another method of improvement mentioned above was a self-optimizing controller. During the operation of this controller, it is constantly examining the long term impacts its schedules have on memory efficiency. If it begins to see a shift in the incoming requests, it optimizes the schedules to produce the best possible patterns. It has been shown to increase the net bandwidth of a multiprocessor system by 30% over a system with in-order scheduling [7].

These optimizations can greatly increase the average-case latency and bandwidth at the cost of the worst-case latency and bandwidth. Because commands are possibly reordered during runtime, it becomes very difficult to analytically determine the absolute worst-case latency and net bandwidth. As such, simulations are the only way to try and verify if bounds are met. As a result, only ranges and averages are returned as verification for system traces that have been simulated. In a system with hard real-time deadlines this type of verification could be unacceptable, and therefore these dynamically scheduled memory controllers are not suitable for this thesis.

#### 4.4.3 Hybrid Memory Controllers

To provide useful performance to a system with variable traffic without sacrificing hard real-time requirements, a new memory controller has been proposed [2].

This controller works by combining aspects of both the statically scheduled controller and dynamically scheduled controllers. A set of groups of commands are utilized by the controller to interact with the memory. Each one of these groups of commands, referred to as a pattern, is responsible for one type of interaction. There is a read pattern, a write pattern, a read to write switching pattern, a write to read switching pattern, and a refresh pattern. These patterns are generated at design time, and their construction is governed by the constraints in the memory specification and limited by requestor requirements.

The idea that separates this controller from a statically scheduled controller, is that this controller schedules these precomputed patterns dynamically, using a predictable arbiter.

Dynamic scheduling with a predictable arbiter allows us to bound the worst-case latency, while knowing the patterns in advance lets us bound the worst-case bandwidth. Another benefit of this approach is that by placing the commands into larger groups, we simplify the amount of constraints present. The patterns generated at design time are explored in Section 5. A demonstration of the differences among the memory controllers introduced above is shown in Table 4.1.

| Controller | Commands | Arbiter | Predictability | Cost                    | Complexity |

|------------|----------|---------|----------------|-------------------------|------------|

| Dynamic    | Dynamic  | Dynamic | No             | Bad Worst-Case          | High       |

| Predator   | Static   | Dynamic | Yes            | Dependent on $e_{data}$ | Medium     |

| Static     | Static   | Static  | Yes            | Rigid Design            | Low        |

Table 4.1: Comparison of characteristics of different memory controllers.

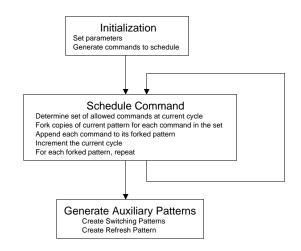

Memory patterns are sequences of SDRAM commands, and are used by the hybrid memory controller proposed in Section 4.4.3. In this section, we present an overview of the patterns, followed by descriptions of the individual patterns themselves. Later, we discuss how these patterns can be evaluated in terms of their efficiency, latency, and bandwidth.

# 5.1 Pattern Overview

Patterns provide the only mode of interaction between a memory controller and the memory itself. We have divided the types of patterns into two groups: access patterns and auxiliary patterns.

*Read patterns* and *write patterns* are grouped under access patterns as they are the only patterns that can actually access the contents of the memory. Once the access patterns have been determined, they are used to compute the lengths of the auxiliary patterns.

The remaining patterns are auxiliary patterns. These patterns consist of the *read* to write switching pattern, the write to read switching pattern, and the refresh pattern. These patterns perform more of a support role, and are responsible for giving the data bus time to switch direction, and keeping the data cells in the memory charged.

## 5.1.1 Scheduling Rules

The patterns are constructed in such a way that a read pattern may be immediately scheduled after itself. Similarly, write patterns are also constructed in such a manner. The reason this is done is to reduce the number of patterns required to interact with a memory device.

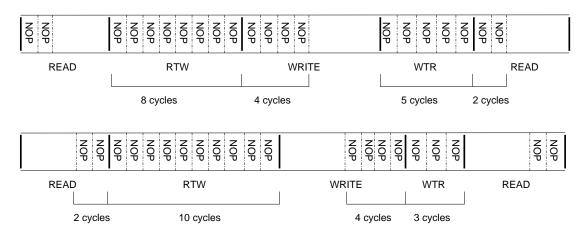

When a switch occurs from a write pattern to a read pattern, a write to read switching pattern must be executed. This provides the SDRAM with the required time to alter the direction of the data bus. Similarly, a read to write switching pattern must be executed when the memory controller wants to execute a write pattern when a read pattern has just finished. A refresh pattern may be executed after read and write patterns. Switching patterns are not required after a refresh. An example of a sequence of patterns can be observed in Figure 5.1.

|  | READ | READ | RTW | WRITE | WTR | READ | REFRESH | WRITE |  |

|--|------|------|-----|-------|-----|------|---------|-------|--|

|--|------|------|-----|-------|-----|------|---------|-------|--|

Figure 5.1: Sequence of various patterns.

## 5.2 Types of Patterns

Detailed in this section are the types of patterns used by the Predator memory controller.

### 5.2.1 Access Patterns

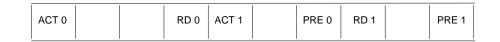

A read pattern is used to retrieve data from the SDRAM. There is one activate command per bank. Each activate is followed by *BurstCount* read commands to each bank, in an interleaved fashion. *BurstCount* is defined in Definition 5.2. Wherever there are gaps remaining, they are filled with NOP commands. Similarly, a write pattern is constructed the same way with write commands instead of read commands.

In Figures 5.2 and 5.3, we see two examples of valid patterns for a DDR2-400 SDRAM device. The definition of a valid pattern is seen in Definition 5.1.

**Definition 5.1 (Valid Pattern)** Valid patterns are defined as patterns that do not violate any of the constraint timings of a given SDRAM.

**Definition 5.2 (BurstCount)** BurstCount is the number of read or write commands per bank present in a read or write pattern.

Figure 5.2: Read pattern for DDR2-400 SDRAM. Blank schedule slots indicate NOP commands.

| ACT 0 |  | WR 0 | ACT 1 |  | WR 1 | ACT 2 |  | WR 2 | ACT 3 |    | WR 3     |

|-------|--|------|-------|--|------|-------|--|------|-------|----|----------|

|       |  |      |       |  |      |       |  |      |       | 16 | 6 Cycles |

Figure 5.3: Write pattern for DDR2-400 SDRAM.

### 5.2.2 Auxiliary Patterns

The read to write switching pattern is used to provide time to the SDRAM so that it may change the direction of its data bus. This pattern only contains NOP commands, the number of which is dependent on the required distance between a read and write command as stated by the memory specification. The write to read switching pattern is constructed in the same way, except it is used in the transition between a write pattern and a read pattern.

As a side note, sometimes this switching time may be completely mitigated depending on the SDRAM specification and the pattern chosen.

The refresh pattern contains one refresh command, along with a number of NOP commands. The number of NOP commands, and the exact location of the REF command, are governed by the read and write pattern construction.

Figure 5.4: Switching patterns being used between read and write patterns.

**Definition 5.3 (Pattern Set)** A pattern set is the collection of read, write, read to write switching, write to read switching, and refresh patterns that are generated for a particular memory specification and BurstCount.

## 5.3 Pattern Dominance

When computing the various types of efficiencies and latencies for a given pattern set, it is important to determine which sequence of patterns will produce the worst-case latency and bandwidth. There are 4 categories into which a pattern set may fall. These are, read dominance, write dominance, mix read dominance, and mix write dominance. Below, we have outlined how to calculate the different dominance types.  $t_{read}$ ,  $t_{write}$ ,  $t_{rtw}$ ,  $t_{wtr}$ , and  $t_{ref}$  refer to the amount of time taken to execute the respective pattern in a set.

### 5.3.1 Read Dominance

Read dominance is said to occur when the length of a read pattern is greater than the sum of the read to write switch, write, and write to read switch patterns. Thus, when attempting to compute the worst-case latency of a pattern, one should assume that only read patterns are being executed by the controller. An example of a read dominant pattern set is shown in Figure 5.5

$$t_{read} > t_{write} + t_{wtr} + t_{rtw}$$

$$(5.1)$$

$$READ$$

$$RTW WRITE WTR$$

Figure 5.5: Illustration of read dominance.

#### 5.3.2 Write Dominance

Write dominance is the converse of read dominance. When calculating worst-case latency or bandwidth, one should assume that only write patterns are being executed. An example of this can be seen in Figure 5.6.

$$t_{write} > t_{read} + t_{wtr} + t_{rtw}$$

$$(5.2)$$

This may be rewritten as

$$t_{read} < t_{write} - t_{wtr} - t_{rtw}$$

(5.3)

Figure 5.6: Illustration of write dominance.

### 5.3.3 Mix Dominance

When a set of patterns does not fall into the read or write dominance areas, it must fall into the mixed dominance area. This area is reached when alternating between read and write patterns provides the worst-case scenario.

$$t_{read} + t_{rtw} + t_{write} + t_{wtr} \ge 2 * t_{read} \land t_{read} + t_{rtw} + t_{write} + t_{wtr} \ge 2 * t_{write}$$

This may be rewritten as

$$t_{write} - t_{wtr} - t_{rtw} \le t_{read} \le t_{write} + t_{wtr} + t_{rtw}$$

$$(5.4)$$

Figure 5.7: Illustration of mix dominance.

Mixed dominance is further subdivided into two more areas; mixed read and mixed write dominance, in order to further simplify the calculations needed to determine worstcase latency and bandwidth. Mix read dominance means that the sum of lengths of read and write to read switch patterns is larger than the sum of write and read to write switch patterns. The bandwidth offered by a pattern set of mix read or mix write dominance does not change, as the sum of the lengths of the patterns remains constant, however the latency calculations may produce different results depending on which dominance type the pattern exhibits.

$$t_{wtr} + t_{read} \ge t_{rtw} + t_{write}$$

$$t_{read} \ge t_{write} - t_{wtr} + t_{rtw}$$

(5.5)

Mix write dominance means that the sum of write and read to write switch patterns is larger than the sum of read and write to read switch patterns.

$$t_{rtw} + t_{write} > t_{wtr} + t_{read}$$

$$t_{read} < t_{write} - t_{wtr} + t_{rtw}$$

(5.6)

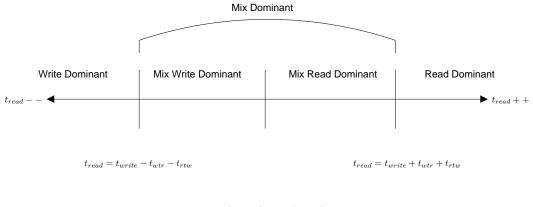

Figure 5.8 shows the range of dominance types on a line. In this figure  $t_{read}$  is scaled up and down while keeping  $t_{write}$ ,  $t_{wtr}$ , and  $t_{rtw}$  fixed.

$t_{read} = t_{write} - t_{wtr} + t_{rtw}$

Figure 5.8: Dominance scale viewed on a line.

## 5.4 Efficiency Calculations

As mentioned in Section 3, the efficiency of a memory controller is very important. It is a major component of the net bandwidth equation shown in Equation (3.5). Therefore, in order to accurately calculate the bandwidth provided by the memory controller, we need to know the efficiency values. Now that we have defined the tools used by a memory controller to interact with an SDRAM, we can precisely compute the various efficiencies. Additionally, the efficiency model of Woltjer that is used by Predator is extended to accommodate pattern sets where the read and write patterns are of different lengths. In Section 3, we concluded that it was difficult to compute some of the efficiencies at design time due to not knowing the traffic. We bypass this restriction now because we have interleaving patterns with fixed access granularity, and shift all uncertainty into data efficiency.

#### 5.4.1 Bank Efficiency

From Section 3.3, we saw that the bank efficiency was a way to incorporate the loss in cycles incurred as a result of SDRAM access time variability.

The bank efficiency is now computed as the number of cycles that there is data on the bus (*TransferCycles*), as defined in Equation (5.7), divided by a pattern length determined by the pattern set dominance type as seen in Equation (5.8). *DataRate* is the number of words per clock cycle, *BurstSize* is the number of words per read or write command, and *BurstCount* is the number of read or write bursts sent to a particular bank. The reason that we divide by the average pattern length in Equation (5.8) in the case of mix dominance is because in the worst-case we will have equal amounts of both types of patterns being executed.

$$TransferCycles = \frac{BurstCount * BurstSize * NumberOfBanks}{DataRate}$$

(5.7)

$$e_{bank} = \begin{cases} \frac{TransferCycles}{t_{read}} & \text{if read dominant} \\ \frac{TransferCycles}{t_{write}} & \text{if write dominant} \\ \frac{TransferCycles}{\frac{t_{read} + t_{write}}{2}} & \text{if mix read or mix write dominant} \end{cases}$$

(5.8)

The calculations are now possible because the addresses of requests coming into the memory controller do not affect access times. Due to the interleaving nature of our patterns, every access will activate all banks before data is read, and all banks are in an idle state when a pattern begins to execute. Thus, access times become static per pattern.

#### 5.4.2 Data Efficiency

As shown in Section 3.2, the equation for determining the data efficiency is dependent on the request size of a requestor and the granularity of the memory access pattern. Now that the read and write pattern has been defined, and considering that it is the only way in which a requestor may access data, we can compute specifically the data efficiency.

$$granularity_{pattern} = BurstCount * NumberOfBanks$$

$$*BurstSize * DataBusWidth$$

(5.9)

Therefore Equation (3.2) becomes

$$e_{data} = \frac{size_{request}}{granularity_{pattern}} \tag{5.10}$$

### 5.4.3 Switching Efficiency

When a pattern set exhibits read dominance or write dominance, it implies that the worst-case scenario occurs when only read patterns or only write patterns are being executed. This means that there will be no switches in the worst-case, and therefore the switching efficiency will be 100%.

If the pattern is mix dominant, the switching efficiency is computed as the time it takes to execute a read and write pattern divided by the time taken to execute a read, read to write switch, write, and write to read switch patterns. This is due to the fact that in the worst-case read and write patterns are alternated at every opportunity.

$$e_{switch} = \begin{cases} 1 & \text{if read or write dominant} \\ \frac{t_{read} + t_{write}}{t_{read} + t_{write} + t_{wtr} + t_{rtw}} & \text{if mix read or mix write dominant} \end{cases}$$

(5.11)

#### 5.4.4 Refresh Efficiency

In order to compute the refresh efficiency, we need to know the worst-case request time that can occur. Now that this value is easily computable, we can determine the refresh efficiency by taking the amount of time it takes for a refresh pattern to execute, and dividing it by how frequently that refresh actually occurs. All current DDR-SDRAMs have a refresh interval (tREFI) of 7800ns at normal operating temperatures. However, to compute the refresh efficiency, we need to know the worst-case request time that can occur. The reason we need to calculate LongestRequestTime is that a refresh pattern may need to be scheduled right after a read or write pattern has been scheduled. LongestRequestTime is defined to be the sum of a switching pattern and an access pattern because in the worst-case, the opposite access pattern has just been executed and thus be must switched. To make sure that the refresh interval is not violated, we rewrite the refresh interval to be LongestRequestTime nanoseconds shorter, as shown in Equation (5.12).

$$LongestRequestTime = \max(t_{read} + t_{wtr}, t_{write} + t_{rtw})$$

RefreshPeriod = tREFI - LongestRequestTime + t\_{ref} (5.12)

$$e_{refresh} = 1 - \frac{t_{ref}}{RefreshPeriod}$$

(5.13)

### 5.5 Latency Calculation

As mentioned in the problem statement in Section 1.3, we also want to guarantee a bound on worst-case latency. Now that we have precisely defined what the memory patterns are, we may now use them to analytically derive the worst-case latency.

The first latency equations that will be shown will compute the worst-case latency assuming that there are  $\alpha$  other requests interfering.

$$latency(\alpha) = \begin{cases} t_{read} * \alpha & \text{if read dominant} \\ t_{write} * \alpha & \text{if write dominant} \\ \\ \left\lceil \frac{\alpha+1}{2} \right\rceil * t_{wtr} + \left\lceil \frac{\alpha}{2} \right\rceil * t_{read} + \left\lceil \frac{\alpha}{2} \right\rceil * t_{rtw} + \left\lfloor \frac{\alpha}{2} \right\rfloor * t_{write} & \text{if mix read dominant} \\ \\ \\ \left\lceil \frac{\alpha+1}{2} \right\rceil * t_{rtw} + \left\lceil \frac{\alpha}{2} \right\rceil * t_{write} + \left\lceil \frac{\alpha}{2} \right\rceil * t_{wtr} + \left\lfloor \frac{\alpha}{2} \right\rfloor * t_{read} & \text{if mix write dominant} \\ \\ \\ (5.14) \end{cases}$$

However, the above equations assume that no refreshes will occur, and this is not a valid assumption while using DRAMs. Therefore the equations are transformed below to account for refreshes, with  $\phi$  defined in Equation (5.18) for clarity.

Equation (5.17) specifies the maximum number of refreshes that can occur with  $\alpha$  requestors interfering. It is broken up into 4 pieces as the worst-case scenario changes with dominance. Once this equation is obtained, we can multiply it with  $t_{ref}$  as shown in Equation (5.16) to determine how much time refreshes by themselves can take. We then add this to the latency calculated in Equation (5.14) to obtain the final latency equation, shown in Equation (5.15).

$$TotalLatency(\alpha) = RefreshTime(\alpha) + latency(\alpha)$$

(5.15)

$$RefreshTime(\alpha) = t_{ref} * NumberRefreshes(\alpha)$$

(5.16)

$$NumberRefreshes(\alpha) = \left\lceil \frac{latency(\alpha)}{\phi} \right\rceil$$

(5.17)

$$\phi = \begin{cases} RefreshPeriod - t_{read} & \text{if read dominant} \\ RefreshPeriod - t_{write} & \text{if write dominant} \\ RefreshPeriod - t_{read} - t_{wtr} & \text{if mix read dominant} \\ RefreshPeriod - t_{write} - t_{rtw} & \text{if mix write dominant} \end{cases}$$

(5.18)

## 5.6 Optimality

Now that we have defined how to calculate various efficiencies, latencies, and net bandwidth, we need to define what an optimal pattern set is.

**Definition 5.4 (Optimality)** An optimal pattern set for a given memory specification is the set of valid patterns that provide the maximum net bandwidth.

The reason why net bandwidth is chosen is two-fold. The first benefit of using this is that the system can support the addition of new requestors more easily, as there is more net bandwidth to distribute. Alternatively, the extra net bandwidth can be redistributed to the requestors with the idea that with more bandwidth allotted to them, they can complete their tasks sooner. In Section 6.2, we see precisely how these patterns are determined.

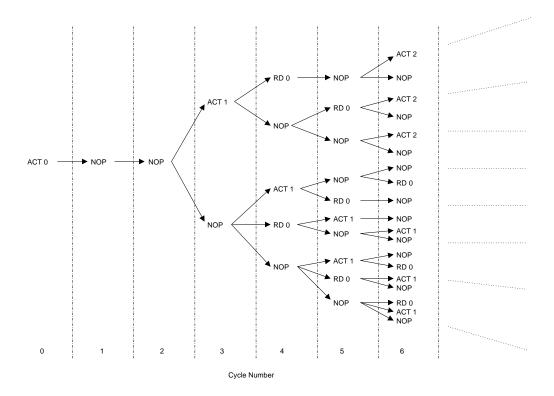

Three heuristic algorithm approaches are explored in this section: branch and bound, as-soon-as-possible scheduling (ASAP), and bank scheduling. These approaches explore the trade-offs between execution time of the algorithm and amount of net bandwidth offered by the resulting patterns. They are all heuristics as computing optimal patterns is too time intensive. The usefulness of the algorithms is measured by the following aspects.

- Speed of the algorithm

- Net bandwidth offered by the resulting patterns

# 6.1 Pattern Generation Design Decisions

When generating the patterns as shown in the following sections, we made 4 design decisions regarding pattern construction. First, we assume that shorter access patterns offer more bandwidth than longer patterns. Secondly, the algorithms will only focus on creating access patterns without regard for auxiliary patterns. Thirdly, we always place an activate command in the first pattern slot. Lastly, we let the algorithms treat all banks equally.

- 1. We justify the first decision by examining how pattern dominance is related to worst-case scenarios.