# MSc THESIS

# Performance estimation technique for optimizing and integrating IPs in MPSoCs

Anand Subhash Khot

CE-MS-2011-12

continuously increased owing to the increasing demand for high performance IPs and SoCs. However, the productivity of chip designers has not scaled up at the same rate. This has led to an enormous design productivity gap. At the same time, the increasing time-tomarket pressure and the high risk of design failure have all fostered the development of IP re-use based designs. One of the major challenges in re-using IPs is that it is difficult to configure and verify the performance of IPs/ IP subsystems after they are integrated into an existing SoC with a given infrastructure (on-chip network, memory subsystem, etc.). To overcome these challenges, we propose two performance estimation techniques that are based on high-level performance modeling of IPs and SoC infrastructure. These models capture some of their key performance characteristics (e.g. latency tolerance of IPs) and help relate the performance dependence of IPs on the service provided by the SoC infrastructure. Along with the advantage of re-using the high-level IP models in multiple SoC designs, the models allow the SoC designer to iteratively estimate the performance of a SoC over a range of IP and SoC infrastructure configurations, thereby aiding the design space exploration process. The

Over the last decade, the complexity of system-on-chips (SoCs) has

proposed performance estimation techniques are particularly useful in rapidly re-assessing the performance of all IP/ IP subsystems once they are integrated into a given SoC design. The performance estimates provided by these techniques in the early SoC design stages saves a significant portion of the precious design time. The performance estimation techniques therefore simplify the process of integrating new IPs/ IP subsystems into existing SoC designs.

# Performance estimation technique for optimizing and integrating IPs in MPSoCs

# THESIS

submitted in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

$\mathrm{in}$

# COMPUTER ENGINEERING

by

Anand Subhash Khot born in Belgaum, India

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

# Performance estimation technique for optimizing and integrating IPs in MPSoCs

## by Anand Subhash Khot

#### Abstract

ver the last decade, the complexity of system-on-chips (SoCs) has continuously increased owing to the increasing demand for high performance IPs and SoCs. However, the productivity of chip designers has not scaled up at the same rate. This has led to an enormous design productivity gap. At the same time, the increasing time-to-market pressure and the high risk of design failure have all fostered the development of IP re-use based designs. One of the major challenges in re-using IPs is that it is difficult to configure and verify the performance of IPs/ IP subsystems after they are integrated into an existing SoC with a given infrastructure (on-chip network, memory subsystem, etc.). To overcome these challenges, we propose two performance estimation techniques that are based on high-level performance modeling of IPs and SoC infrastructure. These models capture some of their key performance characteristics (e.g. latency tolerance of IPs) and help relate the performance dependence of IPs on the service provided by the SoC infrastructure. Along with the advantage of re-using the high-level IP models in multiple SoC designs, the models allow the SoC designer to iteratively estimate the performance of a SoC over a range of IP and SoC infrastructure configurations, thereby aiding the design space exploration process. The proposed performance estimation techniques are particularly useful in rapidly re-assessing the performance of all IP/ IP subsystems once they are integrated into a given SoC design. The performance estimates provided by these techniques in the early SoC design stages saves a significant portion of the precious design time. The performance estimation techniques therefore simplify the process of integrating new IPs/ IP subsystems into existing SoC designs.

| Laboratory<br>Codenumber | : |                                       |  |

|--------------------------|---|---------------------------------------|--|

| Committee Members        | : |                                       |  |

| Advisor:                 |   | Prof. Kees Goossens, ES, TU Eindhoven |  |

| Advisor:                 |   | Dr. ir. Pieter van der Wolf, Synopsys |  |

| Chairperson:             |   | Dr. ir. Sorin Cotofana, CE, TU Delft  |  |

| Member:                  |   | Dr. ir. Georgi Kuzmanov, CE, TU Delft |  |

To my parents

# Contents

| List of Figures  | vii |

|------------------|-----|

| List of Tables   | ix  |

| Acknowledgements | xi  |

| 1        | Intr | roduction                                                               | 1  |

|----------|------|-------------------------------------------------------------------------|----|

|          | 1.1  | System-on-Chip                                                          | 1  |

|          | 1.2  | SoC Design                                                              | 1  |

|          | 1.3  | IP re-use                                                               | 2  |

|          | 1.4  | Problem Statement                                                       | 3  |

|          |      | 1.4.1 IP customization and integration                                  | 3  |

|          |      | 1.4.2 Performance verification                                          | 5  |

|          | 1.5  | Aim                                                                     | 6  |

|          | 1.6  | Proposed Solution                                                       | 6  |

| <b>2</b> | Ger  | neral High level Performance Modeling                                   | 9  |

|          | 2.1  | Functional modules                                                      | 9  |

|          |      | 2.1.1 Generic architecture of IPs:                                      | 9  |

|          |      | 2.1.2 Classification of functional modules                              | 10 |

|          | 2.2  | Model for functional modules                                            | 12 |

|          |      | 2.2.1 External memory request trace                                     | 13 |

|          |      | 2.2.2 Execution behaviour of functional modules                         | 19 |

|          |      | 2.2.3 Performance impact of the SoC infrastructure                      | 19 |

|          |      | 2.2.4 Performance impact of the IPs                                     | 20 |

|          |      | 2.2.5 Total execution time $(E)$ :                                      | 21 |

|          |      | 2.2.6 No-stall interval                                                 | 22 |

|          |      | 2.2.7 Perceived latency                                                 | 22 |

|          |      | 2.2.8 Derived Benefit                                                   | 22 |

|          | 2.3  | Performance modeling of functional modules                              | 23 |

|          | 2.4  | Performance modeling of the SoC infrastructure                          | 23 |

|          | 2.5  | The complete SoC model                                                  | 24 |

|          | 2.6  | Basics of Performance Estimation                                        | 25 |

|          |      | 2.6.1 Characterization of functional modules and the SoC infrastructure | 26 |

|          |      | 2.6.2 Execution of the external memory request trace                    | 27 |

|          | 2.7  | Conclusion                                                              | 27 |

| 3            | Tra            | ce-based Performance Estimation                                 | 29        |

|--------------|----------------|-----------------------------------------------------------------|-----------|

|              | 3.1            | Trace simulator                                                 | 29        |

|              | 3.2            | Experiments based on the trace simulator                        | 29        |

|              |                | 3.2.1 Simple Blocking Processor                                 | 30        |

|              |                | 3.2.2 Experiments for split and pipelined IPs                   | 33        |

|              | 3.3            | Conclusion                                                      | 42        |

| <b>4</b>     | $\mathbf{Sim}$ | plified equation-based Performance estimation                   | <b>45</b> |

|              | 4.1            | Performance estimation using simplified equations               | 45        |

|              | 4.2            | Experiments                                                     | 46        |

|              |                | 4.2.1 Blocking IP                                               | 46        |

|              |                | 4.2.2 Split IPs                                                 | 47        |

|              |                | 4.2.3 Pipelined IPs                                             | 56        |

|              | 4.3            | Application of the performance estimation techniques            | 57        |

|              |                | 4.3.1 Performance estimation using trace simulator              | 57        |

|              |                | 4.3.2 Performance estimation using simplified equation          | 59        |

|              | 4.4            | Conclusion                                                      | 60        |

| 5            | Rela           | ated work                                                       | 61        |

| 6            | Con            | clusion and Future work                                         | 65        |

|              | 6.1            | Summary                                                         | 65        |

|              | 6.2            | Conclusion                                                      | 66        |

|              | 6.3            | Recommendations                                                 | 66        |

|              | 6.4            | Future work                                                     | 67        |

| Bi           | bliog          | graphy                                                          | 70        |

| $\mathbf{A}$ | Alg            | orithm for computing the derived benefit of external memory re- |           |

|              | que            | sts                                                             | 71        |

# List of Figures

| 1.1          | A contemporary system-on-chip (SoC)                                          | 1  |

|--------------|------------------------------------------------------------------------------|----|

| 2.1          | Examples of functional modules in SoCs                                       | 10 |

| 2.2          | Examples of functional modules in SoCs                                       | 11 |

| 2.3          | Assembly code of a task executing on the core IP                             | 16 |

| 2.4          | Memory trace resulting from executing audio application on a processor       |    |

|              | with an ideal memory subsystem                                               | 16 |

| 2.5          | Memory trace generated by the cache (assistance unit) of the functional      |    |

|              | module                                                                       | 17 |

| 2.6          | Memory trace resulting from the execution of real-time video application     |    |

|              | on a streaming graphics engine with an ideal memory subsystem                | 18 |

| 2.7          | Memory trace generated by the pre-fetcher (assistance unit) of the func-     |    |

|              | tional module                                                                | 19 |

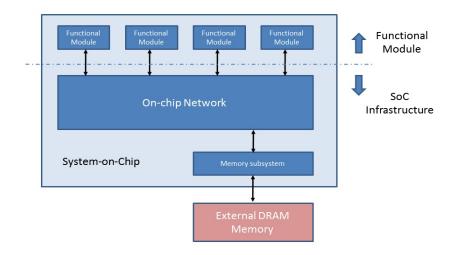

| 2.8          | System level representation of the SoC                                       | 24 |

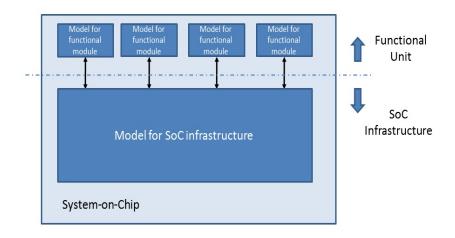

| 2.9          | Model of the complete SoC                                                    | 25 |

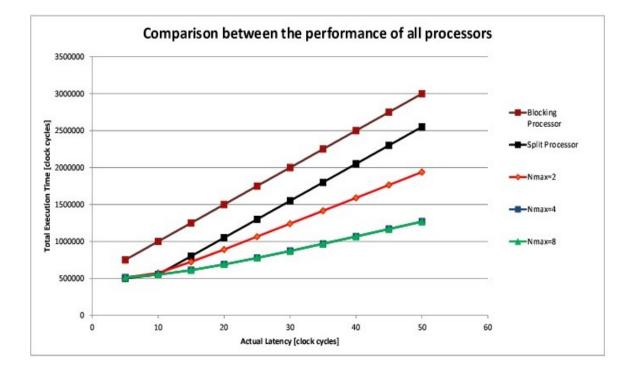

| 3.1          | Simit-ARM experiment                                                         | 32 |

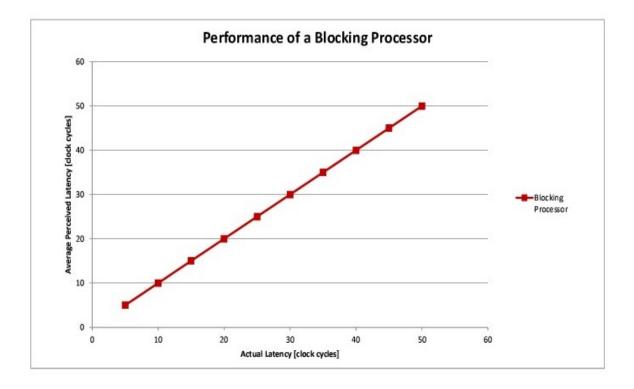

| 3.2          | Performance of blocking processor                                            | 35 |

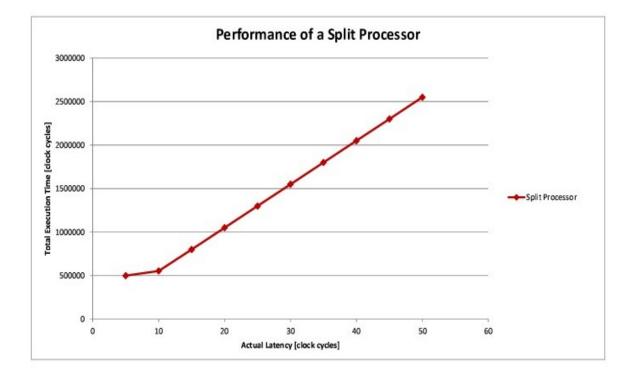

| 3.3          | Performance of split processor                                               | 36 |

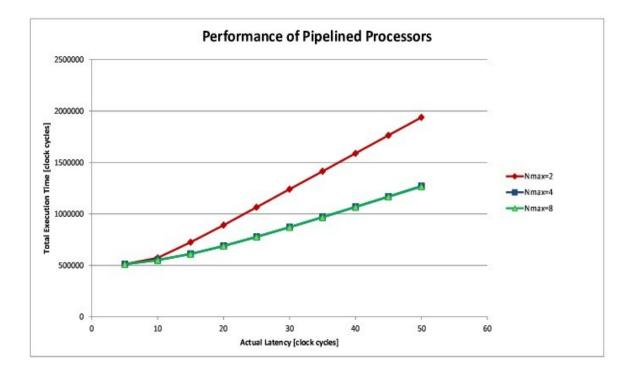

| 3.4          | Comparison of the performance of pipelined processors                        | 38 |

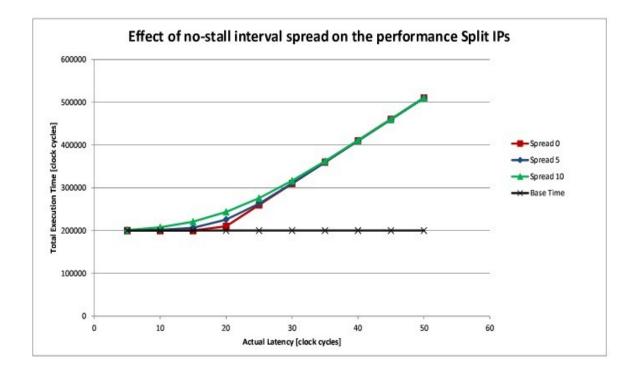

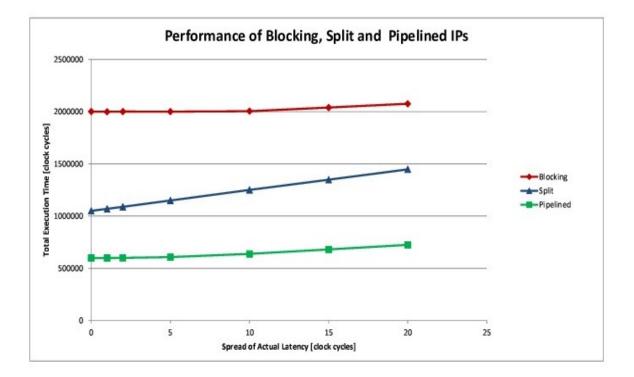

| $3.5 \\ 3.6$ | Comparison between performance of all processors                             | 39 |

|              | split/pipelined IPs                                                          | 41 |

| 3.7          | Effect of the spread in actual latency on the performance of blocking, split |    |

|              | and pipelined IPs                                                            | 43 |

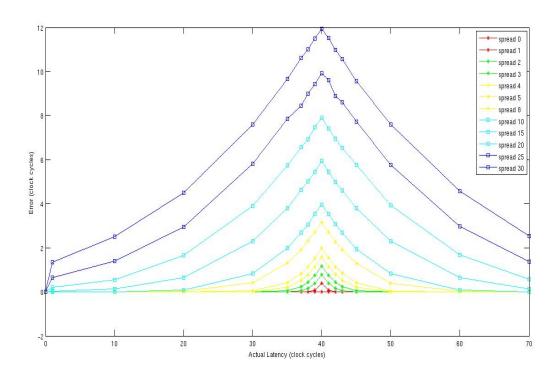

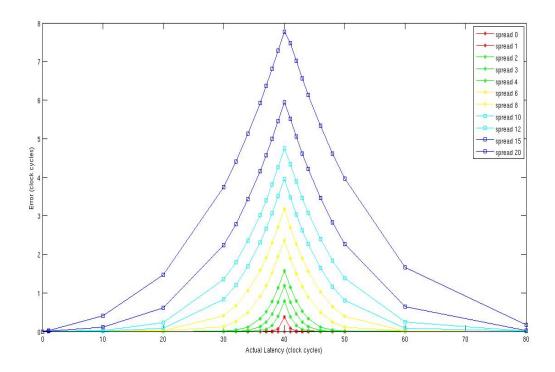

| 4.1          | Error plot for the simulation and simplified equation-based technique        | 48 |

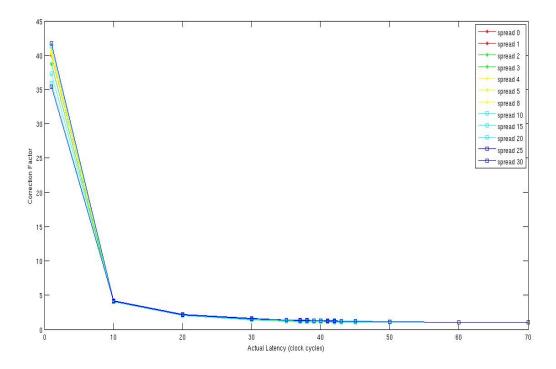

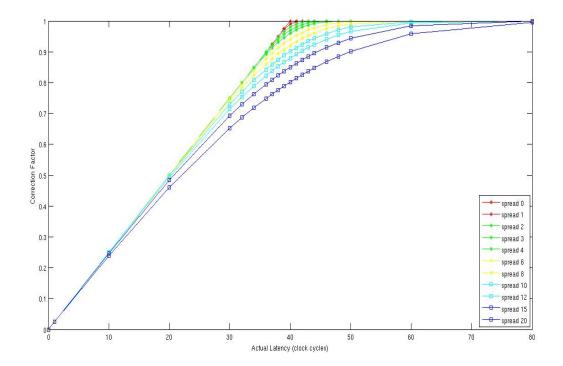

| 4.2          | Correction factor plot for computing the equivalent actual latency           | 50 |

| 4.3          | Error plot for the simulation and simplified equation-based technique        | 52 |

| 4.4          | Correction factor plot for computing the equivalent no-stall interval        | 54 |

|              |                                                                              |    |

# List of Tables

| 2.1 | Classification of functional modules                                        | 12 |

|-----|-----------------------------------------------------------------------------|----|

| 2.2 | Semantics for specifying $RD$ and $CD$                                      | 15 |

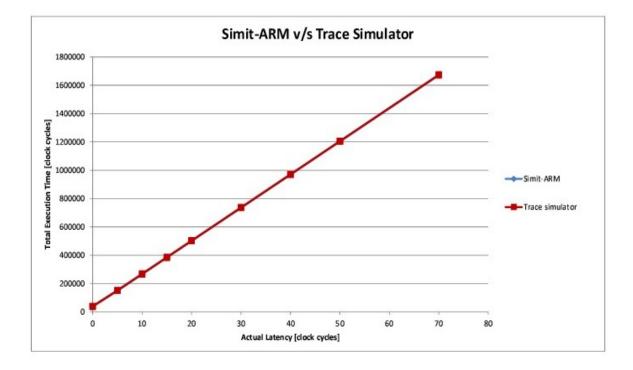

| 3.1 | Simit-ARM v/s Trace simulator results                                       | 31 |

| 3.2 | Blocking processor results                                                  | 34 |

| 3.3 | Split processor results                                                     | 36 |

| 3.4 | Pipelined processor results                                                 | 37 |

| 4.1 | Comparison between the results of the trace-based and the equation-based    |    |

|     | performance estimation techniques for blocking IPs                          | 46 |

| 4.2 | Comparison between the performance results when there is no spread in       |    |

|     | the actual latency and the no-stall interval values                         | 47 |

| 4.3 | Comparison between the results of the trace-based technique and the         |    |

|     | equation-based estimation technique for pipelined IPs                       | 56 |

| 4.4 | Performance estimation results of a DSP $(N_{max} = 4)$ executing a typical |    |

|     | audio decoder application trace                                             | 58 |

| 4.5 | Performance estimation results of a video IP $(N_{max} = 4)$ executing a    |    |

|     | typical video application trace.                                            | 59 |

# Acknowledgements

Firstly, I would like to thank Prof. Kees Goossens and Dr. Pieter van der Wolf for giving me the opportunity to conduct my MSc thesis at Synopsys under their guidance and mentorship. I am grateful for Prof. Goossens's reviews, suggestions for improvements and expert guidance throughout the thesis. I am equally grateful to Pieter for his encouragement, valuable advice and supervision at Synopsys. I would like to express my deepest gratitude to Dr. Benny Akesson (Post. Doc at TU, Eindhoven) for his suggestions and thorough review of my work. I would specially like to thank Prof. Sorin Cotofana for accepting to supervise my thesis from Delft. I would also like to thank Prof. Georgi Kuzmanov for accepting to judge my thesis defense. I am grateful to the staff of Synopsys and the *Memory Team* at TU Eindhoven, especially Firew, Sven, Tim, Karthik, Manil and Davit for creating a pleasant work environment.

Finally, I would like to thank my parents and my sister for their love, care and support. Last but not the least, I would like to thank my friends in the Netherlands, especially my flatmates in Delft and Eindhoven, for making the last 2 years special in my life.

Anand Subhash Khot Delft, The Netherlands June 23, 2011

# 1

# 1.1 System-on-Chip

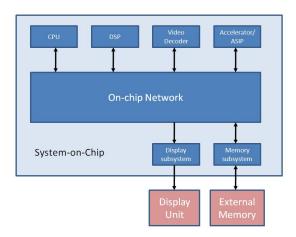

System-on-Chip (SoC) refers to the technology of integrating all components of an electronic system into a single integrated circuit. Figure 1.1 depicts a system level representation of a typical SoC. It can be observed from Figure 1.1 that a contemporary system-on-chip contains various intellectual property (IP) elements such as processing cores (e.g. ARM, MIPS), DSPs, video engines, on-chip network, audio/video subsystem, memory subsystem etc., along with analog and RF components such as PLLs, ADCs, wireless transceivers, data converters etc. IPs such as processors, DSPs and other processing engines execute the associated software to provide the intended functionality. Thus, both the hardware (IPs) and the associated software are an integral part of a system-on-chip.

Figure 1.1: A contemporary system-on-chip (SoC)

# 1.2 SoC Design

Over the last several years, SoCs have become increasingly complex. This is primarily because of the increasing number of multimedia and real time applications supported by modern day SoCs. Due to these applications, the demand for high performance IPs and SoCs has increased. Consequently the number and types of IPs developed to execute these applications have increased over the years.

However, in spite of the ever-increasing growth in the demand for advanced SoCs and the semiconductor process technology, the productivity of chip designers has not scaled up at the same rate. Over the last decade, the number of raw transistors increased at 58% per year (according to Moore's law), whereas the capability of chip designers to design them increased only at a rate of 20% per year, thereby creating an enormous design productivity gap [9]. The design productivity gap is predicted to further widen in the coming future, suggesting that the effort required to design complex chips will only increase. Also, the high cost associated with a design re-spin makes it inevitable for SoC designers to be 'first time right' with each and every SoC design. Thus, the increasing design productivity gap and the high risk of failure associated with SoC designs are the two main SoC design challenges. Along with this, SoC designers are also faced with the challenge of finding the right balance between the power, area, performance, cost (in dollars) and time-to-market constraints of modern SoCs. Due to all these factors, designing next generation SoCs has become extremely challenging and time consuming.

To address the issues of design productivity and design verification, several approaches have been developed. One approach is to develop new design methodologies and tools which allow designers to abstract the design at a higher level, thereby simplifying the design process [2, 6]. It mainly addresses the *design complexity* issues of SoC design. These methodologies and tools help raise the abstraction level at which SoCs are designed and thus, help designers build larger and more complex systems. Some of the design tools are equipped with fast simulators and formal verification techniques to improve design verification and thus, reduce the risk of design failures.

Another approach is to encourage and maximize IP re-use [3, 16, 17], which allows large SoC designs to be partitioned into smaller IP subsystems with specific, well-defined functionality. The reuse of qualified, pre-verified IPs in multiple SoC designs minimizes the risk of design failures and reduces the time-to-market and the high NRE cost associated with SoC designs. To summarize, IP re-use offers the following advantages:

- 1. Reduced time-to-market.

- 2. Reduced NRE cost.

- 3. Reduced risk of design failures.

- 4. Simplified design analysis and customization.

Over the last couple of decades, the market dynamics, the increasing SoC complexity and the time-to-market pressures have all led to the adoption and development of IP re-use based designs.

# 1.3 IP re-use

In general, IP re-use refers to the concept of directly using an IP or an IP subsystem from an existing SoC design. Such re-use of IPs is commonly found within the design groups of a semiconductor company [17]. The IP re-use based design methodology is particularly useful in rapidly evolving and highly competitive markets (such as mobile phones, consumer electronics, etc.), where the next generation SoCs are not designed from scratch, but are built by re-using a considerable portion of an existing SoC. SoC design based on IP re-use typically involves starting the design process with an existing SoC and then, adding/replacing new IP subsystems as per the design requirements. In case the required IPs/ IP subsystems are not available with the design house, they are directly purchased from third party IP vendors [16]. The IP subsystems sold by the IP vendors are pre-verified for functional correctness and support industry standard interfaces (AHB, AXI, etc.), such that they can be integrated easily into custom SoC designs. Since the IP subsystems provide some commonly required functionality, they are generic enough to allow some of the design parameters (e.g. size of data buffers, etc.) to be tweaked and reconfigured as per the performance requirements of individual SoC designs. In this thesis, we consider that the on-chip network, the memory subsystem and the external DRAM memory together form the common, shared *SoC infrastructure* that is used by all IPs/ IP subsystems.

The task of the SoC designer is to verify if the newly added IP/ IP subsystem (with a given configuration) performs as expected when it is coupled to the shared SoC infrastructure. This may require exploring the different possible configurations of the IPs/ IP subsystems and the SoC infrastructure such that they fulfill all the performance requirements of real-time applications. Also, the addition/replacement of an IP/ IP subsystem may invalidate the performance guarantees of other IPs/ IP subsystems of the original SoC. Therefore, it is crucial to ensure that all IPs/ IP subsystems of the original SoC still perform as expected even after the integration of new IP/ IP subsystems.

Thus, as explained above, there are a number of challenges involved in adopting the IP re-use based design methodology. To summarize, it is extremely tedious and time consuming to customize (through configuration) both the IPs and the SoC infrastructure such that they fulfil their performance requirements. Also, the system level performance verification of IPs and SoC infrastructure every time a new IP/ IP subsystem is added to an existing SoC design consumes a significant portion of the precious design time. Thus, rapid customization, integration and performance verification of IPs and the supporting SoC infrastructure are the key challenges in simplifying and enhancing the IP re-use based design methodology, which in turn, increases design productivity and minimizes time to market and the risk of design failure.

# 1.4 Problem Statement

In this thesis, we focus on IP re-use based designs (explained in the Section 1.3) and investigate in detail, the following two critical design challenges:

- 1. IP customization and integration

- 2. Performance verification

## 1.4.1 IP customization and integration

In the context of this work, we use the term *IP customization and integration* to denote the challenges involved in customizing both the IP/ IP subsystems and the supporting infrastructure of a given SoC design. As explained previously, SoC designers typically reuse existing SoC designs and hence, do not need to select the IPs or the SoC infrastructure per se. However, SoC designers often need to tweak the IP/ IP subsystems to suit a given application [19]. At the same time, they need to appropriately dimension the SoC infrastructure such that it successfully supports the performance requirements of all IP/ IP subsystems. The key questions which we specifically try to answer in this thesis are as follows:

- 1. Does an IP/ IP subsystem satisfy all the performance requirements of the application after it is integrated into a SoC with a given infrastructure? If not, can they be reconfigured to achieve the desired level of performance?

- 2. If a given IP/ SoC infrastructure does satisfy all the performance requirements, is there any headroom available to optimize it further?

- 3. In the case of pipelined multi-threaded IPs, how many outstanding memory requests should it ideally support in order to satisfy the performance requirements of all real time functions it executes?

- 4. In the case of IPs employing an advanced pre-fetching cache, how large should the pre-fetch data buffers be in order to allow sufficient pre-fetching of the necessary data, thereby fulfilling all the performance requirements of the IP and the application?

- 5. Given a SoC infrastructure, how do we configure it such that all IPs/ IP subsystems meet their performance requirements? The configuration of the SoC infrastructure typically involves configuring the network topology, the memory controller arbitration technique, etc.

In this thesis, we consider that one of the key concerns while answering the above questions, is to satisfy the performance requirements of all IPs/ IP subsystems sharing the SoC infrastructure. Although the performance requirements of the IP/ IP subsystems are determined by a variety of factors such as the net available bandwidth, the service latency of external memory requests, etc., in this thesis, we associate the performance of an IP/ IP subsystem with its *latency tolerance* and *latency criticality*. Latency tolerance and latency criticality are defined as follows:

#### Latency Tolerance

Latency tolerance of an IP/ IP subsystem is the ability of the IP to continue execution of the application code after issuing a memory request, until it finally stalls for the requested data. An IP/ IP subsystem which is not latency tolerant is termed as *latency sensitive* and vice versa.

#### Latency Criticality

Latency criticality of an IP/ IP subsystem is a measure of the severity of stalling the IP, with respect to the overall functionality of the application or the SoC. An IP/ IP subsystem which is not latency critical is termed as *latency non-critical* and vice versa.

Latency criticality and latency tolerance are orthogonal properties of an IP/ IP subsystem. It can be seen from Table 2.1 that is it possible to classify all IPs/ IP subsystems into the four possible combinations of latency tolerance and latency criticality. The concept of latency tolerance and latency criticality of IPs/ IP subsystems allows us to relate the performance of IPs with the service latency of the SoC infrastructure.

## 1.4.2 Performance verification

In the context of this work, we use the term *performance verification* to denote the process of performing system level performance verification of the entire SoC every time a new IP/ IP subsystem is added to the original SoC. Performance verification is a tedious and time consuming task, especially if the SoC designer undertakes design space exploration to find the right configuration of the IP/ IP subsystem or the SoC infrastructure. With respect to performance verification, we try to address the following key concerns:

- 1. Does a given IP/ IP subsystem (with specific configuration) satisfy all the performance requirements of the application when it is coupled to a SoC infrastructure (with specific configuration)?

- 2. Does addition of an IP/ IP subsystem invalidate the performance guarantees of other IPs/ IP subsystems already integrated into the SoC? Do all IPs/ IP subsystems still perform as expected?

These questions are crucial for the success of the SoC implementation. While re-using a considerable portion of an existing SoC design, the inclusion/replacement of a new IP/ IP subsystem should not degrade the performance of the other IP/ IP subsystems that share the common SoC infrastructure (i.e. NoC, memory subsystem, external DRAM memory). Thus, system level verification is necessary to verify whether the performance of all IPs/ IP subsystems are within their expected bounds after they are all integrated into the SoC.

Currently, performance verification is performed either by using cycle-accurate simulators/emulators [14, 10, 21] or by using analytical verification techniques[18, 12]. Simulation based verification is performed for the entire system, from processors/IPs to the on-chip network to the memory subsystem, which requires their HDL/ system-C models along with the entire application code. Furthermore, simulating the entire application using the IP's HDL/system-C model or an instruction set simulator, for a variety of different IP and SoC infrastructure configurations is extremely slow. On the other hand, analytical verification is fast, but relies on high level models that lack accuracy. Sometimes, analytical verification is performed using worst-case assumptions which works well with real time applications, but is not sufficiently realistic for soft/non real-time applications.

While integrating and optimizing IPs, designers often rely on past experiences and performance specifications of IPs/ SoC infrastructure to select and configure them. Often these IPs are over-dimensioned (by compromising on the bill of materials) to allow some headroom and thus, ensure performance guarantees. Even with over-dimensioning of the IPs/ SoC infrastructure, the performance guarantees need to be verified for every change in the design. The fundamental issue behind all these challenges is the lack of performance estimation techniques that would allow SoC designers to rapidly select, configure and verify the performance of IPs and SoC infrastructure.

# 1.5 Aim

The aim of this thesis is to solve the challenges encountered in the integration, customization and system level performance verification of IPs and SoC infrastructure after they are integrated into a system-on-chip. One of the key challenges in successfully verifying the performance of an IP lies in our ability to characterize the IP by its latency tolerance and latency criticality. The thesis thus, aims to provide high level performance models which capture the latency tolerance and latency criticality of IPs, along with their interaction with the SoC infrastructure. The high level performance models allow rapid and accurate performance estimation of IPs and the SoC infrastructure. Any change in the configuration of the IPs and the SoC infrastructure is reflected in the model parameters, thereby allowing the SoC designer to perform rapid system-level verification of the entire SoC for a range of IP and SoC infrastructure configurations.

# 1.6 Proposed Solution

In this thesis, we propose two performance estimation techniques that allow rapid customization, integration and verification of IPs and the supporting SoC infrastructure. The performance estimation techniques are based on abstracting the IPs/ IP subsystems and the SoC infrastructure to their high level performance models. These performance models capture the key performance characteristics of IPs/ IP subsystems, such as their latency tolerance and latency criticality.

The latency tolerance of an IP is determined by analyzing the trace of external memory requests issued by that IP to the SoC infrastructure. Application developers generally provide a set of worst-case external memory request traces as a means for SoC designers to verify the performance of IPs for the worst-case application execution behaviour. In case the worst-case external memory request traces are not available, they can be easily extracted from the actual execution of the application code on the respective IPs/ IP subsystems. We choose to characterize the IPs/ IP subsystems using their external memory request traces since trace analysis is simple, quick and computationally cheap. Also, the characterization of IPs/ IP subsystems, once performed, can be re-used for customizing and integrating the respective IPs/ IP subsystems in all subsequent SoC designs.

The proposed performance estimation technique allows SoC designers to verify the performance of the SoC by either using an accurate trace simulator or a set of simplified equations utilizing average values. We call these performance estimation techniques as trace-based performance estimation and simplified equation-based performance estimation, respectively. Both these performance estimation techniques are applied to the SoC design after all IPs and the SoC infrastructure are abstracted to their simplified high-level performance models. The trace simulator performs cycle accurate performance estimation

tion by analyzing the memory request trace on a request-by-request basis, whereas the equation-based estimation technique estimates the performance of the entire SoC by using simple performance values. Both these performance estimation techniques allow rapid system-level performance estimation of the SoC in the early stages of SoC design.

Since the high-level performance models capture the key performance characteristics of the IP/ IP subsystems and the SoC infrastructure, any change in the configuration of the IP/ IP subsystem or the SoC infrastructure is reflected in the performance model also. Thus, by using the performance model, SoC designers can rapidly iterate over several IP and SoC infrastructure configurations to perform rapid design space exploration. Also, since the performance model allows SoC designers to quantify the tolerance of IPs, they can utilize any available headroom while configuring the IP or the SoC infrastructure.

#### Organization

The rest of the thesis is organized as follows. Chapter 2 introduces the high-level performance models for IPs and the SoC infrastructure. It briefly explains the basics of performance estimation and introduces the two performance estimation techniques. Chapter 3 presents the trace-based performance estimation technique and illustrates several experiments verifying the approach. Chapter 4 deals with the simplified equation-based performance estimation technique. The chapter provides thorough explanation of the approach, followed by experiments confirming its validity. Later the two performance estimation techniques are applied for verifying and integrating IP/ IP subsystems commonly found in real-life SoC designs. Chapter 5 presents the related work and highlights the differentiated solution offered by this thesis. Finally, chapter 6 summarizes the conclusions of the thesis, proposes several recommendations on using the performance estimation techniques and lastly, presents the possible future work.

In Chapter 1, we discussed the various challenges associated with SoC design, especially from the IP re-use point of view. As a solution to the various challenges encountered in the customization, integration and verification of IPs in complex SoCs, we propose two novel performance estimation techniques. The goal of performance estimation is to instill confidence regarding the performance of an IP/ IP subsystem in co-ordination with a given SoC infrastructure early in the design phase. The proposed performance estimation techniques are based on the high-level performance models of IP/ IP subsystems and the SoC infrastructure. The performance models capture the execution behaviour of IP/ IP subsystems and the SoC infrastructure at a higher abstraction level. In this chapter, we study the performance models for IP/ IP subsystems and the SoC infrastructure.

# 2.1 Functional modules

The functionality of a typical SoC is achieved by executing a set of applications on a variety of IPs. In the context of this work, we consider that an application is made up of a number of functions, each of which is mapped to an IP. A function mapped to an IP constitutes a *functional module*. Each functional module performs a specific, well-defined function of the application and in most cases, interacts with other SoC elements such as the shared DRAM memory via the shared on-chip network. Henceforth, we use the term *functional module* to denote the combination of hardware (IP/ IP subsystem) and the associated software, whereas the term *IP/ IP subsystem* is used to specifically denote the hardware component of the functional module. We consider that the on-chip network, the shared memory subsystem and the external DRAM memory together constitute the *SoC infrastructure*.

# 2.1.1 Generic architecture of IPs:

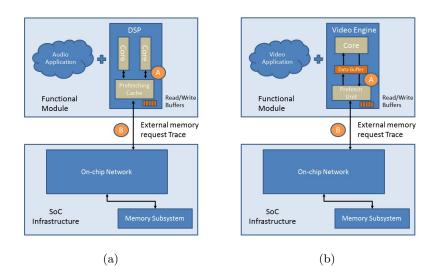

Each IP (such as CPUs, GPUs, etc.) which constitutes a functional module, consists of a core, an assistance unit and read/write buffers. The core of an IP executes the given application code and is responsible for the actual data processing. The assistance unit of an IP, such as the on-chip cache, etc., assists the IP core(s) by providing them with the necessary data. If the IP is provided with an on-chip cache, all read/write requests issued by the core are catered by the cache itself. In case the requested data is not available in the cache, external memory requests are issued to the SoC infrastructure. Similarly, if the IP is provided with an advanced pre-fetching cache, the core collects the pre-fetched data directly from the on-chip pre-fetch data buffers. In this case, the pre-fetching cache of the IP issues all external memory requests (in advance) to the SoC infrastructure. The ability of the IPs to issue multiple outstanding read/write requests to the off-chip

Figure 2.1: Examples of functional modules in SoCs

DRAM memory is directly dependent on the number of read/write buffers available in the IP.

# 2.1.2 Classification of functional modules

Functional modules can be characterized using a range of different parameters. However, as explained in Chapter 1, we characterize the functional modules by their latency tolerance and latency criticality. Based on their latency tolerance and latency criticality, functional modules can be classified into four categories as shown in Table 2.1. Given below are four functional modules that are commonly found in modern day SoCs. Each functional module belongs to one of the four functional module categories.

#### **Basic CPU**

A processor executing general purpose applications and assisted by a cache is shown in Figure 2.1(a). This functional module is latency sensitive since the processor stalls if its external memory requests are not served within a few (typically 3-4) clock cycles, thereby drastically reducing its performance. However, the functional module is latency non-critical since the consequences of stalling the processor while it executes general purpose applications are not severe with respect to the overall functionality of the SoC.

## Pre-fetching CPU

An advanced processor executing general purpose applications and assisted by an advanced pre-fetching cache is shown in Figure 2.1(b). In this example, the functional module has higher latency tolerance than the basic CPU (i.e it can tolerate a higher SoC infrastructure service latency before it stalls). This is mostly because of the advanced pre-fetching capability of the cache, which starts prefetching the unavailable data as soon as it detects a pattern in the addresses of the

Figure 2.2: Examples of functional modules in SoCs

issued memory requests. Again, the functional module is latency non-critical due to the nature of the general purpose applications that it executes.

# DSP

A digital signal processor (DSP) executing hard real-time audio applications is shown in Figure 2.2(a). In this example, the functional module is latency sensitive and extremely latency critical, since missing audio sample deadlines leads to quick deterioration of the audio output which is unacceptable. In modern DSPs, caches and/or pre-fetch units are employed to take advantage of the streaming nature of audio applications. However, the code structure of audio applications is such that there are few opportunities to exploit memory level parallelism, thereby making these IPs latency sensitive.

#### Video Engine

A streaming video engine/ video decoder executing real-time video applications and assisted by a pre-fetch unit is shown in Figure 2.2(b). Both the streaming video engine and the video decoder exhibit high latency tolerance, but at the same time, are latency critical. Streaming video engines issue memory requests with a predictable address pattern, whereas the addresses of the requests issued by a typical video decoder are more random in nature. However, numerous algorithmic optimizations are performed on the decoding application, thereby allowing the decoder IP to successfully hide a large part of the external memory related latency. This makes the decoder IP latency tolerant. Similar to the audio applications, video applications also stream data from the external memory in a regular and predictable manner. Thus, a pre-fetch unit is employed to pre-fetch and store the required data in large data buffers. Missing a few external memory request deadlines for both, the streaming video IP and the video decoder IP is acceptable as long as the collective deadline for a set of requests is met in time. Missing the collective deadline could result in dead pixels at the video output which is unacceptable from the performance point of view.

Latency Tolerant Latency Sensitive DSP Latency Critical Video Engine Pre-fetching CPU Latency Non-critical Basic CPU

Table 2.1: Classification of functional modules

#### Model for functional modules 2.2

The functional module, as the name suggests, performs a specific, well-defined function. It is essentially made up of IPs that execute specific function(s) on their core(s). At the lowest abstraction level, functions are made up of simple instructions such as add/subtract/multiply (data processing), do-while/if-else/jump (flow control) and load/store (data movement).

Data processing and flow control instructions manipulate the application data and provide the intended functionality of the application. On the other hand, data movement instructions, such as the load/store instructions, help move the application data to and from the memory. The execution of the data movement instructions results into memory requests being issued by the core of the IP to the assistance unit. The core translates the load and store instructions to issue read and write memory requests respectively.

The data processing and flow control instructions are typically executed in fixed number of clock cycles. However, data movement instructions require variable number of clock cycles depending on where the required data is stored. If the requested data is available with the assistance unit of the IP, the request is served within a few clock cycles. However, when the requested data is not available with the assistance unit, it (assistance unit) issues multiple external DRAM memory requests to the SoC infrastructure. The number of clock cycles required to retrieve the data from the external off-chip memory then depends on the service latency of the SoC infrastructure.

The performance of a functional module is directly dependent on the timely availability of the necessary data. If the SoC infrastructure takes a long time to fetch the necessary data from the external DRAM memory, the core of the IP could stall while waiting for the necessary data. The execution behaviour of the functional modules is therefore directly dependent on how external memory requests are served by the SoC infrastructure. Thus, the performance model for the functional modules captures both the execution behaviour and the performance dependence of the functional modules on the service provided by the SoC infrastructure.

Since we are primarily interested in the interaction of the functional module and the SoC infrastructure, we can abstract the execution of application code to the execution of the external memory request trace. As a result, we can model the execution behaviour of the functional modules by modeling the execution of the external memory request trace, as explained in the next subsection.

#### 2.2.1 External memory request trace

The external memory requests issued by a functional module constitute the *memory* request trace. The memory request trace is derived from the actual execution of the application code on an IP which is coupled to an ideal SoC infrastructure. Since the application code typically involves complex conditional and unconditional branching, each of which generates a unique external memory trace, we assume that a given trace is derived from the actual execution of the application code (with a specific user input data set) on the given IP. The ideal SoC infrastructure is made up of a zero latency memory subsystem (including the DRAM memory) and a zero latency on-chip network. This assumption is essential since the issuance of an external memory request directly depends on the service provided by the SoC infrastructure to the previous requests. The assumption guarantees generation of a unique external memory trace for a give application code executing on an IP and decouples the SoC infrastructure from the characterization of the functional module. Along with the application code, the hardware capabilities of the IP, especially its ability to pipeline multiple memory requests, directly influences the issuance of memory requests and hence the external memory request trace. Based on their ability to pipeline external memory requests, the IPs can be classified as:

## **Blocking IP**

IPs which stall immediately after issuing a memory request are termed as blocking IPs. A blocking IP can issue a maximum of one outstanding memory request  $(N_{max})$ .

# Split IP

An IP is classified as a split IP if, unlike a blocking IP, it can proceed with further execution even after issuing a memory request. The split IP does not stall for the response of the issued request until it (response) is required by an instruction. The maximum number of outstanding requests  $(N_{max})$  supported by a split IP is equal to one.

## Pipelined IP $(N_{max})$

An IP is classified as a pipelined IP if it can issue multiple outstanding requests without stalling for the response of previously issued requests, unless an explicit dependence exists in the application code. A pipelined IP is, by definition, also split. The maximum number of outstanding requests  $(N_{max})$  supported by a pipelined IP is called as its *pipeline depth* and is always greater than one.

Thus, the actual execution of the application code on a given IP coupled to an ideal SoC infrastructure and the hardware capabilities of the IP together determine the external memory request trace.

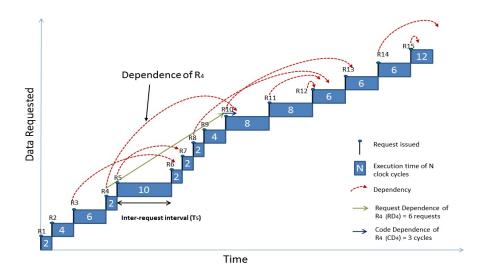

## 2.2.1.1 Specification of the Trace

A trace is primarily defined by the *inter-request intervals* of the external memory requests. The inter-request interval indicates the temporal distribution of all external memory requests issued by the functional module. Since the trace is essentially derived from the execution of the application code, the inter-request interval indicates the number of clock cycles consumed by the data processing and flow-control instructions.

The trace can additionally, but not necessarily, specify the dependencies associated with memory requests. In the context of this work, we consider two dependencies, namely the *request dependence* and the *code dependence*. Request dependence exists between two memory requests, whereas code dependence exists between a request and a non memory movement instruction of the application. The inter-request interval and the request/code dependencies, which characterize and uniquely define a given trace, can be represented using different semantics. The semantics chosen to express these phenomena should allow their easy representation and manipulation. At the same time, they should express each of the phenomenon precisely without any contradictions or ambiguity. In our model, a memory request trace is completely specified with the following parameters:

#### Inter-request interval (T)

The inter-request interval  $(T_i)$  of request  $R_i$  is defined as the number of clock cycles required by the functional module to issue request  $R_{i+1}$  after request  $R_i$  has been issued, with the assumption that all requests are completely independent and served instantaneously by an ideal (zero latency) SoC infrastructure.

#### Request dependence (RD)

A request  $R_i$  has a request dependence associated with it, if a future request, say  $R_j$  (j > i) cannot be issued until the response for request  $R_i$  has been successfully received. The request dependence of a request  $R_i$ , i.e  $RD_i$ , specifies the number of requests which can be issued after issuing request  $R_i$ , without the need to wait for the response of request  $R_i$  to have been successfully received. In other words, it specifies the number of requests which can be issued after issuing the request  $R_i$ , such that it is guaranteed the core of the IP will not stall until the issuance of  $RD_i$  further requests. The functional module could however, stall before issuing these  $RD_i$  number of requests due to dependencies of other requests or the hardware limitation of the IP, but it is guaranteed that the functional module will never stall due to the request  $R_i$  itself. In our model, the request dependence  $(RD_i)$  of a request  $R_i$  is upper bounded by the hardware capability of the IP to issue a maximum of  $N_{max}$  outstanding requests, i.e  $RD_i < N_{max}$ . If the request dependence associated with request  $R_i$  is ignored and the request is considered as an independent request.

#### Code dependence (CD)

A request  $R_i$  has a code dependence associated with it, if a particular non memory movement instruction (such as add/subtract/if-else) cannot be executed until the response of request  $R_i$  is successfully received. This is observed in scenarios where the critical instruction requires the data returned by request  $R_i$  to perform the necessary data manipulation or take the appropriate control decision.

The code dependence of request  $R_i$ , i.e  $CD_i$ , specifies the number of clock cycles that the core of the functional module can execute after having issued  $RD_i$  further

requests, before it stalls for the requested data. The code dependence of a request  $R_i$  is thus bounded by the inter-request interval of request  $R_{(i+RD_i)}$ , which is  $T_{(i+RD_i)}$ .

A trace of size N can be exactly described by specifying three vectors, as shown in Equation 2.1

$$Trace(N) = \begin{cases} \text{Inter-request interval } [T_i] & \forall i \in [1, N], T_i \in [1, \infty] \\ \text{Request dependence } [RD_i] & \forall i \in [1, N], RD_i \in [-1, N_{max} - 1] \\ \text{Code dependence } [CD_i] & \forall i \in [1, N], CD_i \in [-1, T_{(i+RD_i)} - 1] \\ \end{cases}$$

(2.1)

Along with the above definitions, the specification of request dependence (RD) and code dependence (CD) depend on the type of the IP and follow the semantics given in Table 2.2.

| Table 2.2. Demantics for specifying $ILD$ and $CD$ |                    |                          |  |

|----------------------------------------------------|--------------------|--------------------------|--|

| Request characteristic                             | $RD_i$             | $CD_i$                   |  |

| Independent $R_i$                                  | -1                 | -1                       |  |

| $R_j$ depends on $R_i$                             | (j-i-1)            | $T_{(j-1)} - 1$          |  |

| $R_i$ on blocking IP                               | 0                  | 0                        |  |

| $R_i$ on split IP                                  | 0                  | $[-1, T_i - 1]$          |  |

| $R_i$ on pipelined IP                              | $[0, N_{max} - 1]$ | $[-1, T_{(i+RD_i)} - 1]$ |  |

Table 2.2: Semantics for specifying RD and CD

### 2.2.1.2 Sample Traces

In this subsection, we examine a few traces typically generated by the following functional modules:

- 1. A processor executing a general purpose application (Figure 2.1(a))

- 2. A streaming video engine executing a real-time video application (Figure 2.2(b))

These examples illustrate how the execution of application code generates the memory request traces and how the dependencies within the application code get transferred to the memory request traces. The examples show how different memory request traces exist at different points within the SoC and how they are correlated to each other. Using these examples, we also highlight the specific memory request trace that we analyze while characterizing the functional modules.

## 2.2.1.3 A processor executing a general purpose application

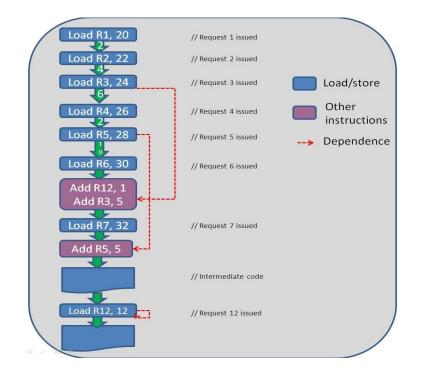

Figure 2.3 presents a sample general purpose application code written in assembly language. Figure 2.4 shows the trace derived from the execution of the above application code on a simple processor employing a simple, conventional cache. It presents the trace

Figure 2.3: Assembly code of a task executing on the core IP.

Figure 2.4: Memory trace resulting from executing audio application on a processor with an ideal memory subsystem.

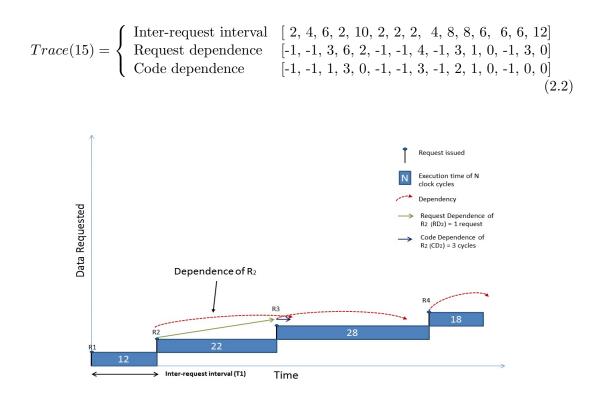

of memory requests issued by the processor to the cache, observed at point A of the Figure 2.1(a). The mathematical representation of the trace is given by Equation (2.2).

Figure 2.5: Memory trace generated by the cache (assistance unit) of the functional module.

Caches are designed such that most of the memory requests issued by the processor to the cache result in a cache hit. However, whenever there is a cache miss, the cache controller, on behalf of the processor, issues external memory requests to the SoC infrastructure. These memory requests constitute the trace observed at point B of Figure 2.1(a). It is clear that the trace generated by the cache controller consists only of external memory requests. This trace is essentially derived from the original trace issued by the processor to the cache, but has fewer requests. The trace generated by the cache controller is as shown in Figure 2.5. In this thesis, we are mainly concerned with the performance dependence of the functional modules on the service provided by the SoC infrastructure. To assess this performance dependence, we inspect and analyze only the external memory request trace of each functional module.

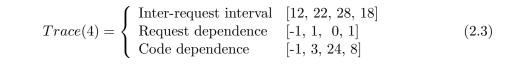

In the given example, requests  $R_1$ ,  $R_4$ ,  $R_{10}$  and  $R_{14}$  of the processor trace result into cache misses and subsequently get manifested as requests  $R_1$ ,  $R_2$ ,  $R_3$  and  $R_4$  respectively, in the trace generated by the cache controller. The cache controller trace is derived from the processor trace and hence, the two traces are inter-related. The issuing instants of the corresponding requests from both traces are assumed to be exactly the same, along with their dependencies. Although the cache trace is derived from the processor trace, the specifications of the two traces in our model are distinct. The processor trace (Figure 2.4) and the cache trace (Figure 2.5) are specified using Equation (2.2) and Equation (2.3) respectively.

Figure 2.6: Memory trace resulting from the execution of real-time video application on a streaming graphics engine with an ideal memory subsystem.

#### 2.2.1.4 A streaming video engine executing a real-time video application

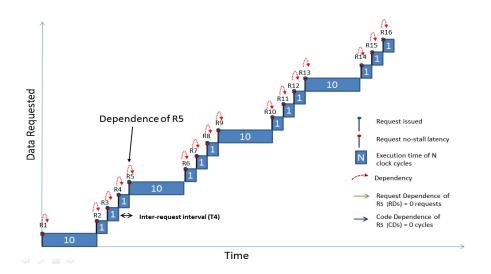

For IPs like video engines or custom hardware accelerators, all memory requests are issued to the pre-fetch unit, which is responsible to have already fetched and stored the necessary data in its data buffer. These requests constitute a trace which is presented in Figure 2.6. It is representative of the trace typically observed at point A of Figure 2.2(b).

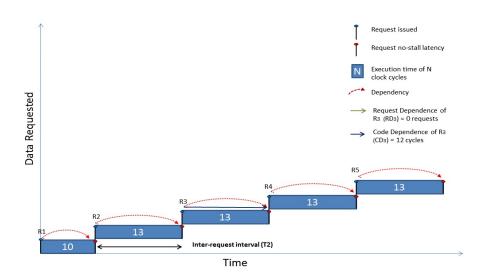

The pre-fetch unit, on the other hand, issues external memory requests to the SoC infrastructure so that it can pre-fetch the necessary data in advance. The pre-fetched data is temporarily held in the data buffers until it is eventually consumed by the core of the functional module. The external memory requests that are issued by the pre-fetch unit constitute the trace shown in Figure 2.7. It represents the trace observed at point B of Figure 2.2(b)

Similar to the previous example, the trace generated by the pre-fetch unit is related to the streaming video engine trace. The request  $R_2$  of the pre-fetch unit trace requests for the data required by requests  $R_6$ ,  $R_7$ ,  $R_8$  and  $R_9$  of the streaming video engine trace. For simplicity, we assume that the instant the data is received by the pre-fetch unit, it is immediately available to the streaming video engine via the data buffers. Again, in this thesis, we are only interested in the external memory trace, which, in this example, is the pre-fetch unit trace.

Figure 2.7: Memory trace generated by the pre-fetcher (assistance unit) of the functional module.

# 2.2.2 Execution behaviour of functional modules

To derive the high-level performance models of functional modules, it is necessary to capturing their execution behaviour. The execution behaviour of functional modules is influenced by two factors:

- 1. Performance of the SoC infrastructure

- 2. Performance of the IPs

# 2.2.3 Performance impact of the SoC infrastructure

The SoC infrastructure is composed of the on-chip network, the memory subsystem and the external DRAM memory. Thus, the performance of the SoC infrastructure is a combination of the performance of the on-chip network, the memory subsystem and the external DRAM memory. It is influenced by a variety of factors such as the quality of service (QoS) facilities it provides, the protocol it uses, arbitration policy for the NoC and memory controller, etc. The performance of the SoC infrastructure can be measured by different parameters such as the bandwidth, service latency etc. However, in this thesis, we are interested in the service latency aspect of the SoC infrastructure and thus relate the performance of the SoC infrastructure to its service latency. The service latency for any memory request issued to the SoC infrastructure involves the latency of the memory subsystem to retrieve the data from the external memory along with the latency of the on-chip network to transport the data from the memory subsystem to the functional module. This service latency is the *actual latency* required to serve the requests from the instant they are issued by the functional module. We formally define actual latency as follows:

#### Actual latency (AL)

- 1. Read Request: Actual latency  $(AL_i)$  of a read request  $R_i$  specifies the number of clock cycles required by the functional module to receive the entire requested data in its buffer, from the instant it issues request  $R_i$ .

- 2. Write Request: The actual latency  $(AL_i)$  of a posted write request  $R_i$  is considered to be zero since we do not wait for the acknowledgement associated with such write requests. However, for non-posted write requests, the actual latency  $(AL_i)$  specifies the number of clock cycles required by the functional module to receive an acknowledgement from the SoC infrastructure after successfully writing the data to the external memory.

In our model, the actual latency of the processor trace (Figure 2.4) is represented by a vector of trace size (N) as indicated by Equation (2.4).

Actual Latency (N) = [12, 10, 14, 14, 12, 10, 12, 12, 14, 14, 14, 12, 10, 8, 14] (2.4)

## 2.2.4 Performance impact of the IPs

The IP executes the application code, thereby generating the external memory request trace. The performance of an IP is significantly affected by the amount of stalling it experiences. In fact, in this work, we determine the performance of a given IP by accounting all the stall cycles it experiences. Thus, to determine the performance impact of the IPs, we need to understand the phenomenon of stalling of the IP.

The stalling of the IP (or functional module) can be defined as a temporary suspension of code execution on the core of the IP. We assume that it is the core of the IP that executes the application code, thereby providing the expected functionality of the functional module. Due to the hardware capabilities of the IPs and the application code structure, all IPs experience some amount of stalling, which is acceptable. However, too much stalling of the IP core can prove detrimental to its performance. Thus, SoC designers must ensure that the stalling experienced by the IP core(s) is within the given bounds.

#### Reasons for the stalling of IP core

Typically, the core of the IP stalls whenever the assistance unit, in co-operation with the SoC infrastructure, is incapable of providing it with the necessary data before a fixed deadline. Thus, the stalling of the processing core is directly dependent on the performance of the assistance unit and the SoC infrastructure. The stalling of the IP cores is attributed to two fundamental restrictions imposed on the IP.

#### Hardware restriction

The hardware restriction is imposed on an IP by its pipeline depth. The pipeline depth of the IP is defined by its ability to issue a certain number of maximum outstanding requests  $(N_{max})$ . The ability of the IP to issue a maximum of  $N_{max}$  requests depends on the hardware support built into it to perform the necessary

bookkeeping of all in-flight requests. If the number of outstanding requests issued at any given time is equal to  $N_{max}$ , a new memory request cannot be issued until the response of a previous request is successfully received. This causes the processing core to stall even though there is no explicit dependence prohibiting the issuance of the next request.

# Software restriction

The software restrictions are imposed on an IP by the request and code dependencies associated with the memory requests as explained in Chapter 1. During the execution of a given application on an IP core, if a request dependence or a code dependence (associated with a request) is encountered, the core of the IP stalls, irrespective of its hardware capability to issue further requests.

Along with the hardware restrictions mentioned above, the assistance unit can also stall due to the finite size of the pre-fetch data buffers. However, the stalling of the assistance unit does not necessarily lead to the stalling of the functional module.

Due to the stalling of the functional module, the service latency of the SoC infrastructure for memory requests, as experienced by the core of the functional module varies. To mathematically express the phenomenon of stalling, we introduce the following concepts:

- 1. Total execution time (E)

- 2. No-stall interval (NI)

- 3. Perceived latency (PL)

- 4. Derived benefit (DB)

# **2.2.5** Total execution time (E):

The total execution time (E) is defined as the number of clock cycles required by a given IP to execute the entire application code. The total execution time is a direct measure of the performance of an IP to execute a given application code. It is dependent on a variety of factors such as:

- 1. Application characteristics (e.g. length of application code, the number of memory movement instructions, etc.)

- 2. IP characteristics (e.g. latency tolerance of the processor/ IP, cache size, cache hit-rate, etc.)

- 3. SoC infrastructure characteristics (e.g. service latency of the SoC infrastructure, etc.)

The total execution time (E) of the base trace executed on a trace simulator coupled to an ideal (zero service latency) SoC infrastructure is defined as *base time*  $(E_0)$ . It is mathematically defined by Equation (2.5).

$$E_0 = \sum_{i=1}^{N} T_i$$

(2.5)

For a SoC infrastructure with a non-zero service latency, the total execution time is generally greater than the base time.

# 2.2.6 No-stall interval

The no-stall interval  $(NI_i)$  of a request  $R_i$  is the time interval during which the core can continue with the application execution without stalling for the data requested by request  $R_i$ . It can also be seen as an allowance period given to the SoC infrastructure to produce the requested data, after the functional module issues the corresponding memory request. Every request  $R_i$  has a fixed no-stall interval  $(NI_i)$  which can be derived by analyzing the application code or the external memory request trace. Equation (2.6) can be used to determine the no-stall interval  $(NI_i)$  of a given request  $R_i$ .

$$NI_{i} = \left(\sum_{j=i}^{(i+RD_{i})} T_{j}\right) + CD_{i}$$

(2.6)

# 2.2.7 Perceived latency

The perceived latency  $(PL_i)$  of a request  $R_i$  is the number of clock cycles for which the core of the functional module actually stalls while waiting for the response of request  $R_i$ . Here, we assume that the sole reason for the IP to stall is the inability of the SoC infrastructure to successfully produce the requested data within the no-stall interval of request  $R_i$ .

For a given application code, the total execution time of the functional module is at least equal to the base time  $(E_0)$ . This generally happens when the functional module is coupled to an ideal (zero service latency) SoC infrastructure. For a SoC infrastructure with a non-zero service latency, the total execution time is greater than the base time if the non-zero service latency of the SoC infrastructure leads to the stalling of the functional module. In fact, the total execution time of a functional module can be determined by adding the base time  $(E_0)$  to the sum of perceived latencies of all external memory requests issued by the functional module. The total execution time (E) of a trace (size N, base time  $(E_0)$ ), executing on an IP coupled to a SoC infrastructure with a non-zero service latency is given by using Equation (2.7).

$$E = E_0 + \sum_{i=1}^{N} PL_i$$

(2.7)

# 2.2.8 Derived Benefit

The perceived latency for a given memory request  $R_i$  does not account for the stalls caused by any of the previous or next  $(N_{max} - 1)$  requests. The stalling of the IP due to a given request provides additional no-stall interval to all the current outstanding requests. This additional no-stall interval available to all outstanding requests is termed as *derived benefit*. The derived benefit is propagated to the neighbouring outstanding requests, both in the forward and the backward direction. In our model, we use the term derived benefit of request  $R_i$ , represented by  $DB_i$ , to denote the cumulative sum of derived benefits provided by all neighbouring requests of the given request  $R_i$ . In essence, the derived benefit of a given request is the sum of the perceived latencies of all neighbouring requests which overlap with the given request. The parameter of derived benefit is computed dynamically (at run-time) based on the knowledge of which requests overlap with the given request. The method of computing the derived benefit is presented as an algorithm explained in Appendix A.

Mathematically, perceived latency can be expressed in terms of the actual latency, the no-stall latency and the derived benefit using Equation (2.8).

$$PL_i = max(0, AL_i - NI_i - DB_i)$$

$$(2.8)$$

The no-stall interval, perceived latency, actual latency and the derived benefit together allow us to capture the execution of the external memory request trace. At the same time, these parameters capture the performance dependence of the functional modules on the service provided by the SoC infrastructure. Thus, by analyzing the external memory request trace with respect to these parameters, the execution behaviour of the functional modules can be captured in their performance models.

# 2.3 Performance modeling of functional modules

The functional module can be abstracted to a high-level model by capturing its execution behaviour and its performance dependence on the SoC infrastructure, especially its latency tolerance towards the service latency of the SoC infrastructure. The parameter of no-stall interval mainly quantifies and expresses the latency tolerance of functional modules. The model thus uses the parameter of no-stall interval for characterizing the functional module.

The advantage of using the no-stall interval to characterize the functional module is that the no-stall interval is solely dependent on the functional module (i.e the application code and the hardware capabilities of the IP). It is completely independent of the supporting SoC infrastructure and is also independent of other functional modules sharing the SoC infrastructure. Thus, the functional modules can be independently characterized at design time by using the parameter of no-stall interval.

# 2.4 Performance modeling of the SoC infrastructure

The performance model for the SoC infrastructure mainly captures the performance of the SoC infrastructure in terms of its service latency. The service latency of the SoC infrastructure for a given memory request is a combination of the latency of the memory subsystem to retrieve the data from the external memory along with the latency of the on-chip network to transport the data from the memory subsystem to the functional module. This service latency is the *actual latency* required to serve the requests from

Figure 2.8: System level representation of the SoC

the instant they are issued to the SoC infrastructure by the functional modules. Thus, we model the performance of the SoC infrastructure by the parameter of actual latency, which is a direct measure of its service latency.

The actual latency of a SoC infrastructure is directly dependent on the characteristics of the on-chip network (topology, configuration, arbitration, QoS capabilities, etc.), the memory subsystem (configuration, arbitration, QoS capabilities) and the external DRAM memory (gross available bandwidth, etc.). It is also dependent on the request issuing behaviour and the performance of functional modules. The actual latency value is therefore determined either by measuring the actual latency for each external memory request issued by the functional module or by simply considering the average/ worstcase service latency of the SoC infrastructure. At times, the SoC designer can utilize statistical data and approximate the actual latency of individual requests by providing an average actual latency value along with the deviation (or spread) of the values over the length of a given trace.

# 2.5 The complete SoC model

The system on chip can be viewed as a collection of functional modules connected to each other and the SoC resources (like external memory, display system etc.) via the SoC infrastructure (Figure 2.8). Thus, the entire SoC can be modeled by connecting together the performance models of individual functional modules to the performance model of the SoC infrastructure. The performance model of the complete SoC is thus, built using the performance models of the functional modules and the SoC infrastructure as shown in Figure 2.9.

The interaction of the functional modules and the SoC infrastructure is captured using the perceived latency. The perceived latency indicates the number of stall cycles experienced by the functional module while receiving service from the SoC infrastructure. It can also be viewed as a figure of merit for the performance of the functional module in association with a given SoC infrastructure.

# 2.6 Basics of Performance Estimation

The high-level performance models discussed earlier are used for the performance estimation of the functional modules and the SoC infrastructure. Rapid performance estimation ultimately enables the SoC designer to efficiently integrate and verify the performance of IPs. Performance estimation can be achieved by using either a cycle-accurate trace simulator or a set of simplified equations based on average performance metrics. Both the approaches use the same performance models and hence, are conceptually identical. However, they differ in their complexity, accuracy, verification time and implementation effort.

Performance estimation requires the designer to execute a given task on a functional module coupled to a given SoC infrastructure and by some means, estimate its performance. As discussed previously, the execution of application code on an IP can be abstracted with the execution of its external memory request trace. The execution of the external memory request trace can be performed using either a trace simulator or can be approximated using a set of average performance values. Performance estimation is therefore performed in two steps:

- 1. Characterization of functional modules and the SoC infrastructure.

- 2. Execution of the external memory request trace.

# 2.6.1 Characterization of functional modules and the SoC infrastructure

#### Characterization of functional modules

The characterization of a functional module is performed differently depending on which performance estimation technique is used. In the trace-based performance estimation technique, the functional module is characterized by going through the (worst-case) application trace on a per-request basis and evaluating the no-stall interval of each request. To evaluate the no-stall interval of each request, it is also necessary to specify the hardware capabilities of the IP, mainly its ability to issue multiple outstanding requests  $N_{max}$ . The trace-based technique thus uses the application trace to characterize the functional module.

On the other hand, the simplified equation-based performance estimation technique utilizes average performance values for characterizing the functional module. These average performance values can be determined by analyzing the trace and extracting the average no-stall interval per request  $NI_{avg}$  and the spread of the no-stall interval  $NI_{spread}$  about the average value. They can also be determined by simply considering the worst-case values or making a calculated guess based on past experiences. The functional module can then be abstracted to a black box characterized by the parameters of average no-stall interval ( $NI_{avg}$ ) and its spread ( $NI_{spread}$ ).

The parameter of no-stall interval characterizes the latency tolerance of the functional module. A high value of average no-stall interval suggests that the functional module can tolerate a large service latency per request until it finally stalls for the requested data. At the same time, the spread in no-stall interval suggests how far the no-stall intervals of individual requests deviate from the average value. A large value of spread in no-stall interval indicates that the no-stall interval of individual requests varies significantly about the average value, possibly due to the bursty request issuing nature of the functional module. Likewise, a small value of spread in no-stall interval is indicative of a more regular request issuing behaviour of the functional module.

# Characterization of the SoC infrastructure

The SoC infrastructure is characterized by the parameter of actual latency. For characterizing the SoC infrastructure, we assume that each request issued to the SoC infrastructure is served with a given average actual latency  $(AL_{avg})$ . Along with the average actual latency, we also utilize the spread in actual latency  $(AL_{spread})$ . The average actual latency value is determined either by using statistical data or by simply considering the worst-case service latency, whereas the spread is mainly determined by using statistical data.

The average actual latency  $(AL_{avg})$  indicates the average service latency of the SoC infrastructure to serve any given external memory request. The spread of actual latency  $(AL_{spread})$  indicates the deviation in the service latency provided to individual memory requests as compared to the average actual latency value. A high value of spread indicates that the SoC infrastructure is not consistent in providing service to individual memory requests. It could also indicate that the functional modules coupled to the given SoC infrastructure issue requests for localized data in a bursty manner, due to which some

requests are served with a large service latency, whereas others are served with a relatively small service latency.

The functional module and the SoC infrastructure are characterized and abstracted to their respective performance models independently. For a given functional module, the characterization step is performed only once. The performance model of the functional module can then be used over multiple SoC designs. This is particularly useful from the design re-use point of view. The performance model of the SoC infrastructure captures the performance dependence of the SoC infrastructure (on parameters like burstiness, bandwidth, request behaviour, priority, etc.) into a single parameter of actual latency, thereby simplifying the performance estimation process. The characterization of functional modules and the SoC infrastructure is essential in both the performance estimation techniques.

# 2.6.2 Execution of the external memory request trace