# Design and Formal Analysis of Real-Time Memory Controllers

PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus prof.dr.ir. F.P.T. Baaijens, voor een commissie aangewezen door het College voor Promoties, in het openbaar te verdedigen op maandag 26 september 2016 om 16:00 uur

door

Yonghui Li

geboren te Shaanxi, China

Dit proefschrift is goedgekeurd door de promotoren en de samenstelling van de promotiecommissie is als volgt:

| voorzitter:              | prof.dr.ir. A.B. Smolders                    |  |  |  |

|--------------------------|----------------------------------------------|--|--|--|

| 1 <sup>e</sup> promotor: | prof.dr. K.G.W. Goossens                     |  |  |  |

| copromotor:              | dr. K.B. Akesson (CISTER INESC TEC and ISEP) |  |  |  |

| leden:                   | prof.dr. Y. Wang (Uppsala University)        |  |  |  |

|                          | prof.dr.ir. J.P. Katoen (RWTH Aachen)        |  |  |  |

|                          | prof.dr.ir. C.H. van Berkel                  |  |  |  |

|                          | dr.ir. R.J. Bril                             |  |  |  |

Het onderzoek dat in dit proefschrift wordt beschreven is uitgevoerd in overeenstemming met de TU/e Gedragscode Wetenschapsbeoefening.

# Design and Formal Analysis of Real-Time Memory Controllers

Yonghui Li

Committee:

| prof.dr. K.G.W. Goossens    | Eindhoven University of Technology, promotor |

|-----------------------------|----------------------------------------------|

| dr. K.B. Akesson            | CISTER INESC TEC and ISEP, copromotor        |

| prof.dr.ir. A.B. Smolders   | Eindhoven University of Technology, chairman |

| prof.dr. Y. Wang            | Uppsala University                           |

| prof.dr.ir. J.P. Katoen     | RWTH Aachen University                       |

| prof.dr.ir. C.H. van Berkel | Eindhoven University of Technology           |

| dr.ir. R.J. Bril            | Eindhoven University of Technology           |

© Yonghui Li 2016. All rights are reserved. Reproduction in whole or in part is prohibited without the written consent of the copyright owner.

This thesis was typeset in LATEX, written in *Sublime Text* and built with *SCons*. The figures were created with Viso and the graphs were plotted using python *matplotlib*.

The cover of this thesis was designed by Mr. Juan Manuel Martelli.

Printed by CPI Koninklijke Wöhrmann – The Netherlands.

A catalogue record is available from the Eindhoven University of Technology Library. ISBN: 978-90-386-4140-9

#### ACKNOWLEDGMENTS

The PhD study has resulted in this thesis after four-year hard work, which involved many bright minds and productive collaborations with many people. I foremost thank my promotor Prof. Kees Goossens for his continuous encouragement, and for his sharp insights and valuable suggestions that helped to make progresses in my research and also engineering skills. For his broaden knowledge and wisdom, I would like to say that he is the one whom I can always believe. My special thank goes to my co-promotor Dr. Benny Akesson for his comprehensive assistance in the whole procedure of my research work. I extremely appreciate all the enjoyable and detailed discussions with him, which helped me to make my work more concrete. In addition to the technical work, I am also very grateful to him for taking care of me in life and for always giving me valuable advices. I would also like to thank Prof. Yi Wang, Prof. Kees van Berkel, Prof. Joost-Pieter Katoen, Dr. Reinder J. Bril, and Prof. Bart Smolders for being my thesis committee and giving their valuable feedback.

Without productive and supportive collaborations, it is hard to come up with this thesis. In particular, I want to thank Dr. Orlando Moreira, Hrishikesh Salunkhe, and João Bastos for their help on the dataflow modeling of the memory controller. Without their persistent support, it was hard to complete this work fast and was impossible to win the best paper award from ESTIMEdia' 15. I also thank Dr. Marc Geilen for the valuable discussions of dataflow modeling. His deep insight helped me to correct my model and make the work more concrete. My special thank also goes to Dr. Kai Lampka for the generous discussions about timed automata model and for making my stay in Uppsala enjoyable. I also appreciate his help in completing a paper published in a top conference. Mladen Skelin has given very valuable feedback on a chapter of this thesis. Moreover, the discussions with him were very enjoyable and useful. He deserves my gratitude. I would also like to thank Valeriu Codreanu especially for his help in applying for the permission to use the SURFsara servers. Acknowledgment also goes to SURFsara for supporting the experiments of model checking.

In the past four years, I have had the opportunity to work with a large number of people. I am especially grateful to the Memory team, where I comprehensively learned the memory subsystem. I enjoyed the discussions during the regular meetings. I also appreciate the critical feedback from the team members on my work as well as their great help on solving (non-)technical issues. I was fortunate to be a part of the memory team, and I am thankful to the team members Sven Goossens, Manil Dev Gomony, Karthik Chandrasekar, and Jasper Kuijsten. The memory team was involved in a larger CompSoC team, where I learned more about multicore embedded systems than anywhere else. I am grateful to the CompSocers Andrew Nelson, Martijn Koedam, Gabriela

Breaban, Reinier van Kampenhout, Shubhendu Sinha, Davit Mirzoyan, Juan Valencia, Rasool Tavakoli, and Hadi Ahmadi Balef for the valuable and interesting discussions.

I am very grateful to the friendship of all members of the Electronic Systems group. Many thanks to Firew Siyoum, Shakith Fernando, Erkan Diken, S. Rehan Afzal, Francesco Comaschi, Luc Vosters, Mark Wijtvliet, Gert-Jan van den Braak, Maurice Peemen, Amir Behrouzian, Hadi Ara, Joost van Pinxten, Andreia Moço, Robinson Medina Sanchez, Sander Stuijk, for the wonderful discussions during internal/external meetings/conferences, parties, and group events. My sincere thanks give to our group secretaries Marja de Mol, Rian van Gaalen, and Margot Gordon for their special care and supportive assistances that made my stay in the office very comfortable. I am extremely thankful to these Chinese in our group, including Dongrui She, Yifan He, Hailong Jiao, Xin Chen, Jun Zhu, Bo Liu, Ang Li, Wenjin Wang, Wenfeng (Sean) Wang, Tong Geng, Qi Tang, Zechuan Li, Hubiao Yang, for their help in work and life and also the great moments that we shared together inside and outside work.

The PhD life might be not colorful without many friends for the daily life. I would like to thank my running partners Jiong Zhang, Hefeng Zhou, Zizheng Cao, Qing Wang, Jie Xie, for sharing many great moments outside. I am also grateful to Bilin Han, Caixia Liu and Roy Berkeveld, Shenhai Ran, Wang Miao and Shuli Wang, Yuqing Jiao, Pei Tang, Jun Xia, Guanna Li and Dapeng Sun, Jiquan Wang, Lin Xu and Yang Zhang, Huapeng Sui, Shengnan Lu, Yaping Luo and many others who made my stay in Eindhoven filled with lots of joy and fun.

Finally, I would like to thank my family for supporting me through all these years. Their encouragement and expectation drive me to move on. No matter how far away we are from each other, our hearts are always close. In particular, I would like to thank my farther who left us three years ago. May you find peace in heaven and you are always in my heart. Last but not least, I am very grateful to my wife YingChao Cui for supporting me to overcome the difficulties in life and work, and for sharing the exciting moments together. I cannot imagine how miserable my life might be without her accompanying in the past years. I really look forward to the future life being with her.

Yonghui Li, August 17, 2016

# Design and Formal Analysis of Real-Time Memory Controllers

Modern multi-core embedded systems integrate an increasing number of heterogeneous resources to provide the necessary computational capacity for executing a variety of applications simultaneously. To reduce the cost, resources are shared by real-time and non-real-time applications. The former have timing requirements, such as a maximum response time or a minimum throughput, which must always be satisfied. The latter must be responsive and require good average performance. However, it is difficult to design these systems because of the complex sharing of resources between applications, making it challenging to meet their timing requirements.

SDRAM is typically used as a main data storage device in embedded systems to store the data for the executed applications. It is shared by memory requestors, such as processors, DMAs, and hardware accelerators, which generate diverse memory traffic in terms of arbitrary read/write transactions with variable sizes on behalf of the applications they run. As a result, the memory controller coordinating between the requestors and the SDRAM has to provide guaranteed performance for real-time applications, while still giving good average performance to the rest, in the context of this diverse memory traffic. It is difficult for a memory controller to meet this requirement, because SDRAM is a complex resource, resulting in interference between requestors when they compete for the memory. Existing real-time memory controllers execute transactions by scheduling commands to the SDRAM either (semi-)statically based on pre-computed command schedules or dynamically. Static scheduling eases the analysis by sacrificing average performance, since run-time information cannot be exploited, and it does not efficiently support variable transaction sizes. On the other hand, dynamic scheduling achieves better average performance, while the analysis becomes harder. Therefore, existing dynamically-scheduled memory controllers and/or their analyses only support fixed transaction sizes.

The goal of this thesis is to overcome the problem of designing an efficient real-time memory controller for increasingly complex systems that feature a mix of real-time and non-real-time applications. The main contributions of this thesis are 1) a memory controller, named Run-DMC, designed to efficiently deal with the diverse traffic by dynamically scheduling commands for each transaction at run-time, and 2) three analysis approaches proposed to provide the worst-case response time (WCRT) and worst-case bandwidth (WCBW) based on a formalization, a dataflow model, and a timed automata model, respectively.

The architecture of Run-DMC consists of a front-end and a back-end. The front-end connects to the requestors through a bus or Network-on-Chip (NoC). It receives transactions from different requestors and then uses a novel work-conserving *time-division multiplexing* (*TDM*) arbiter to send transactions to the back-end. The TDM arbiter uses time slots with variable lengths to cope with the variable-sized transactions. Moreover, the requirements of the requestors can be satisfied by allocating a different number of slots to them. The back-end executes transactions with variable sizes by dynamically scheduling commands to the SDRAM using a new command scheduling algorithm, which exploits pipelining within and between transactions.

Run-DMC is analyzed using three proposed analysis approaches. Our first approach is based on a formalization that accurately computes the time when a command is scheduled. The formalization is implemented as an open-source tool called *RTMemController*. Based on the formalization, the WCRT and WCBW can be computed, and they are guaranteed to be conservative using manual proofs, which are time-consuming to make. Our second approach switches the effort from formal analysis to modeling the timing behavior of the memory controller, which is much easier and faster. The worst-case bounds can be derived by analyzing the model with existing techniques and tools, which can automatically handle the complex interferences between transactions. The second approach is based on a mode-controlled dataflow (MCDF) model. An existing tool called Heracles is used to automatically derive the WCBW bound. However, Heracles cannot analyze the WCRT. The third approach uses a timed automata (TA) model to accurately capture the timing behavior of Run-DMC, and the bounds on WCBW and WCRT are obtained by verifying properties of the TA model via model checking. Finally, since the same memory controller is analyzed with these three analysis approaches, we investigate their strengths and weaknesses with respect to performance, portability, exploitation of static information, simulation, validation, and verification.

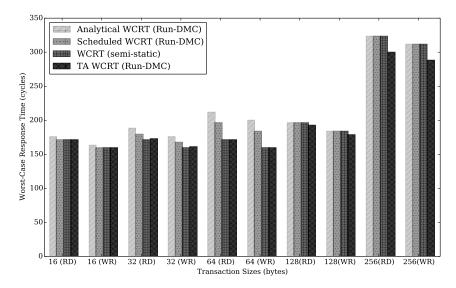

The proposed memory controller and the analysis approaches are experimentally evaluated. The results demonstrate that Run-DMC significantly outperforms a stateof-the-art semi-static memory controller in the average case by achieving 44.9% smaller response time and 16.7% larger bandwidth, while they are comparable in the worst-case. Moreover, we compare the performance of the three analysis approaches and quantify the impact of their underlying assumptions. The results show that the TA model outperforms the MCDF model that in turn is better than the formal analysis approach.

# CONTENTS

| 1 | INTRODUCTION 1.1 Real-Time Embedded Systems                        | 1<br>2 |

|---|--------------------------------------------------------------------|--------|

|   | 1.1     Real Time Embedded Systems       1.2     Problem Statement | 5      |

|   | 1.2       Troblem Statement         1.3       Thesis Contributions | 7      |

|   |                                                                    | '      |

| 2 | BACKGROUND $\dot{\sigma}$ terminology                              | 13     |

|   | 2.1 SDRAM Architecture and Operation                               | 13     |

|   | 2.2 Real-Time Memory Controllers                                   | 18     |

|   | 2.3 Analysis of Real-Time Memory Controllers                       | 21     |

| 3 | RUN-DMC: A REAL-TIME MEMORY CONTROLLER WITH DYNAMIC COM-           |        |

|   | MAND SCHEDULING                                                    | 31     |

|   | 3.1 Related Work                                                   | 32     |

|   | 3.2 Memory Controller Front-End                                    | 33     |

|   | 3.3 Memory Controller Back-End                                     | 38     |

|   | 3.4 Cycle-Accurate SystemC Model of Run-DMC                        | 43     |

|   | 3.5 Experimental Results                                           | 45     |

|   | 3.6 Summary                                                        | 55     |

| 4 | FORMAL ANALYSIS OF RUN-DMC                                         | 57     |

|   | 4.1 Related Work                                                   | 58     |

|   | 4.2 Formalization of Dynamic Command Scheduling                    | 60     |

|   | 4.3 Worst-Case Initial Bank States                                 | 63     |

|   | 4.4 Worst-Case Execution Time                                      | 66     |

|   | 4.5 Worst-Case Response Time                                       | 73     |

|   | 4.6 Worst-Case Bandwidth                                           | 75     |

|   | 4.7 <i>RTMemController</i> Tool                                    | 75     |

|   | 4.8 Experimental Results                                           | 77     |

|   | 4.9 Summary                                                        | 88     |

| 5 | MODE-CONTROLLED DATAFLOW (MCDF) MODELING OF RUN-DMC                | 91     |

|   | 5.1 Related Work                                                   | 92     |

|   | 5.2 Background of Dataflow Models                                  | 94     |

|   | 5.3 MCDF Model of Run-DMC                                          | 99     |

|   | 5.4 Worst-Case Bandwidth                                           | 107    |

|   | 5.5 Experimental Results                                           | 109    |

|   | 5.6 Summary                                                        | 114    |

| 6 | TIMED AUTOMATA (TA) MODELING OF RUN-DMC                            | 117    |

|   | 6.1 Background of Timed Automata                                   | 118    |

| x | CONTENTS  |

|---|-----------|

|   | 001111110 |

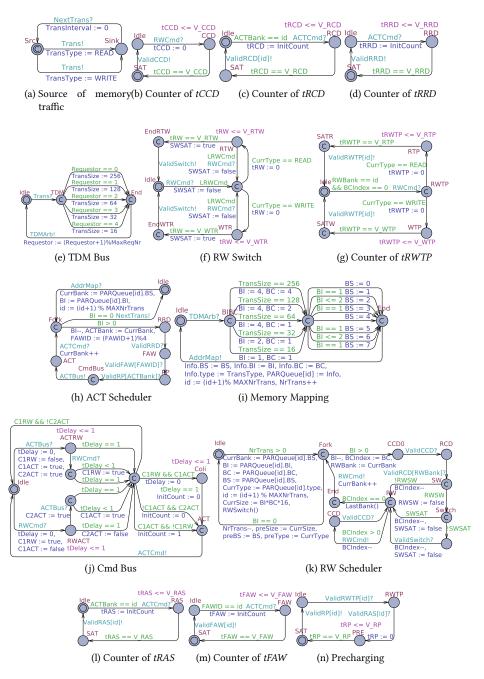

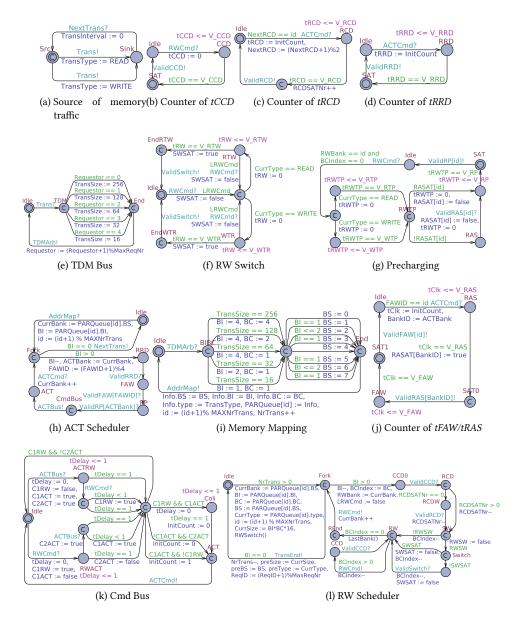

|    | 6.2 Modular TA Model of Run-DMC                           | 120   |

|----|-----------------------------------------------------------|-------|

|    | 6.3 Verification with Model Checking                      | 130   |

|    | 6.4 Related Work                                          | 134   |

|    | 6.5 Experimental Results                                  | 135   |

|    | 6.6 Summary                                               | 143   |

| 7  | CONCLUSIONS AND FUTURE WORK                               | 145   |

|    | 7.1 Conclusions                                           | 145   |

|    | 7.2 Future Work                                           | 151   |

| BI | BLIOGRAPHY                                                | 153   |

| A  | PROOF OF LEMMAS                                           | 163   |

|    | A.1 Proof of Lemma 1                                      | 163   |

|    | A.2 Proof of Lemma 2                                      | 164   |

|    | A.3 Proof of Lemma 3                                      | 166   |

|    | A.4 Proof of Lemma 4                                      | 168   |

|    | A.5 Proof of Theorem 1                                    | 170   |

|    | A.6 Proof of Theorem 2                                    | 172   |

|    | A.7 Proof of Lemma 5                                      | 173   |

| в  | SYSTEM DECLARATIONS FOR TIMED AUTOMATA MODEL              | 175   |

|    | B.1 Intuitive Timed Automata Model                        |       |

|    | B.2 Simplified Timed Automata Model                       | 176   |

| С  | SCALABILITY OF MODE-CONTROLLED DATAFLOW AND TIMED AUTOMAT | A 179 |

| D  | LIST OF ACRONYMS                                          | 183   |

| Е  | LIST OF SYMBOLS                                           | 185   |

| F  | ABOUT THE AUTHOR                                          | 187   |

| LI | ST OF PUBLICATIONS                                        | 190   |

# LIST OF FIGURES

| Figure 1.1  | An example of a multi-core hardware platform                    | 3  |

|-------------|-----------------------------------------------------------------|----|

| Figure 1.2  | An abstracted view on a typical memory controller               | 4  |

| Figure 1.3  | The development of our dynamically-scheduled memory con-        |    |

|             | troller Run-DMC.                                                | 9  |

| Figure 2.1  | SDRAM architecture                                              | 14 |

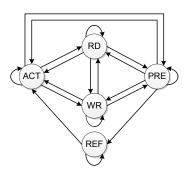

| Figure 2.2  | Simplified state diagram of scheduling commands                 | 16 |

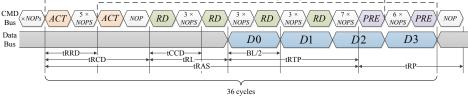

| Figure 2.4  | The general architecture of a memory controller.                | 19 |

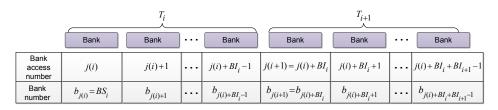

| Figure 2.6  | Bank access number and bank number for $T_i$ and $T_{i+1}$ .    | 21 |

| Figure 2.7  | An example of illustrating the bank accesses for transactions   |    |

|             | $T_0, T_1, \text{ and } T_2$ .                                  | 22 |

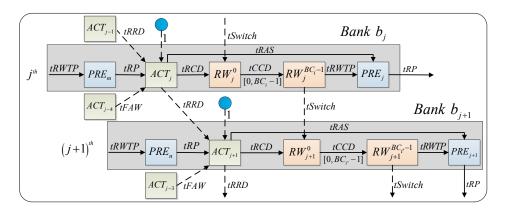

| Figure 2.8  | Command scheduling dependencies between any two succes-         |    |

|             | sive bank accesses corresponding to $T_i$ and $T_{i'}$ .        | 23 |

| Figure 2.9  | Dependencies between transactions.                              | 24 |

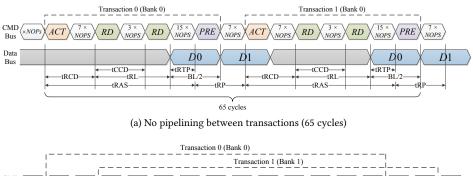

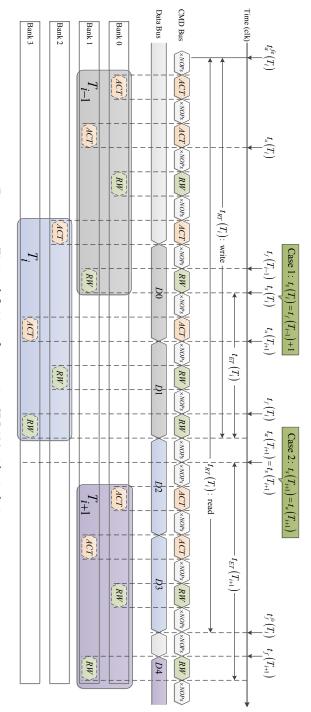

| Figure 2.11 | Timing definitions for accessing SDRAM with pipelining.         | 28 |

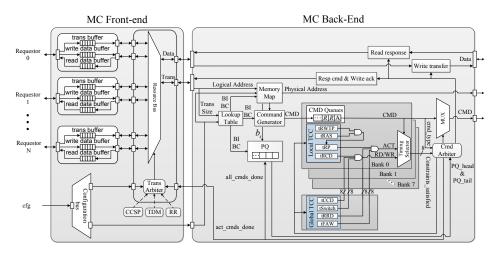

| Figure 3.1  | The architecture of the front-end and back-end of Run-DMC.      | 34 |

| Figure 3.2  | The worst-case interference delay for requestor $r_1$ : (a) TDM |    |

| -           | slot allocation; (b) the proposed work-conserving TDM arbiter;  |    |

|             | (c) traditional work-conserving TDM arbiter.                    | 38 |

| Figure 3.3  | The structure of the cycle-accurate SystemC simulator of Run-   |    |

|             | DMC                                                             | 43 |

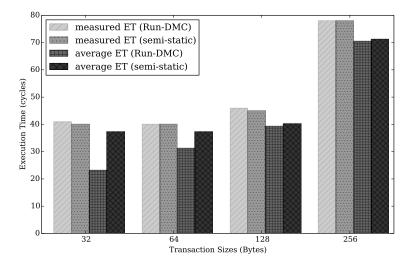

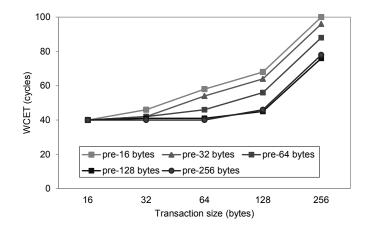

| Figure 3.4  | The maximum measured WCET and average execution time (ET)       |    |

|             | for DDR3-1600G SDRAM with fixed transaction sizes               | 47 |

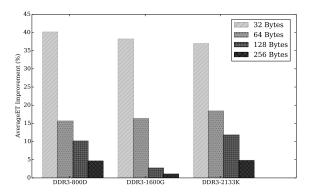

| Figure 3.5  | The improvement of the average execution time (ET) for dif-     |    |

|             | ferent DDR3 SDRAMs with fixed transaction sizes. The results    |    |

|             | of Run-DMC are compared to the semi-static approach [3]         | 48 |

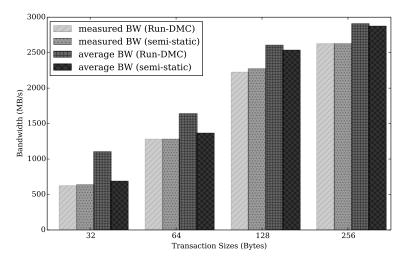

| Figure 3.6  | The measured minimum and average bandwidth for DDR3-            |    |

|             | 1600G SDRAM with fixed transaction sizes.                       | 49 |

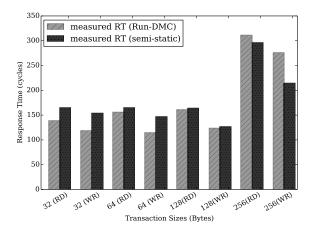

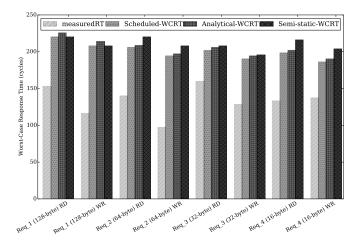

| Figure 3.7  | The maximum measured response time (RT) for DDR3-1600G          |    |

|             | SDRAM with fixed transaction sizes.                             | 50 |

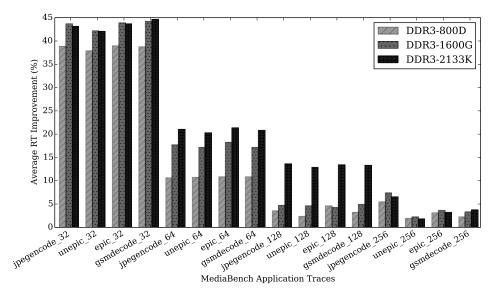

| Figure 3.8  | Comparison to a semi-static approach [3] in average response    |    |

|             | time of Mediabench application traces for different DDR3 SDRAM  | s  |

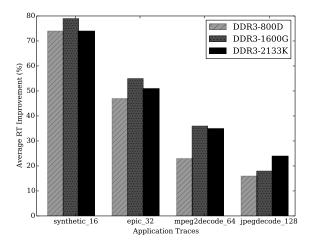

|             | with fixed transaction size.                                    | 51 |

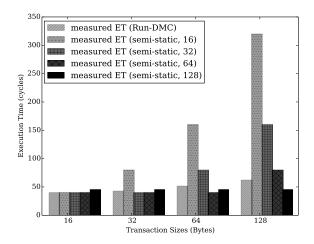

| Figure 3.9  | The maximum measured WCET of both Run-DMC and the               |    |

| -           | semi-static approach [4] for DDR3-1600G SDRAM with vari-        |    |

|             | able transaction sizes.                                         | 53 |

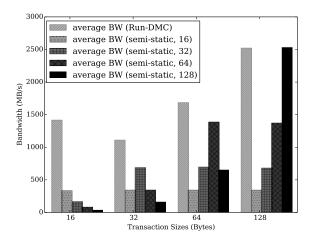

|             |                                                                 |    |

| Figure 3.10 | The average bandwidth (BW) of both Run-DMC and the semi-<br>static approach [4] for DDR3-1600G SDRAM with variable trans-                                                                                      |    |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

|             | action sizes.                                                                                                                                                                                                  | 54 |  |

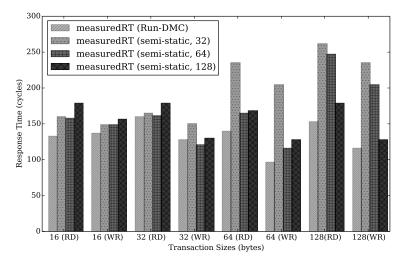

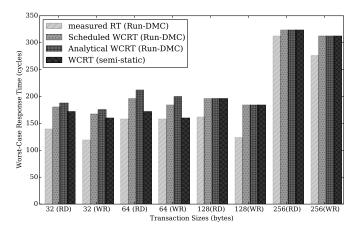

| Figure 3.11 | The measured response time (RT) of both Run-DMC and the semi-static approach [4] for DDR3-1600G SDRAM with vari-                                                                                               |    |  |

| -           | able transaction sizes.                                                                                                                                                                                        | 55 |  |

| Figure 3.12 | The average response time (RT) improvement gained by Run-<br>DMC versus the semi-static approach [4] with the best patterns<br>for DDR3 SDRAMs with variable transaction sizes.                                | 56 |  |

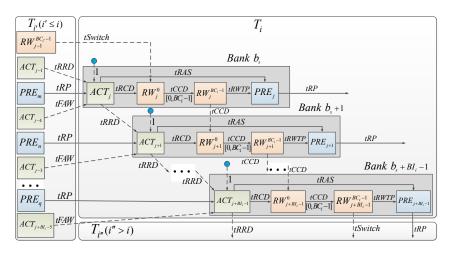

| Figure 4.1  | The timing dependencies of command scheduling for transaction $T_i$ .                                                                                                                                          | 62 |  |

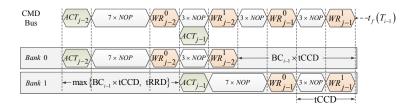

| Figure 4.2  | An example of As-Late-As-Possible ( <i>ALAP</i> ) scheduling with DDR3-1600G SDRAM for $T_i$ which has $BI_i = 4$ and $BC_i = 2$ . The previous transaction $T_{i-1}$ uses $BI_{i-1} = 2$ and $BC_{i-1} = 2$ . |    |  |

|             | The previous transaction $T_{i-1}$ uses $B_{i-1} = 2$ and $B_{C_{i-1}} = 2$ .<br>The starting bank for both $T_{i-1}$ and $T_i$ is <i>Bank</i> 0.                                                              | 65 |  |

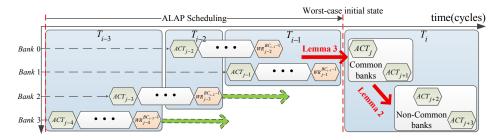

| Figure 4.3  | An illustration of the <i>ALAP</i> scheduling that provides worst-                                                                                                                                             | 05 |  |

| rigure 4.5  | case initial bank states for the current transaction $T_i$                                                                                                                                                     | 67 |  |

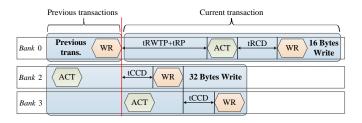

| Figure 4.4  | An example illustrating that the actual execution time of a                                                                                                                                                    | 07 |  |

| 8           | larger transaction (32 Bytes write) can be less than that of a                                                                                                                                                 |    |  |

|             | smaller transaction (16 Bytes write).                                                                                                                                                                          | 72 |  |

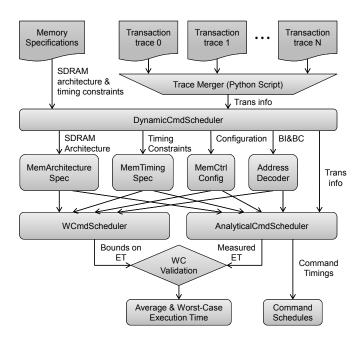

| Figure 4.5  | The design flow of <i>RTMemController</i> , an open-source WCET                                                                                                                                                |    |  |

| 8           | and ACET analysis tool for real-time memory controllers [70].                                                                                                                                                  | 76 |  |

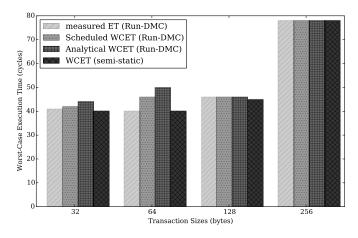

| Figure 4.6  | The WCET of fixed transaction sizes with DDR3-1600G SDRAM.                                                                                                                                                     |    |  |

| C           | Results are compared to a semi-static approach [3]                                                                                                                                                             | 80 |  |

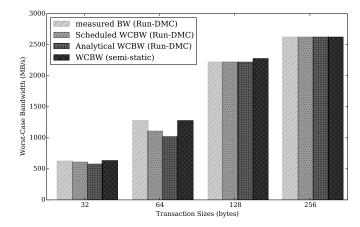

| Figure 4.7  | The worst-case bandwidth (WCBW) for a DDR3-1600G SDRAM using our dynamically-scheduled Run-DMC and the semi-static                                                                                             |    |  |

|             | approach [3] with fixed transaction sizes.                                                                                                                                                                     | 81 |  |

| Figure 4.8  | The worst-case response time for DDR3-1600G SDRAM with                                                                                                                                                         |    |  |

|             | fixed transaction sizes                                                                                                                                                                                        | 82 |  |

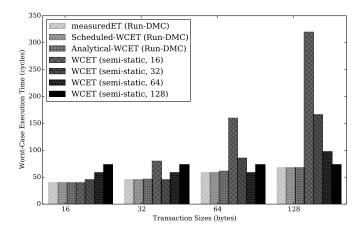

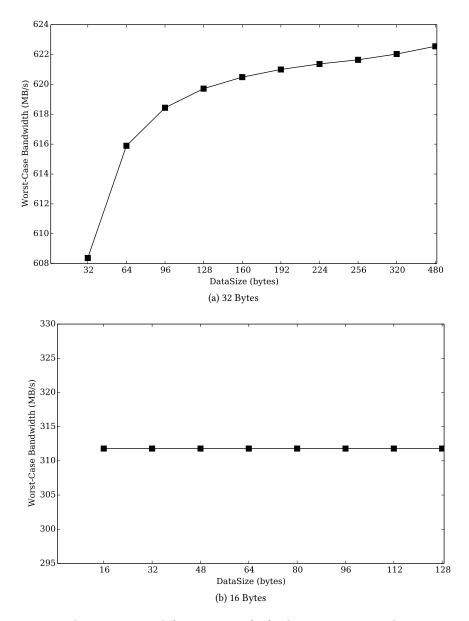

| Figure 4.9  | WCET for DDR3-1600G with variable transaction sizes                                                                                                                                                            | 83 |  |

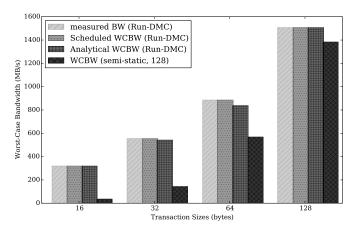

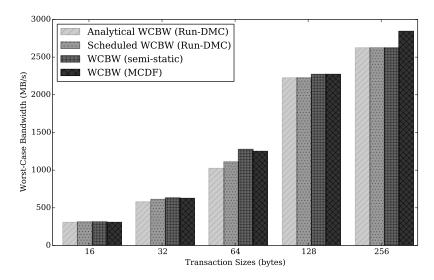

| Figure 4.10 | Worst-Case Bandwidth for DDR3-1600G with variable trans-<br>action sizes.                                                                                                                                      | 84 |  |

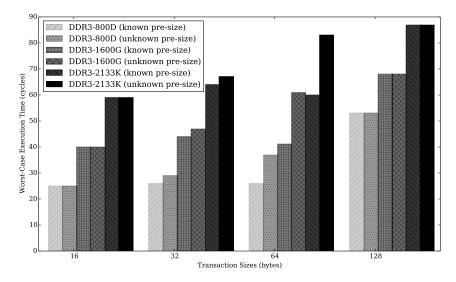

| Figure 4.11 | WCET with known/unknown previous transaction size. Re-<br>questors are allocated to TDM slots in descending order of their                                                                                     |    |  |

|             | transaction sizes.                                                                                                                                                                                             | 85 |  |

| Figure 4.13 | WCRT for DDR3-1600G with variable transaction sizes.                                                                                                                                                           | 88 |  |

| Figure 4.14 | The monotonicity of scheduled WCET with transaction size                                                                                                                                                       | 00 |  |

| 1.5010 1.11 | for a requestor. DDR3-1600G is taken as an example.                                                                                                                                                            | 89 |  |

| Figure 5.1  | A single-rate dataflow graph.                                                                                                                                                                                  | 94 |  |

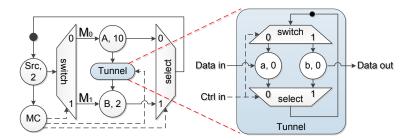

| Figure 5.2  | An MCDF graph and a basic tunnel.                                                                                                                                                                              | 95 |  |

| 0           |                                                                                                                                                                                                                |    |  |

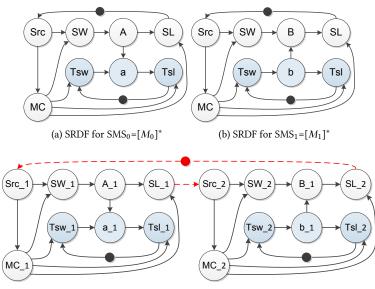

| Figure 5.3     | The equivalent SRDF of recurring SMS for the MCDF in Figure 5.2.                                                                                 | 96   |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 5.4     | Merging the equivalent SRDF graphs of SMS <sub>0</sub> and SMS <sub>1</sub> . This results in the equivalent SRDF graph of $[SMS_0   SMS_1]^*$ . | 97   |

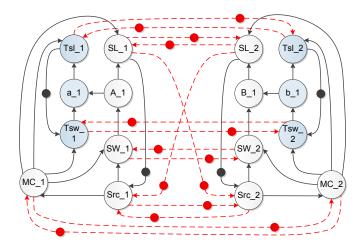

| Figure 5.5     | The execution of the merged equivalent SRDF graph shown in Figure 5.4.                                                                           | 98   |

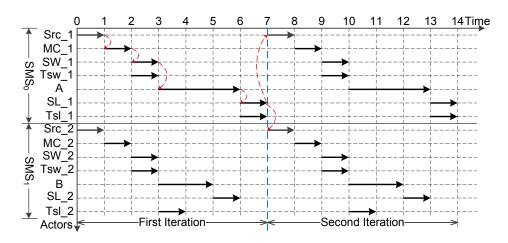

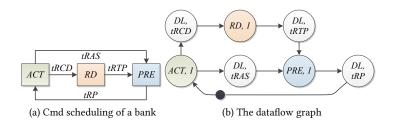

| Figure 5.6     | An example of dataflow modeling of commands to a bank.                                                                                           | 100  |

| Figure 5.7     | An overview of the MCDF modeling of memory controllers.                                                                                          | 100  |

| Figure 5.8     | Mode-controlled dataflow model of memory command sche-                                                                                           | 100  |

| 8              | duling                                                                                                                                           | 102  |

| Figure 5.9     | A generic mode tunnel with <i>M</i> inputs and <i>N</i> outputs                                                                                  | 105  |

| Figure 5.10    | A cascade tunnel structure to support multiple initial tokens                                                                                    |      |

| C              | for a specific set of modes.                                                                                                                     | 107  |

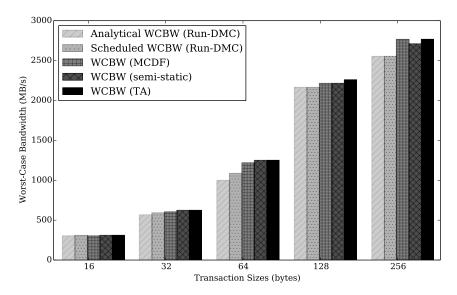

| Figure 5.11    | The WCBW given by different analysis approaches for DDR3-                                                                                        |      |

|                | 1600G SDRAM with fixed transaction size                                                                                                          | 112  |

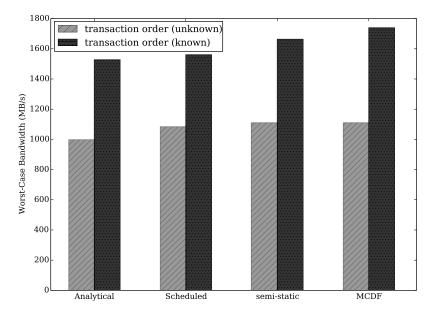

| Figure 5.12    | The WCBW given by different analysis approaches for DDR3-                                                                                        |      |

|                | 1600G SDRAM with known/unknown static order of variable                                                                                          |      |

|                | transaction sizes.                                                                                                                               | 113  |

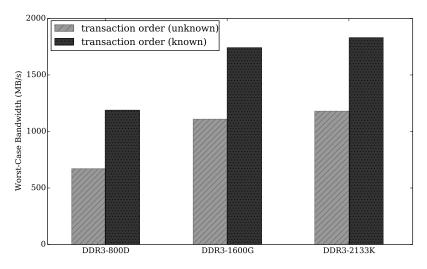

| Figure 5.13    | The WCBW achieved by MCDF model for DDR3 SDRAMs with                                                                                             |      |

|                | known/unknown static order of variable transaction sizes. $\ . \ .$                                                                              | 114  |

| Figure 6.1     | A Timed Automata model of producing and consuming trans-                                                                                         |      |

|                | actions                                                                                                                                          | 119  |

| Figure 6.2     | Abstracted overview of TA model for the dynamically-scheduled                                                                                    |      |

|                | memory controller Run-DMC.                                                                                                                       | 121  |

| Figure 6.3     | The TA templates for intuitively modeling the behavior of dy-                                                                                    |      |

|                | namic command scheduling within the Uppaal toolbox                                                                                               | 123  |

| Figure 6.4     | The optimized TA templates for modeling the behavior of dy-                                                                                      |      |

|                | namic command scheduling within the Uppaal toolbox                                                                                               | 128  |

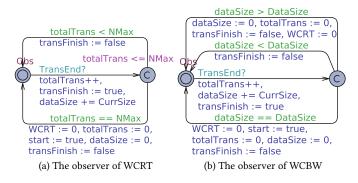

| Figure 6.5     | The TA to verify the WCRT and WCBW bounds.                                                                                                       | 131  |

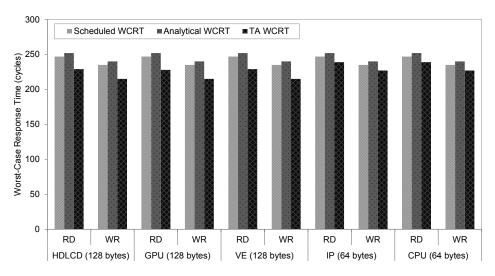

| Figure 6.6     | The WCRT for 4 requestors accessing DDR3-1600G with fixed                                                                                        |      |

|                | transaction sizes.                                                                                                                               | 137  |

| Figure 6.7     | The WCBW using different DataSize for fixed transaction sizes                                                                                    |      |

| <b>T</b> ! ( ) | with DDR3-1600G.                                                                                                                                 | 139  |

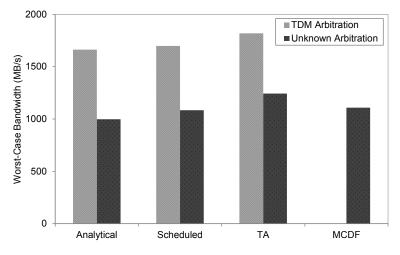

| Figure 6.8     | The WCBW for fixed transaction sizes.                                                                                                            | 140  |

| Figure 6.9     | The WCRT for the requestors in a HD video and graphics proc-                                                                                     | 1.40 |

| <b>F</b> :     | essing system [31] with variable transaction sizes                                                                                               | 142  |

| Figure 6.10    | The WCBW for variable transaction sizes.                                                                                                         | 143  |

# LIST OF TABLES

| Table 2.1 | Timing constraints (TC) for DDR3-1600G SDRAM [53]               | 15  |

|-----------|-----------------------------------------------------------------|-----|

| Table 3.1 | Characterization of memory traffic with fixed transaction size. | 46  |

| Table 3.2 | Characterization of memory traffic with variable transaction    |     |

|           | sizes                                                           | 52  |

| Table 4.1 | Summary of notation                                             | 61  |

| Table 6.1 | Comparison between the intuitive and optimized TA model         | 129 |

| Table C.1 | Different configurations for Run-DMC with variable sizes        | 180 |

| Table C.2 | WCBW (MB/s) and WCRT (cycles) of different DDR3 SDRAMs          |     |

|           | with fixed transaction size.                                    | 181 |

# 1

### INTRODUCTION

In the 20th century, one of the greatest inventions was the Internet [9], which connects people and delivers information worldwide. Now, we are in 2016 and what can be expected for the future is that a massively connected world beyond the Internet will be built, where everything will be connected, leading to the *Internet of Things (IoT)* [41]. The connected world will be much more cooperative, productive, and intelligent. Similarly to the Internet where computers are the fundamental components, embedded platforms will be the "heart" of "things", such as our digital watch, mobile phones, navigation systems, factory controllers, and the computers inside cars and aircraft. Embedded platforms are designed for a particular purpose and interact with physical mechanical or electrical systems by running their applications, which often have *real-time requirements* [19], such as a time deadline or a processing throughput requirement. These requirements may be associated with the safety or mission of the system and must hence be satisfied.

To satisfy the requirements of the real-time applications, the embedded platform has to provide guaranteed performance [11], such as a worst-case execution time and/or a minimum throughput. However, it is challenging to achieve this goal because of the complexity of embedded platforms, which are composed of an increasing number of resources, such as processing cores, hardware accelerators, memories, I/O interfaces, and peripherals. Moreover, the platform supports both real-time and non-real-time applications [2, 16], and the resources in the platform are shared between all the applications. Guaranteed performance must be given to real-time applications, such that their requirements are always satisfied, while good average performance is needed by non-real-time applications to feel responsive.

Synchronous Dynamic Random-Access Memory (SDRAM) is one of the most shared resources in an embedded platform and has great impact on satisfying the requirements of applications [60]. It is accessed by memory *requestors*, such as cores, hardware accelerators, and *direct memory access* (DMA) modules, via a memory controller. Since multiple applications execute concurrently in the platform, the requestors generate *diverse traffic* for the memory controller, which receives arbitrarily-mixed read/write transactions with variable sizes. Moreover, the memory addresses of transactions correspond to different internal locations of the SDRAM, resulting in complex interferences between transactions. This thesis focuses on design and formal analysis of real-time memory controllers, which efficiently deal with the diverse memory traffic.

This chapter starts with Section 1.1, which introduces real-time embedded systems. The requirements of applications are discussed, followed by a brief introduction of the main memory sub-system in an embedded hardware platform. The problems of designing and analyzing of real-time memory controllers are given in Section 1.2. In Section 1.3, we briefly discuss how our contributions address the raised issues.

#### 1.1 REAL-TIME EMBEDDED SYSTEMS

This section investigates some general trends in the application requirements, modern multi-core hardware platforms, and main memory subsystems. In particular, the main memory subsystem is presented in more detail, since it is the basis of the work in this thesis.

#### 1.1.1 Application Requirements

There is a variety of applications running on modern multi-core embedded platforms, including hard/soft real-time and non-real-time applications [61]. The hard real-time applications have deadlines that must always be respected. For example, a longitudinal flight controller adjusts the longitude of an aircraft by changing its speed within a given time period [83]. It is unacceptable to miss a deadline, since it can cause catastrophic consequences, such as an aircraft crash and the loss of lives. In contrast, soft real-time applications are not safety critical, and certain deadline misses are tolerable, though they are highly undesirable. One or more overrun deadlines for soft real-time applications may result in temporary quality/service degradation, but will not lead to a catastrophe. For example, displaying a video stream on mobile devices can accept occasional dropped frames, which have a little negative effect on the *Quality of Service (QoS)* for the users [106]. Finally, non-real-time applications, such as web browsing [89], do not have any timing constraints and can tolerate occasional slow response times. However, they have to be fast enough to keep the user happy and have a good average performance.

This thesis focuses on how to provide guaranteed performance for the main memory, such as the *worst-case response time* and *bandwidth*. The worst-case response time is the maximum latency experienced by a transaction in the memory controller. The worst-case bandwidth represents the minimum data transfer rate of the memory controller over a long time period. They are used to satisfy the requirements imposed by the hard real-time applications on the memory subsystem. In this thesis, we do not distinguish soft real-time and non-real-time applications. The reason is that soft real-time applications are typically supported by just providing good enough average performance. Note that this thesis does not address the issues of how to efficiently allocate resources (e.g.,

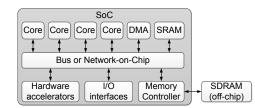

Figure 1.1: An example of a multi-core hardware platform.

memory space, bandwidth) to the applications, such that their requirements are satisfied. There exist solutions in [8, 46, 77] to solve these issues.

#### 1.1.2 Multi-Core Hardware Platforms

With the advances in semiconductor technology with respect to shrinking transistor dimensions, an increasing number of transistors are integrated on a single chip [57]. This high density of transistors makes it possible to integrate multiple cores in a *System-on-Chip* (*SoC*). As a result, a large amount of off-chip circuitry can be moved from printed circuit boards to integrated circuits. This allows manufactures to produce smaller boards, while simplifying the board layout and routing, reducing power consumption and cost [54]. It also reduces the complexities involved in high-speed board design. Due to the abundant resources on a chip, it allows multiple applications to be executed concurrently.

Multi-core platforms have been widely used in almost all present electronic systems, such as consumer electronics [60, 103], telecommunication systems [14], and automotive systems [17]. They are also promising for use in avionics [82]. Multi-core platforms executing multiple applications usually consist of various heterogeneous hardware resources. Figure 1.1 presents an example of a general hardware platform, which can be used for smart phones [86, 104] for instance. It contains a number of processing cores, on-chip static random-access memory (SRAM), hardware accelerators, DMAs, I/O interfaces, and also the off-chip memory (i.e., SDRAM), etc. The cores can be either used to perform general-purpose computation [49] or digital signal processor (DSP) cores for numerical manipulation of signals [78]. Hardware accelerators are specialized for accelerating specific functions [102]. For example, video or audio engines are often implemented using hardware accelerators [76]. The on-chip SRAM is fast and used for the cache or scratchpad. However, the capacity of the SRAM cannot be large, e.g., maximally a few megabytes, because of the relatively high cost per bit (i.e., 6 transistors for one bit). The off-chip SDRAM is used as main memory. It has much larger capacity up to gigabytes, since only one transistor and one capacitor are needed for one bit, thus consuming less area. However, SDRAM is slower than SRAM and has to be periodically refreshed to prevent data loss, as the capacitor suffers from leakage. The SDRAM is shared by other resources to read or write data via a memory controller integrated

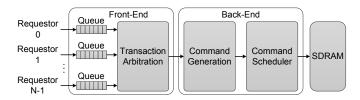

Figure 1.2: An abstracted view on a typical memory controller.

in the SoC. The on-chip interfaces for I/O devices manage video streams or data from Ethernet network. These on-chip resources are interconnected by a communication in-frastructure, such as a bus or a *network-on-chip* (*NoC*) [33].

The hardware resources in a platform allow an application to be parallelized by running tasks on multiple processors simultaneously [94, 99]. Multiple applications can be deployed in the platform at the same time by sharing the resources. As a result, complex interferences between applications rise due to shared resources in the platform. When one application accesses a resource, other applications requiring the same resource have to wait. This impacts their ability to satisfy the timing constraints. In particular, SDRAM is a very commonly shared resource by the requestors, such as cores, hardware accelerators, DMAs, which generate diverse memory traffic. This makes the design and analysis of memory controllers challenging.

Next, we will focus on the memory subsystem and introduce how a memory controller serves transactions generated by different requestors.

#### 1.1.3 Main Memory Subsystem

The memory subsystem is typically hierarchically organized in a SoC. The on-chip caches (e.g., L1/L2/L3 caches) are closer to the processor, such that it operates without suffering the long latency of reading data from the main memory, i.e., off-chip SDRAM. When the required data is not stored in the cache, e.g., a last-level cache miss, the processor generates a transaction (i.e., memory request) to read data from the SDRAM via the memory controller. When data must be stored, a write transaction is generated by the processor and sent to the memory controller, which forwards the data to the SDRAM. Similarly, other processing elements (e.g., hardware accelerators) may use DMA or specific circuit logic to manage their memory transactions and read/write data from/into the SDRAM via the memory controller.

SDRAM is a very popular volatile memory and is used for temporary data storage. It is accessed via the on-chip memory controller, which is typically partitioned into a *front-end* and a *back-end*, as shown in Figure 1.2. The front-end receives transactions from different requestors, and decides in which order to serve them. Its architecture is composed of *queues* for transactions per requestor and an arbiter to schedule each transaction to the back-end. The transaction is then executed by sending instructions (i.e., memory

commands) to the SDRAM, such that internal actions are triggered, e.g., reading or writing. In essence, the back-end translates the transaction into commands with the *command generator*, as presented in Figure 1.2. Once commands are generated, they are scheduled for execution in the SDRAM by a *command scheduler*, also shown in Figure 1.2. Note that commands are scheduled through a command bus to the SDRAM, where only one command can be transferred per clock cycle. Although the front-end and back-end are conceptually separate, interaction exists between them. For example, the front-end arbitration between requestors can be triggered by the back-end when a specific command is scheduled. Moreover, depending on the implementation, the transaction-level arbitration in the front-end can be combined with the command-level scheduling in the back-end.

The external SDRAM is typically viewed as a black-box to simplify its internal complexities [21, 29, 91, 109]. However, SDRAM is structured with multiple banks (i.e., memory arrays), which are controlled by memory commands. Commands can be executed on multiple banks simultaneously. This results in so-called bank parallelism [59], which supports the pipelining between transactions by executing their commands corresponding to different banks at the same time. The command scheduling is also complex. The reasons include: 1) it has to respect an internal *finite-state machine* that specifies the valid orders of executing commands, and 2) commands are executed subject to the *timing constraints*, such that the SDRAM can work properly. 3) When multiple commands are available for execution, e.g., all time constraints are satisfied for them, the scheduler has to choose one of them and sends to the SDRAM via the command bus. This is called a *collision* between these executable commands. The occurrence of collisions is unpredictable, because it is hard to know when the timing constraints are satisfied for multiple commands at the same time. Therefore, it is hard to predict the scheduling of a command, and thus bounding the memory performance is a challenging problem.

#### 1.2 PROBLEM STATEMENT

This section discusses the two main problems solved in this thesis. The first problem is *how to design* memory controllers to efficiently deal with the diverse memory traffic in a heterogeneous multi-core hardware platform. The following problem is *how to analyze* the timing behavior of the memory controller and provide guaranteed performance in terms of worst-case response time and bandwidth. These worst-case results can be further integrated into system-level analysis of the application. For example, the worst-case response time for the SDRAM can be integrated as the cache miss penalty into the worst-case execution time estimation tools of applications [11]. In addition, they can be also integrated into a system-level analysis using dataflow formalism [80]. Although this is an important topic, the integration of worst-case results into a high-level analysis of real-time applications is outside the scope of this thesis.

#### 6 INTRODUCTION

#### 1.2.1 Problem I: Real-Time Memory Controller Design

In modern multi-core systems, we see two relevant trends. 1) Both real-time and nonreal-time applications are deployed at the same time in the same SoC [2, 16]. As discussed in Section 1.1.1, the former require guaranteed performance, while the latter should be given good average performance to feel responsive. 2) An increasing number of heterogeneous hardware resources are integrated in a system. The external SDRAM is shared by all resources, which result in diverse memory traffic in terms of arbitrarilymixed read and write transactions with variable sizes and different physical addresses, as discussed in Section 1.1.2. These trends pose the following requirements on a memory controller: *it has to efficiently deal with the diverse traffic, while being analyzable to bound its performance, such that the requirements of real-time applications can be satisfied. Moreover, the memory controller should also give good average performance to non-real-time applications.*

A memory controller faces diverse memory traffic from different requestors executing tasks of real-time and/or non-real-time applications. The front-end of the memory controller needs an arbiter to schedule transactions from different requestors. However, *it is hard to choose a proper arbiter*. First, requestors have different requirements in terms of worst-case response time and/or bandwidth because of the applications being executed. The arbiter has to distinguish these differences between requestors. As a result, the widely used *round-robin (RR)* arbiter [85] is not always applicable, since requestors are served in a cycle, and each of them is given an equal opportunity to access the memory. A TDM arbiter [37] can allocate different number of time slots to requestors based on their requirements. However, a requestor needs many slots to satisfy its tight response time requirement [77]. This problem can be overcome by fixed-priority based arbiters by giving different priorities to requestors according to their response time requirements [55, 56]. However, this may result in starvation when a requestor is always overtaken by a prioritized requestor.

The back-end of a memory controller executes transactions by generating and scheduling commands to SDRAM subject to the timing constraints. There exists state-of-theart real-time memory controllers [3, 25, 39, 88], which use pre-computed static command schedules to execute transactions, such that their analyses are easy. Intuitively, each transaction is executed by picking up commands from the static schedules and sequentially sending them to the SDRAM. Since the schedules are statically designed, they only support a fixed transaction size and cannot exploit the run-time state of the SDRAM. However, transactions in the diverse traffic need to be *dynamically* executed, since they have variable sizes. Moreover, the run-time state of the SDRAM can be exploited to achieve good performance. We can imagine that different numbers of commands are needed by the variable-sized transactions, since a read/write command executed by SDRAM triggers a data burst of fixed size. Moreover, other commands are also needed to manage the banks of SDRAM. Therefore, *the question is what kind of commands and how many of them should be generated for each transaction*. This question relies on the mechanisms used by the back-end. For example, a memory transaction can read/write data bursts from/into multiple banks rather than a single one, resulting in parallel accesses to different banks.

The scheduling of commands has to enable correct execution of commands based on the internal finite-state machine of SDRAM, while satisfying their timing constraints. It is difficult for the scheduler to make a decision, because 1) the execution of a command can be fast or slow depending on the relevant timing constraints and the current state of the SDRAM. 2) The execution of the current command influences future commands, resulting in command-level interferences. 3) The interferences between transactions are complex, because their commands to different banks can be scheduled in a pipelined manner. Therefore, it is challenging to design an efficient memory controller to deal with the diverse memory traffic. Finally, the memory controller must be analyzable, such that the worst-case response time and bandwidth can be derived. The analysis challenges will be discussed in the next section.

#### 1.2.2 Problem II: Real-Time Memory Controller Analysis

This thesis focuses on analyzing the worst-case response time and bandwidth for the SDRAM. However, the main difficulty is the complex interferences between requestors, transactions, and commands. The response time of a transaction in the memory controller starts when it arrives at the front-end. Then it may experience a delay caused by other requestors, whose transactions may be executed first. The interference between requestors is highly dependent on the arbitration mechanism used in the front-end of the memory controller. It can be RR, TDM, or priority-based arbitrations, such as creditcontrolled static-priority arbitration (CCSP) [5] and frame-based static priority (FBSP) [6]. When the transaction is scheduled and is sent to the back-end, it is executed in pipelining with the previous transaction, resulting in interferences between transactions. Finally, the data transmission is triggered when the read/write commands are executed by SDRAM. Hence, it is hard to analyze for how long time a transaction is executed. Within this time, a fixed amount of data corresponding to the transaction size is transferred. It is even more difficult to extend this analysis to a sequence of arbitrary transactions corresponding to a larger data volume. As a result, the long-term bandwidth measured by the execution times of transactions divided by the transferred data is more difficult to obtain.

#### 1.3 THESIS CONTRIBUTIONS

This section introduces our solutions to solve the two critical issues of design and analysis of real-time memory controllers.

- 1. We design a **d**ynamically-scheduled **m**emory **c**ontroller, which efficiently deals with the diverse memory traffic at **run**-time and offers guarantees as well as good average performance. We refer to this memory controller as *Run-DMC* and it is introduced in Chapter 3.

- 2. To analyze the worst-case response time and bandwidth of Run-DMC, three analysis approaches are proposed.

- A formal analysis approach uses a mathematical model to compute the time, at which each command is scheduled by Run-DMC. To address the complex interferences between transactions, it applies two simplifying assumptions to provide the worst-case initial bank state for an arbitrary transaction. Then the bounds on the worst-case response time and bandwidth are computed, and they are formally proved to be conservative. This formal analysis approach is given in Chapter 4.

- A dataflow model is proposed to provide better bounds in an easier way than the formal analysis approach. It naturally captures the dependencies of scheduling commands by Run-DMC, and an existing analysis tool is used to automatically derive the bound on worst-case bandwidth. This approach eliminates one of the assumptions used in the formal analysis approach, resulting in a better bound. Moreover, the bound is easier to obtain, since it does not rely on complex manual proofs used by the previous approach. This approach is presented in Chapter 5.

- The third approach continues modeling Run-DMC in Chapter 6, where a timed automata model is proposed to accurately describe the timing behavior of Run-DMC without any simplifying assumptions. The bounds on both worst-case response time and bandwidth are derived using model checking with an existing tool. This approach performs equally well as or better than the previous approaches to derive the bounds.

- 3. All the three analysis approaches are used to analyze the same memory controller (i.e., Run-DMC). This allows us to investigate their strengths and weaknesses in Chapter 7.

- 4. Finally, the formal analysis approach has been implemented as an open-source tool *RTMemController* [70] to evaluate both the average-case and worst-case performance of Run-DMC. Moreover, the TA model is also publicly available on-line [73].

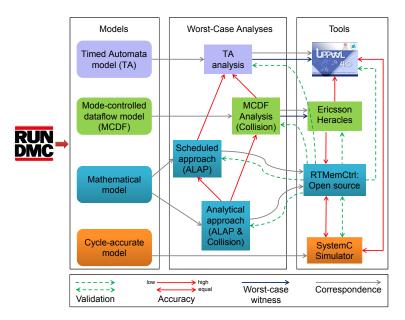

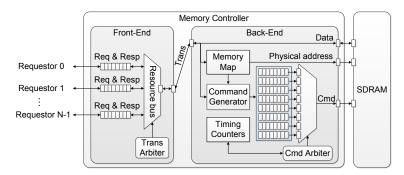

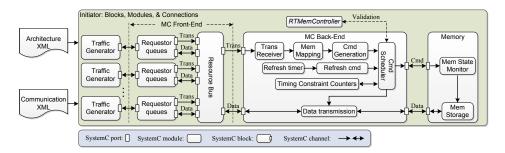

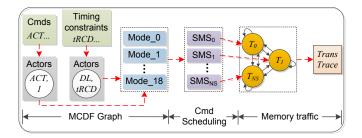

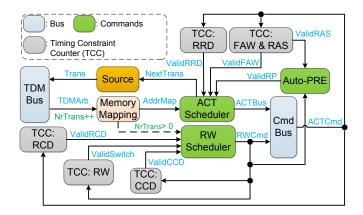

Figure 1.3 shows an overview of the development of Run-DMC, including its implementation, simulation, validation, and verification, by using different models and tools. We proceed by explaining each contribution and Figure 1.3 in more detail in the following sections.

Figure 1.3: The development of our dynamically-scheduled memory controller Run-DMC.

#### 1.3.1 Run-DMC: a Dynamically-Scheduled Real-Time Memory Controller

To efficiently deal with the diverse memory traffic, we design a memory controller to execute transactions with variable sizes by dynamically scheduling commands to the SDRAM according to the run-time SDRAM state and timing constraints. Its architecture is composed of a front-end and a back-end. The front-end uses a novel TDM arbiter to serve requestors with variable transaction sizes. The TDM slots hence have variable lengths. Moreover, it is flexible to meet the requirements of requestors by allocating different number of time slots to each requestor, while being easy to analyze. The two novelties to reduce the worst-case response time are that 1) idle slots (i.e., no transactions from the requestor) are skipped rather than being reallocated. This reduces the interference delay between requestors, since the requestor serve are served in descending order of their transaction sizes. The reason is that transactions pipeline better following a larger transaction than a smaller one.

To avoid complexity while still being efficient, the back-end dynamically generates commands based on the transaction type (i.e., either read or write), size, and physical address. It schedules commands based on an algorithm that uses a *first-come first-serve (FCFS)* scheme to execute transactions in-order, while it supports pipelining between successive transactions. Moreover, scheduling collisions occurring when multiple commands are executable at the same time are avoided by prioritizing the read/write

commands over others. The reason is that the read/write commands trigger data transmission, and giving higher priorities to them intuitively provides good performance. The proposed memory controller will be introduced in Chapter 3. It has been implemented as a cycle-accurate SystemC model, as shown in Figure 1.3. It is the basis of validating the analysis models of Run-DMC.

#### 1.3.2 Formal Analysis of Run-DMC

As discussed in Section 1.2.2, the analysis of a memory controller that pipelines commands across transactions is difficult because of the complex interferences between requestors, transactions, and commands. We propose a formal analysis approach to overcome this problem by partitioning it into two parts, where 1) interferences between requestors are analyzed in the front-end of Run-DMC that uses our novel TDM arbiter, and 2) the analysis of the back-end covers the interferences between commands. In particular, the back-end analysis bounds the maximum length of each time slot used by the TDM arbiter. The formal analysis approach will be presented in Chapter 4.

To carry out the worst-case analysis, we firstly propose a formalization to accurately capture the scheduling times of commands. This formalization has been implemented as an open-source C++ tool, named *RTMemController* [70]. It is validated by the SystemC simulator, ensuring accurate command scheduling times (see Figure 1.3). Therefore, the timing behavior of *RTMemController* is equivalent to the SystemC model of the memory controller. Due to the equivalence, *RTMemController* will be used to validate the other analysis models of Run-DMC.

Based on the formalization, the worst-case execution time experienced by a transaction in the back-end is analyzed. The difficulty is that the execution of the current transaction depends on the previously scheduled commands corresponding to earlier transactions. We employ two conservative assumptions to eliminate the impact of these earlier transactions. The first assumption is that the commands of the previous transactions were scheduled as-late-as-possible (ALAP), resulting in the maximum possible scheduling times of the previous commands. This provides the worst-case initial SDRAM state for the current transaction. Moreover, Run-DMC prioritizes read/write commands over others. When there is a collision between them, these commands with lower priority are delayed. Since the collisions are unpredictable, the analysis has to conservatively assume that they always occur for the low-priority commands. Then the formalization can compute the maximum scheduling times of commands for the current transaction, resulting in the worst-case execution time in the back-end. This is the so-called *analytical* approach, as shown in Figure 1.3. To achieve lower worst-case execution time, RTMem-*Controller* is used to actually detect the command collisions for the current transaction, while the scheduling times of the previous commands are still given using ALAP scheduling. As a result, this scheduled approach hence outperforms the analytical approach. Both of them are included in RTMemController. Finally, we compute the worst-case bandwidth based on the worst-case execution time, with which a fixed amount of data is transferred. In addition, the worst-case response time in the front-end is calculated according to the static TDM slot allocation, where the period of each slot equals to the relevant worst-case execution time.

#### 1.3.3 Dataflow Modeling of Run-DMC

Run-DMC schedules commands subject to the SDRAM finite-state machine and the timing constraints, which result in dependencies between commands. These dependencies have already been captured by the formalization. However, its worst-case analysis provides pessimistic results because of the conservative assumptions. Moreover, the analysis is based on manual proofs that are very time-consuming to make. As a result, it is difficult to extend the formal analysis approach to different memory controllers or SDRAM devices. Dataflow models naturally capture dependencies and existing tools can be used to derive the worst-case results by automatically analyzing the model. Therefore, we switch the effort from formal analysis to modeling the timing behavior of the memory controller and derive the worst-case results by analyzing the model with existing techniques and tools.

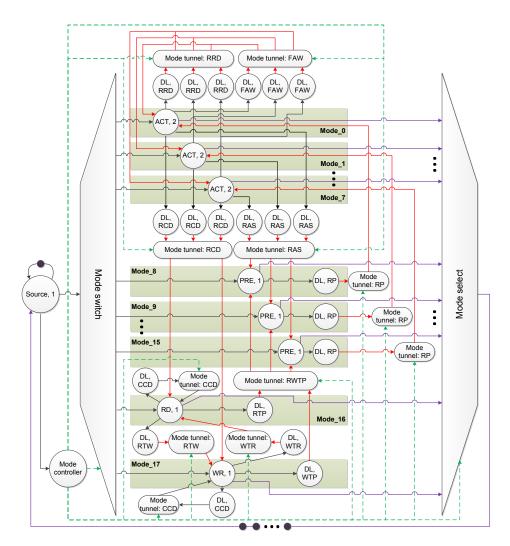

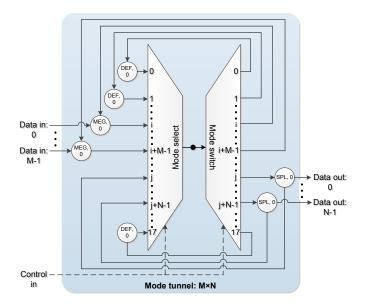

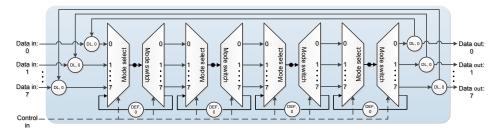

We propose a *mode-controlled dataflow* (*MCDF*) model that captures the dependencies of dynamic command scheduling for Run-DMC. Existing dataflow analysis techniques implemented in the Ericsson's Heracles tool [79] are used to derive the worst-case results. The MCDF model will be introduced in Chapter 5. In the MCDF model, memory commands are represented by actors. The SDRAM timing constraints are captured by the execution time of actors, while the dependencies are described by edges between actors. A mode corresponds to a subset of the dataflow graph and the dynamism in the memory traffic in terms of different transactions can be captured by dynamically selecting different modes.

The MCDF model is executable and supports simulation of the memory controller. We use this to validate the MCDF model with the open-source tool *RTMemController*, which provides identical scheduling times of commands for the same transaction traces. The analysis of the MCDF model provides the minimum throughput of executing transactions after determining the critical sequence of transactions. The minimum throughput can be converted into the worst-case/minimum bandwidth (WCBW). The WCBW is determined by analyzing sequences of transactions rather than a single transaction. The former supports exploiting the pipelining between transactions, while the latter used by the formal analysis approach does not. Therefore, the MCDF model can provide better WCBW results in a more convenient way using existing analysis tool. The experimental results demonstrate that the MCDF model outperforms the formal analysis approach. However, similarly to the analytical approach in the formal analysis, the MCDF model conservatively assumes command collisions to avoid non-deterministic variations in the dataflow model. It uses the actual scheduling times of command rather

#### 12 INTRODUCTION

than the ALAP scheduling, as shown in Figure 1.3. Moreover, the Heracles tool is only capable of proving the WCBW, as analysis of worst-case response time is not supported.

#### 1.3.4 Timed Automata Modeling of Run-DMC

To overcome the drawbacks of the previous MCDF model, we continue modeling Run-DMC using a different model, which is based on *timed automata (TA)* [15]. The opensource tool Uppaal [13] is used to carry out the modeling, simulation, and verification. In particular, the worst-case response time and bandwidth can be automatically obtained by exhaustively exploring the state space via model checking with Uppaal.

We have developed a modular TA model of our dynamically-scheduled memory controller without any simplifying assumptions, as shown in Figure 1.3. The TA model will be given in Chapter 6. The timing behavior of each component (e.g., TDM arbiter, command generator, command scheduling) is accurately described by a TA. The accuracy has been validated by simulating the TA model with given transaction traces using Uppaal, and also feeding these traces to the open-source *RTMemController*. Identical scheduling times of commands are obtained in these two ways, which suggests that the TA model accurately captures the timing behavior of Run-DMC.

Model checking exhaustively explores the state space, which automatically includes the complexities of interferences between requestors, transactions, or commands, whether they occur in the front-end or back-end. Therefore, the proposed TA model is capable of 1) providing tight worst-case results, which are validated easily. The reason is that Uppaal provides a diagnostic transaction trace (i.e., witness) for each result. The experimental results demonstrate that the TA model gives better worst-case results than these previous approaches. 2) It can be easy to extend to other memory controllers, since the TA of the common components can be reused.

# 2

# BACKGROUND & TERMINOLOGY

This chapter sets the stage on which the following chapters will play out. The SDRAM is introduced in Section 2.1, including its architecture and memory commands as well as the timing constraints between commands. SDRAM is connected to the memory controller with the command, address, and data buses. It executes commands scheduled by the memory controller, which coordinates between the memory requestors (e.g., processors, GPU, DMA, hardware accelerators) and the SDRAM. Section 2.2 will introduce the general functionalities of a memory controller, which are partitioned into a front-end and a back-end. The front-end receives transactions from different requestors, which are served by an arbiter. When a transaction is sent to the back-end, a number of commands are generated, and are sequentially scheduled to the SDRAM via the command bus without violating any timing constraints. Finally, to formalize the command scheduling for an individual transaction, the relevant timings are defined in Section 2.3, followed by the metrics to evaluate the performance of the memory controller. The metrics include the execution time in the back-end, the response time, and the bandwidth provided by the memory controller.

#### 2.1 SDRAM ARCHITECTURE AND OPERATION

#### 2.1.1 SDRAM Architecture

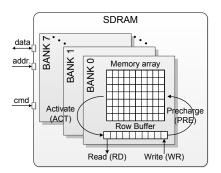

The off-chip SDRAM is a very popular volatile memory and used as temporary data storage. An SDRAM chip comprises a set of banks, e.g., a contemporary DDR3 SDRAM chip typically has 8 banks. A bank contains a memory array consisting of elements arranged in rows and columns [51], as shown in Figure 2.1. The banks can work in parallel. However, they share the same interface consisting of command, address, and data buses. As a result, only one command or data word can be sent to one bank at a time. The command bus transfers a single command per clock cycle, while the data bus transfers two data words per cycle for a *double data rate (DDR)* memory. Moreover, the data bus is bidirectional and used to both read and write data. The address bus transfers the physical address in terms of bank, row, and column for each command. To issue a command, several timing constraints have to be satisfied, as specified by the JEDEC

Figure 2.1: SDRAM architecture

DDR3 standard [53]. Timing constraints guarantee that the SDRAM can properly execute the received commands. Note that although this thesis focuses on DDR3 SDRAMs, it requires only minor adaptations to work with other types of SDRAMs, such as DDRx, LPDDRx and Wide I/O.

# 2.1.2 SDRAM Commands and Timing Constraints

An SDRAM executes commands, which mainly include *Activate (ACT), read (RD), write (WR), precharge (PRE), refresh (REF)*, and *no operation (NOP)*. The execution of commands has to satisfy SDRAM timing constraints, as summarized in Table 2.1. The commands work as follows:

- An *ACT* command opens a row in a bank, i.e., moves the data in the row into the row buffer of the bank (see Figure 2.1). It makes the data available for subsequent *RD* or *WR* command(s). This activation takes *tRCD* cycles, as indicated in Table 2.1. The *ACT* command is accompanied by the addresses of the required bank and row.

- When data is available in the row buffer, a *RD* or *WR* command triggers reading or writing a burst of data from a range of columns in the open row. The *burst length* (*BL*) is 8 words for DDR3 SDRAMs. The first bit of the required data appears on the data bus *tRL* cycles after issuing a *RD* command, while it is after *tWL* cycles for a *WR* command. The DDR3 SDRAM transfers two words per cycle. As a result, a data burst occupies the data bus for *BL*/2 cycles. When more data bursts are needed, a number of *RD* or *WR* commands can be issued to SDRAM. Each *RD* or *WR* command is accompanied by the address of the first column of the data burst. The address is aligned with *BL*, i.e., address (in words) modulo *BL* = 0.

- Once reading/writing is finished, a PRE command is issued to close the open row, i.e., the data in the row buffer is stored back to the original row in the bank. Subsequently, a different row in the bank may be opened. The timing constraints to

issue a *PRE* command include *tRAS* after an *ACT* command, *tRTP* after a *RD* command, and *tWTP* and *tWR* after a *WR* command. They are shown in Table 2.1. A *PRE* command can be either explicitly issued via the command bus or by adding an auto-precharge flag to the previous *RD* or *WR* command, such that precharging is automatically triggered when all timing constraints are satisfied. The latter is called an auto-precharge policy. The precharging duration is *tRP* cycles.

- Since SDRAM is volatile, it has to be periodically refreshed every *tREFI* cycles to retain the data. A *REF* command is issued after all open rows are closed. The period of refreshing (*tRFC*) depends on the capacity of the SDRAM and the operating temperature. Table 2.1 assumes a capacity of 2 Gb and a fixed operating temperature range, i.e., 0 °C to 85 °C [53].

- Finally, a NOP command is issued when waiting until timing constraints are satisfied, or when no commands have to be executed. NOP does nothing.

|       | 0 ( )                                                                                                                    |        |

|-------|--------------------------------------------------------------------------------------------------------------------------|--------|

| TC    | Description                                                                                                              | Cycles |

| tCK   | Clock period                                                                                                             | 1      |

| tRCD  | Minimum time between ACT and RD or WR commands to the same bank                                                          | 8      |

| tRRD  | Minimum time between ACT commands to different banks                                                                     | 6      |

| tRAS  | Minimum time between ACT and PRE commands to the same bank                                                               | 28     |

| tFAW  | Time window in which at most four banks may be activated                                                                 | 32     |

| tCCD  | Minimum time between two RD or two WR commands                                                                           | 4      |

| tWL   | Write latency. Time after a <i>WR</i> command until first data is available on the bus                                   | 8      |

| tRL   | Read latency. Time after a <i>RD</i> command until first data is available on the bus                                    | 8      |

| tRTP  | Minimum time between a RD and a PRE command to the same bank                                                             | 6      |

| tRP   | Precharge duration time                                                                                                  | 8      |

| tWTR  | Internal WR command to RD command delay                                                                                  | 6      |

| tWR   | Write recovery time. Minimum time after the last data word has<br>been written to a bank until a precharge may be issued | 12     |

| tRFC  | Refresh period time                                                                                                      | 128    |

| tREFI | Refresh interval                                                                                                         | 6240   |

#### Table 2.1: Timing constraints (TC) for DDR3-1600G SDRAM [53].

#### 2.1.3 Command Scheduling

An SDRAM operates on commands, which can be scheduled in various ways by the memory controller. This section firstly provides a simplified state diagram, which gives

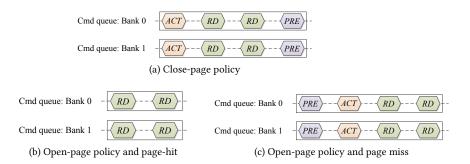

Figure 2.2: Simplified state diagram of scheduling commands.

an overview of the possible orders of scheduling commands to a single bank or multiple banks, respectively. Then, we introduce several concepts for command scheduling, including 1) page policy, 2) command pipelining, and 3) bank interleaving.

# 2.1.3.1 State Diagram of Scheduling Commands

Following the descriptions of how commands work in the previous section, we can straightforwardly draw Figure 2.2 that presents a state diagram to show the valid orders of scheduling commands. To access a single bank, it implies the following situations:

- SDRAM can read/write one or more data bursts only if the row is open. This requires an *ACT* command followed by one or multiple *RD/WR* commands. It is captured by the transition from the ACT state to the RD/WR state in Figure 2.2. In addition, RD/WR state has a self-transition, which means multiple *RD/WR* commands can be issued in a sequence.

- Precharging is performed after reading or writing is complete, resulting in the transition from the RD or WR state to the PRE state. The transition from PRE to ACT in Figure 2.2 shows that opening a new row in the bank is after closing the previous row.

- Finally, the SDRAM can be refreshed when the row is closed, and thus there is a transition from PRE to REF in Figure 2.2. Since SDRAM is allowed to execute a group of refreshes, the REF state consists of a self-transition. It implies that a new *REF* command can be scheduled after another one subject to the timing constraints.

In addition to the transitions of scheduling commands to a single bank, additional transitions in Figure 2.2 illustrate the possible orders of scheduling commands to different banks. For example, two *ACT* commands can be scheduled to two different banks successively, since banks work in parallel. This is depicted by the self-transition of the ACT state in Figure 2.2.

#### 2.1.3.2 Page Policies