Magisterarbeit

# Design and Implementation of a Memory Controller for Real-Time Applications

Markus Ringhofer

Institut für Technische Informatik Technische Universität Graz Vorstand: O. Univ.-Prof. Dipl.-Ing. Dr. techn. Reinhold Weiß

Begutachter: O. Univ.-Prof. Dipl.-Ing. Dr. techn. Reinhold Weiß Betreuer: Ass.-Prof. Dipl.-Ing. Dr. techn. Christian Steger

Eindhoven und Graz, im September 2006

# Abstract

A memory controller is proposed where the behavior is predictable and which can be used for real-time systems. The memory controller is designed to be used in any system where a predictable memory controller is required, but integrates very well with Æthereal. It offers predictability per flow, which guarantees minimum bandwidth and maximum latency, without the necessity of simulation. Furthermore, the memory controller translates the peak memory bandwidth (gross bandwidth) to a net bandwidth, which is the effective available bandwidth for the IP blocks. The proposed solution has a worst-case gross-tonet bandwidth translation efficiency of 80%. The maximum latency for the highest priority requestor is 375ns. The memory controller is synthesized for CMOS12 and results in a small scalable memory controller with  $0.04mm^2$  for 6 requestors.

Keywords: Memory Controller, Network-on-Chip, DDR2, SDRAM

# Acknowledgments

This thesis was written at the Institute of Technical Informatics at the Graz University of Technology in cooperation with the Embedded Systems Architecture on Silicon Group at Philips Research in Eindhoven, The Netherlands.

I would like to acknowledge Dr. Kees Goossens for supervising me during my stay at Philips Research. I would also like to thank Benny Åkesson for the close collaboration throughout the course of this project.

I also owe my gratitude to Prof. Lambert Spaanenburg for organizing the road trip from Lund University to Philips Research, which resulted in an internship opportunity at the Philips Research Labs and thus leading to this thesis. Furthermore, I thank him for the supervision on the thesis. Special thanks go to Vince as well, who as a work mate and a friend, made coffee breaks and lunches more fun.

## Danksagung

Diese Diplomarbeit wurde im Studienjahr 2005/06 am Institut für Technische Informatik an der Technischen Universität Graz und in der Gruppe Embedded Systems Architectur on Silicon bei Philips Research in Eindhoven (Niederlande) durchgeführt.

Spezieller Dank geht an meinen Betreuer Herrn Ass.-Prof. Dr. Christian Steger von der TU Graz für die akademische Betreuung.

Bedanken darf ich mich auch für die Unterstützung und das Verständis von meiner Freundin Sophie. Bei meinen drei besten Freunden Günter, Herbert und Wolfgang bedanke ich mich fuer die netten Gespräche und für gelegentliche gemeinsame Bierchen. Vielen Dank auch an Andy, Karin und Thomas, die in ihrer Wohnung immer Platz für mich hatten, wenn ich in Graz war.

Im Speziellen bedanke ich mich bei meinen Eltern, Erwin und Maria, die mich in meinen Entscheidungen stets bestärkt haben, und auf deren Unterstützung ich mich immer verlassen konnte.

# Contents

| 1        | Intr              | oducti | on 1                                        |  |  |  |  |  |  |  |  |  |  |

|----------|-------------------|--------|---------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|          | 1.1               | Motiva | ation                                       |  |  |  |  |  |  |  |  |  |  |

|          | 1.2               | Goal   |                                             |  |  |  |  |  |  |  |  |  |  |

|          | 1.3               | Struct | ure                                         |  |  |  |  |  |  |  |  |  |  |

| <b>2</b> | State of the art  |        |                                             |  |  |  |  |  |  |  |  |  |  |

|          | 2.1               | Dynar  | nic memory models                           |  |  |  |  |  |  |  |  |  |  |

|          |                   | 2.1.1  | History                                     |  |  |  |  |  |  |  |  |  |  |

|          |                   | 2.1.2  | Memory architecture                         |  |  |  |  |  |  |  |  |  |  |

|          |                   | 2.1.3  | Memory efficiency 5                         |  |  |  |  |  |  |  |  |  |  |

|          |                   | 2.1.4  | Memory mapping                              |  |  |  |  |  |  |  |  |  |  |

|          | 2.2               | Memo   | ry controller                               |  |  |  |  |  |  |  |  |  |  |

|          | 2.3               | Real-t | ime requirements                            |  |  |  |  |  |  |  |  |  |  |

|          | 2.4               | Netwo  | rk-on-Chip architecture                     |  |  |  |  |  |  |  |  |  |  |

|          |                   | 2.4.1  |                                             |  |  |  |  |  |  |  |  |  |  |

|          |                   | 2.4.2  | Proteo NoC                                  |  |  |  |  |  |  |  |  |  |  |

|          |                   | 2.4.3  | Xpipes interconnect                         |  |  |  |  |  |  |  |  |  |  |

|          |                   | 2.4.4  | Decoupling of communication and computation |  |  |  |  |  |  |  |  |  |  |

|          |                   | 2.4.5  | Real-time guarantees                        |  |  |  |  |  |  |  |  |  |  |

|          | 2.5 Previous work |        |                                             |  |  |  |  |  |  |  |  |  |  |

| 3        | Des               | ign of | the memory controller 19                    |  |  |  |  |  |  |  |  |  |  |

|          | 3.1               | Motiva | ation                                       |  |  |  |  |  |  |  |  |  |  |

|          | 3.2               | System | n Architecture                              |  |  |  |  |  |  |  |  |  |  |

|          |                   | 3.2.1  | Request and response buffering requirements |  |  |  |  |  |  |  |  |  |  |

|          |                   | 3.2.2  | Integration into Æthereal                   |  |  |  |  |  |  |  |  |  |  |

|          | 3.3               | Requir | rements                                     |  |  |  |  |  |  |  |  |  |  |

|          |                   | 3.3.1  | Gross-to-net bandwidth translation          |  |  |  |  |  |  |  |  |  |  |

|          |                   | 3.3.2  | Requestor isolation                         |  |  |  |  |  |  |  |  |  |  |

|          |                   | 3.3.3  | Design conclusion                           |  |  |  |  |  |  |  |  |  |  |

|          | 3.4               | Chang  | ges to the Æthereal design flow             |  |  |  |  |  |  |  |  |  |  |

|          | 3.5               |        |                                             |  |  |  |  |  |  |  |  |  |  |

### CONTENTS

| <b>4</b>     | Imp                       | elementation results and test strategy | 33 |  |  |  |  |  |  |  |  |  |  |

|--------------|---------------------------|----------------------------------------|----|--|--|--|--|--|--|--|--|--|--|

|              | 4.1                       | Memory Controller architecture         | 33 |  |  |  |  |  |  |  |  |  |  |

|              |                           | 4.1.1 Scheduler requirements           | 33 |  |  |  |  |  |  |  |  |  |  |

|              |                           | 4.1.2 Core memory controller           | 34 |  |  |  |  |  |  |  |  |  |  |

|              | 4.2                       | Arbitration mechanism                  | 40 |  |  |  |  |  |  |  |  |  |  |

|              |                           | 4.2.1 Analysis of the arbitration      | 40 |  |  |  |  |  |  |  |  |  |  |

|              |                           | 4.2.2 Scheduler architecture           | 42 |  |  |  |  |  |  |  |  |  |  |

|              |                           | 4.2.3 Static-priority reordering       | 43 |  |  |  |  |  |  |  |  |  |  |

|              | 4.3                       | Worst-case latency of a memory request | 45 |  |  |  |  |  |  |  |  |  |  |

|              | 4.4                       | Design Flow                            | 45 |  |  |  |  |  |  |  |  |  |  |

|              | 4.5                       | Synthesis results                      | 48 |  |  |  |  |  |  |  |  |  |  |

|              |                           | 4.5.1 Memory Controller                | 48 |  |  |  |  |  |  |  |  |  |  |

|              |                           | 4.5.2 Scheduler $\ldots$               | 48 |  |  |  |  |  |  |  |  |  |  |

|              | 4.6                       | Test strategy                          | 52 |  |  |  |  |  |  |  |  |  |  |

|              |                           | 4.6.1 Core Memory Controller           | 52 |  |  |  |  |  |  |  |  |  |  |

|              |                           | 4.6.2 Scheduler                        | 53 |  |  |  |  |  |  |  |  |  |  |

|              | 4.7                       | Conclusion                             | 54 |  |  |  |  |  |  |  |  |  |  |

| 5            | Experiments               |                                        |    |  |  |  |  |  |  |  |  |  |  |

|              | $5.1^{-}$                 | Experiment setup                       | 56 |  |  |  |  |  |  |  |  |  |  |

|              | 5.2                       | Results                                | 57 |  |  |  |  |  |  |  |  |  |  |

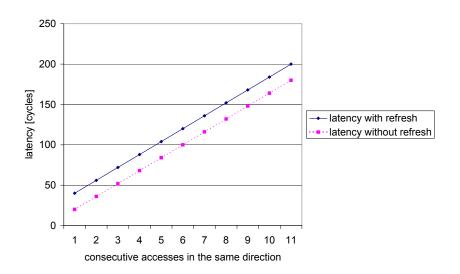

|              |                           | 5.2.1 Latency                          | 57 |  |  |  |  |  |  |  |  |  |  |

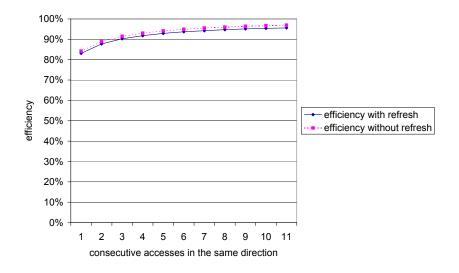

|              |                           | 5.2.2 Efficiency                       | 58 |  |  |  |  |  |  |  |  |  |  |

|              | 5.3                       | Conclusion                             | 59 |  |  |  |  |  |  |  |  |  |  |

| 6            | Final Remarks and Outline |                                        |    |  |  |  |  |  |  |  |  |  |  |

|              | 6.1                       | Conclusion                             | 61 |  |  |  |  |  |  |  |  |  |  |

|              | 6.2                       | Outline                                | 61 |  |  |  |  |  |  |  |  |  |  |

| $\mathbf{A}$ | Glos                      | ssary                                  | 63 |  |  |  |  |  |  |  |  |  |  |

|              |                           | Used acronyms                          | 63 |  |  |  |  |  |  |  |  |  |  |

| Re           | eferei                    | nces                                   | 64 |  |  |  |  |  |  |  |  |  |  |

$\mathbf{V}$

# List of Figures

| 2.1  | DRAM architecture and access cycle                                                                                                                |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | Half of the data is lost due to of poor data alignment                                                                                            |

| 2.3  | Memory map for an interleaved access                                                                                                              |

| 2.4  | Memory map for sequential access                                                                                                                  |

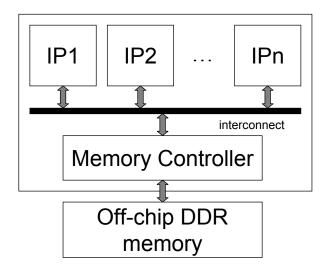

| 2.5  | Memory controller place in the system                                                                                                             |

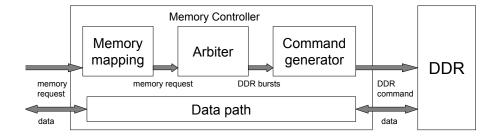

| 2.6  | Architecture of a memory controller 12                                                                                                            |

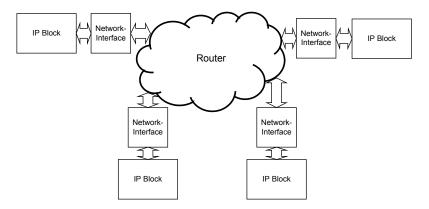

| 2.7  | Simple NoC Scheme 14                                                                                                                              |

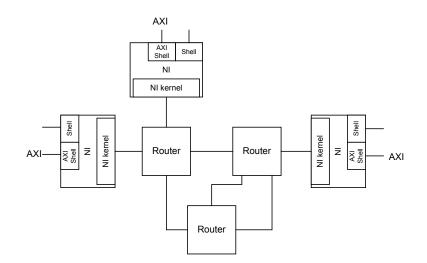

| 2.8  | $ \text{ $\pounds$thereal example } \dots $ |

| 2.9  | Production pattern of a regular producer                                                                                                          |

| 2.10 | The worst-case of an irregular producer                                                                                                           |

| 3.1  | Three requestor are connected through an interconnect                                                                                             |

| 3.2  | Modularization of the design                                                                                                                      |

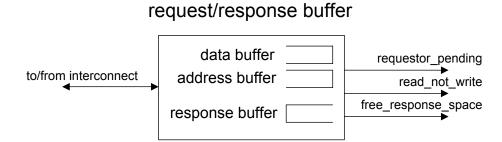

| 3.3  | Request/response buffering for every requestor                                                                                                    |

| 3.4  | Goal of the design                                                                                                                                |

| 3.5  | Modification to the kernel                                                                                                                        |

| 3.6  | NI memory controller shell                                                                                                                        |

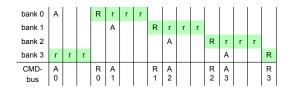

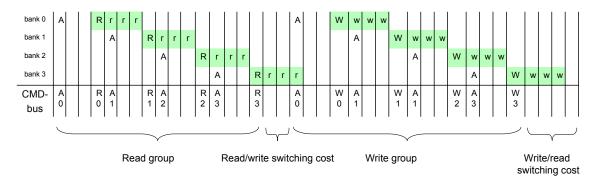

| 3.7  | Basic read group                                                                                                                                  |

| 3.8  | Basic write group                                                                                                                                 |

| 3.9  | Read/write switch overhead                                                                                                                        |

| 3.10 | Read/write efficiency                                                                                                                             |

|      | Latency                                                                                                                                           |

| 3.12 | Basic refresh group                                                                                                                               |

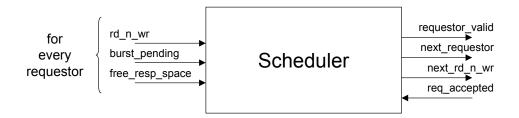

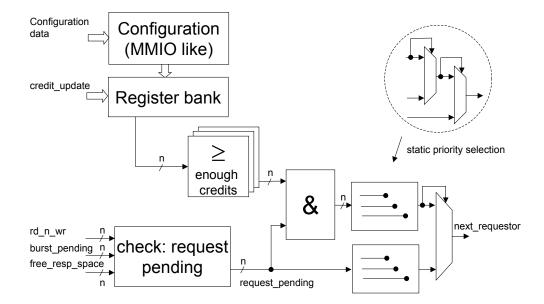

| 4.1  | Scheduler standard interface                                                                                                                      |

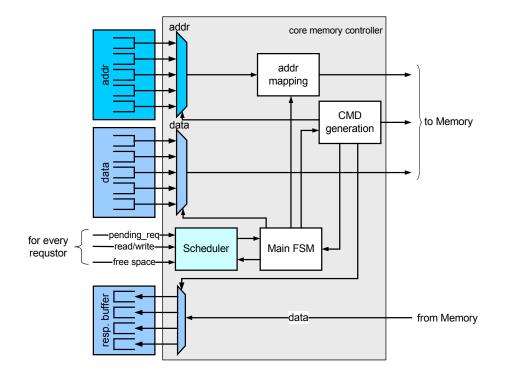

| 4.2  | Architecture core memory controller                                                                                                               |

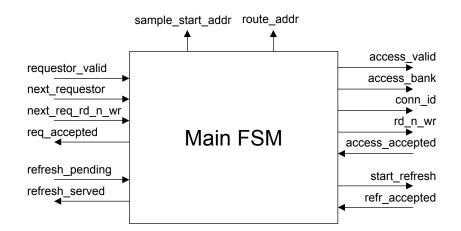

| 4.3  | Interface of the main FSM                                                                                                                         |

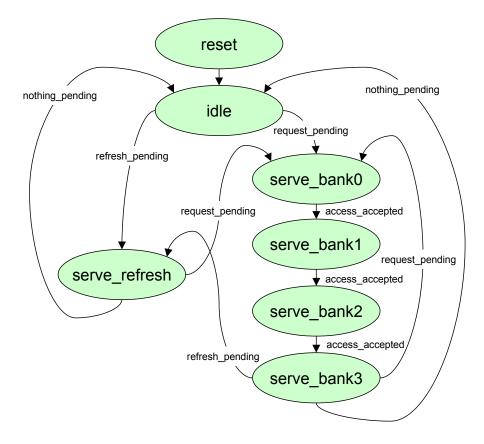

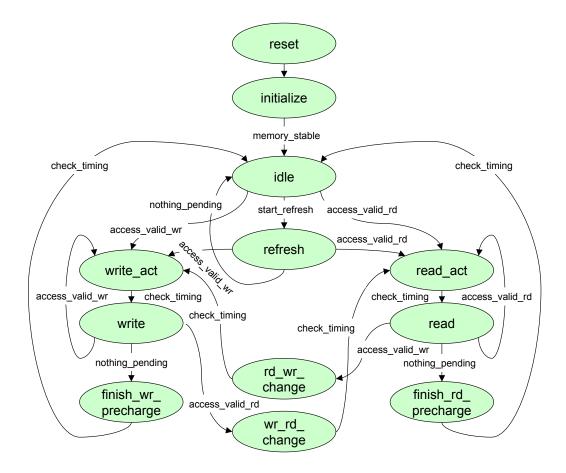

| 4.4  | State diagram of the main FSM                                                                                                                     |

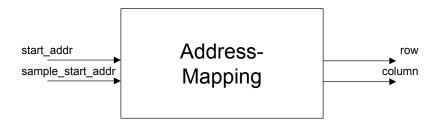

| 4.5  | Address mapping module 37                                                                                                                         |

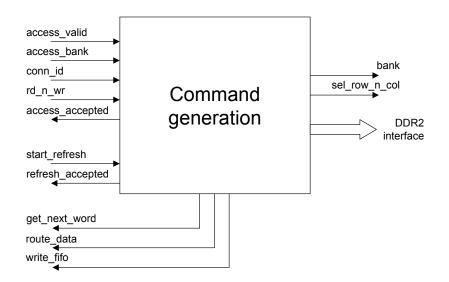

| 4.6  | Command generation module                                                                                                                         |

| 4.7  | State diagram of the command generation unit                                                                                                      |

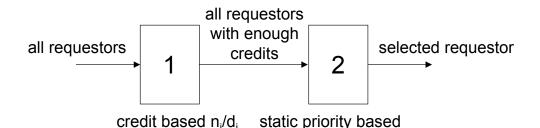

| 4.8  | Components of the arbiter                                                                                                                         |

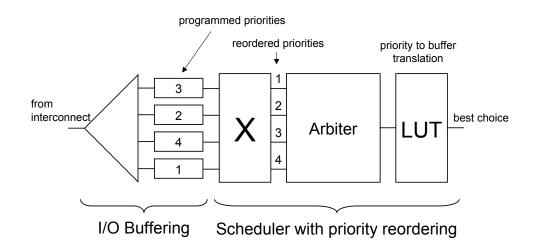

| 4.9  | Scheduler architecture                                                                                                                            |

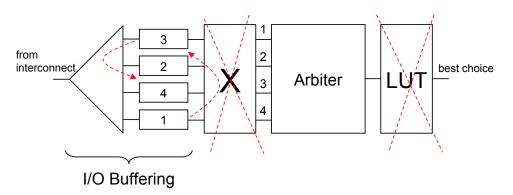

| 4.10 | Priority reordering with a switch 44                                                                                                              |

|      | Priority reordering by interchanging the buffers                                                                                                  |

| 4.12 | Timing test of the memory controller                                                                                                              |

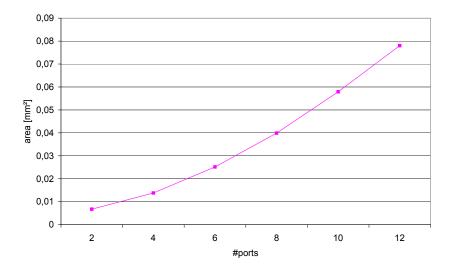

| 4.13 | Area of the scheduler with priority reordering                        | 49 |

|------|-----------------------------------------------------------------------|----|

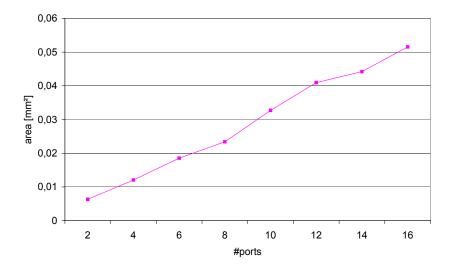

| 4.14 | Area of the scheduler without priority reordering                     | 50 |

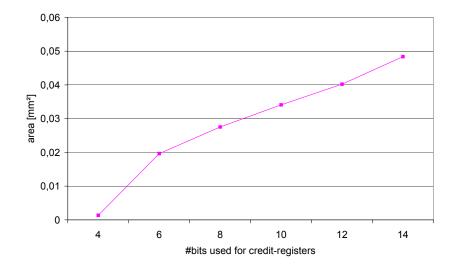

| 4.15 | Area of the scheduler in respect to the bits used in credit registers | 50 |

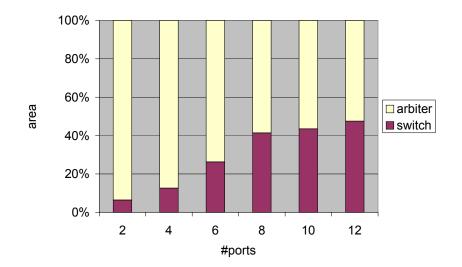

| 4.16 | Influence on the area of the scheduler from the switch                | 51 |

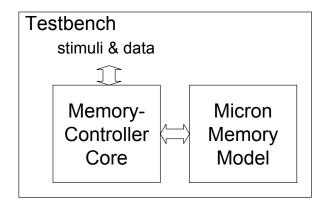

| 4.17 | Timing test of the memory controller                                  | 53 |

| 4.18 | Test strategy of the overall system                                   | 54 |

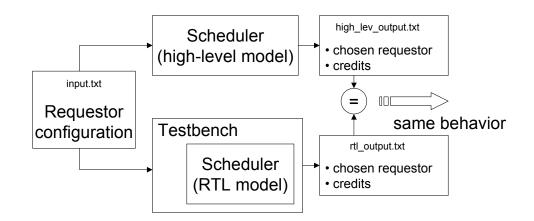

| 4.19 | The test strategy of the scheduler                                    | 55 |

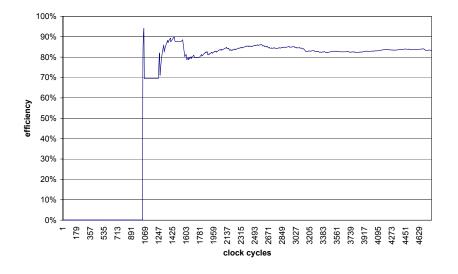

| 5.1  | Measured accumulated efficiency                                       | 59 |

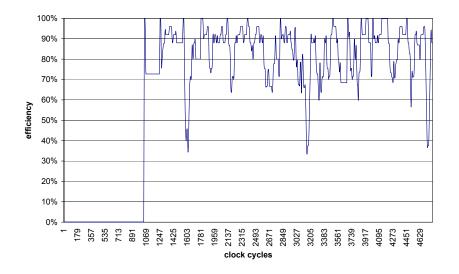

| 5.2  | Measured smoothened instantaneous efficiency                          | 60 |

# List of Tables

|     | Some SDRAM commands   |    |

|-----|-----------------------|----|

| 4.1 | Address mapping table | 38 |

|     | Use-Case definition   |    |

| 5.2 | Scheduler parameters  | 57 |

| 5.3 | Latency results       | 58 |

# Chapter 1 Introduction

This chapter gives an introduction to the research area and starts with a motivation of the topic in Section 1.1. In Section 1.2 the goal of the thesis is stated. In Section 1.3 the structure of the thesis is outlined.

## 1.1 Motivation

Systems-on-Chip (SoC) and in particular embedded real-time systems typically consist of several computational elements. These elements fulfill different tasks for processing an overall solution. Let's take a set-top box for TV sets as an example [GGRN04]. A set-top must generate a TV-signal for a particular TV channel from a digital satellite signal. This process takes different tasks. One task is to split the incoming digital signal into data streams, such as video and audio. Another task is to convert the video stream into an actual TV-signal. One more conversion has to be made to turn the audio stream into an audio signal for the TV set. Meanwhile, another task handles the user input such as changing the channel when the remote control is pressed. All these tasks have to be done in parallel and are bound by real-time deadlines. The cost of missing these deadlines is visible as black boxes on the screen or audible as noise. This is unacceptable and therefore it is necessary to always deliver this data within hard real-time deadlines.

These computational elements are either general-purpose processors or digital signal processors. Nowadays, multiple of them are integrated into a System-on-Chip solution [CS99]. A processor needs to interact with other processors, memories or I/O devices to complete a task. Currently busses are used to interconnect these IP blocks. The current research in the field suggests using Networks-on-Chip (NoC) to interconnect IP blocks, because NoCs allow more flexibility than busses [GGRN04, RGAR<sup>+</sup>03].

However, to get NoCs accepted as communication paradigm in SoCs there are still left open research questions according to [OHM05]. An example is how to deal with voluminous storage. High volume storage is usually put off-chip as dynamic memory. The separation is necessary because the manufacturing process is a different one for memories to that for standard logic. Dynamic memories provide high data rates and high storage capabilities. Nevertheless, dynamic memories lack flexibility in accessing random memory locations efficiently and require refresh cycles to keep the content. Allowing efficient communication between IP blocks and a shared memory requires a memory controller. IP blocks, which communicate with the memory, are named hereinafter requestors. The memory controller arbitrates between the requestors and manages the memory accesses. The goal of this thesis is to design a memory controller to provide hard real-time guarantees, and provides an efficient communication between IP blocks and the memory. The memory controller should also be easily/efficiently combined with the interconnection.

# 1.2 Goal

The goal of this thesis is to provide a memory controller for real-time systems, which can be used with  $\pounds$ thereal [GDG<sup>+</sup>05].  $\pounds$ thereal is a NoC proposed by Philips Research. The memory controller is co-designed with the network infrastructure of  $\pounds$ thereal. The design of the memory controller and  $\pounds$ thereal focus on predictable performance. To keep the overall system predictable the memory controller has to be predictable as well. Identifying the key elements of  $\pounds$ thereal leads to distinct goals, which are required for a memory controller suitable for real-time systems. The identified requirements for the memory controller are:

- predictable

- gross-to-net bandwidth translation

- efficient resource utilization

- requestor isolation

Predictability means that the memory controller can be analyzed analytically and worst case scenarios can be calculated at design time. A gross-to-net bandwidth translation allows to calculate from the peak memory bandwidth (gross bandwidth) the net bandwidth, which is the effective available bandwidth for the requestors. Efficient resource utilization is another goal for this memory controller, allowing an economical use of the resources of the system. The requestor isolation allows that every requestor can be analyzed individual without considering the traffic patterns of the other requestors in the system. The memory controller is designed in a way so it can be used in any system where a predictable memory controller is required.

## 1.3 Structure

The thesis is organized as follows: In Chapter 2 the related work is discussed. In Chapter 3 the design process of the memory controller is described and the design of the memory controller is proposed. Chapter 4 describes the implementation and the verification process. Furthermore, synthesis results are presented. Chapter 5 shows the simulated performance of the memory controller with a Philips Mid-End multimedia SoC use-case. Chapter 6 concludes the thesis with a summary and questions for further research work.

# Chapter 2

# State of the art

This chapter summarizes the current technologies and architectures proposed in the field, which are related to the topic of the thesis. It starts with an introduction on dynamic memories in Section 2.1. In the following Section 2.2 the concept of memory controllers is discussed and it is illustrated with a memory controller proposed by others. The real-time requirements are discussed in Section 2.3. Networks-on-Chip architectures are discussed in Section 2.4, where the focus is on Æthereal. Section 2.5 discusses the related work.

# 2.1 Dynamic memory models

This section gives an overview of dynamic memories. Starting from the history and background of memories in Section 2.1.1 the architecture is discussed in Section 2.1.2. Memory efficiency is discussed in Section 2.1.3 and the memory mapping is discussed in Section 2.1.4.

#### 2.1.1 History

Storage plays an important role in virtually any computer system and in system development. Since 1975 DRAMs are used in computer systems as the main memory [HP03]. Robert Dennard invented the concept of DRAMs in 1968. The first letter stands for dynamic, and was introduced to allow reducing the number of transistors per stored bit. One transistor is used per bit, and the information is stored as charge in a capacitor. The capacitor is part of the transistor. Reading from a memory cell can disturb the information in the transistor, therefore it is necessary to precharge a memory cell after accessing it. However, not only accessing a memory cell disturbs the information. The self-discharge of the capacitor also disturbs the information. Therefore, a regular refresh must be invoked to recharge the memory cells [HP03].

The advantage of DRAMs compared to static RAMs (SRAMs) is that DRAM memory cells are smaller in size and hence allow a higher integration capacity per area unit. SRAMs use a bistable Flip-Flop to store information. A SRAM bit cell requires 6 transistors. The advantage of SRAMs is that they are faster and do not require a recharge mechanism. Furthermore, SRAMs have lower power consumption. It is possible to put a SRAM into an effective low-power mode or standby mode. SRAMs find their application on high levels of the memory hierarchy in areas where fast memories are required, such as in caches or in scratchpads. The application of DRAMs is where more storage is required, but the latency is not so critical compared to the application domain of SRAMs [HP03].

#### 2.1.2 Memory architecture

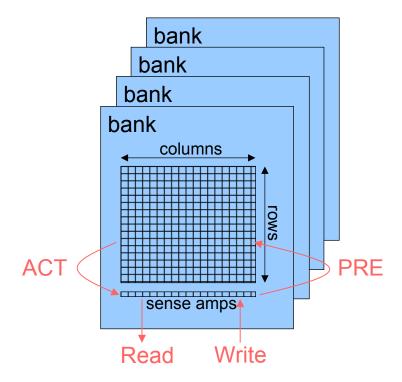

The architecture of DRAMs allows packing more storage into the memory than with the architecture of SRAMs. This causes that the width of the address lines to grow in size too. With the concern of costly pin count in mind, the address is separated into column and row information and is multiplexed onto the address bus of the memory. The architecture of an SDRAM (Synchronous DRAM) is three dimensional (bank, row, and column) and is illustrated in Figure 2.1.

Figure 2.1: DRAM architecture and access cycle

Double Data Rate SDRAM (DDR) memories are DRAM memories introduced as high bandwidth memories. DDR memories transfer data at both clock edges. The DDR standard is an open standard and defined by the Joint Electron Device Engineering Council (JEDEC). The DRAM memory is specified in [Ass04].

The row address is sent first to access a memory cell, called the row access strobe (RAS). The information of the cells is fetched into an intermediate buffer, the sense amplifiers. With providing the column address and the information of the type of the access (read or write), the correct columns in the sense amplifiers are selected. For a read access a data burst is sent to the output. The memory location is now ready to be precharged with the unmodified content of the sense amplifiers. This mechanism is required since reading the memory cells results in changing the content of the memory cells. For a write access a data burst is fetched from the data input and is stored at the selected column

position of the sense amplifiers. The memory cells are updated with a precharge with the current information from the sense amplifiers [HP03, Ass04].

The access pattern of DRAMs follows the below stated and simplified principle<sup>1</sup>, and is shown in Figure 2.1:

- 1. Activate a row (ACT)

- 2. Read or write to a column within the row (RD/WR)

- 3. Precharge the row (PRE)

A memory controller translates the accesses from the requestors into commands understood by the memory. Table 2.1 lists the most frequently used commands.

| Command | Description           | Opcode |

|---------|-----------------------|--------|

| NOP     | do nothing            | none   |

| ACT     | Activate              | row    |

| RD      | Read                  | column |

| WR      | Write                 | column |

| PRE     | Precharge current row | row    |

| REF     | Refresh               | none   |

Table 2.1: Some SDRAM commands

To access the memory the timing parameters of the memory have to be considered. See Table 2.2 for a selected choice of timing parameters taken from the DDR2 specification in [Ass04]. After activating a row, the time  $t_{RCD}$  has to be elapsed to continue with a read or write access. To precharge a row again the time  $t_{RAS}$  after the activate command has to be elapsed to invoke a precharge command. For the analysis of the memory efficiency in the next Section 2.1.3 the timing parameters are considered in more detail.

The time  $t_{RC}$  is the minimum time which has to elapse until an activate command is allowed to follow a previous activate command to the *same* bank. Whereas the time  $t_{RRD}$ is the minimum time which has to elapse until an activate command is allowed to follow a previous activate command to a *different* bank. The time  $t_{RCD}$  has to elapse after an activate command until a read or write command can be invoked to the same bank. The time  $t_{WTR}$  is the required time on the data bus for switching the directions from write to read.

#### 2.1.3 Memory efficiency

Designing embedded systems requires being economical with the use of integrated components. Embedded systems have the requirement to be small in area size and should have a low energy consumption to allow extended operation time on battery power. However, when using dynamic memories, 100% efficiency cannot be reached due to protocol limitations. Dynamic memories have the advantage to provide more storage at a lower cost but also have the drawback that the memory content needs to be refreshed regularly. During

<sup>&</sup>lt;sup>1</sup>It is possible to access another column in the same open row, without the necessity of precharging and activating the same row first.

| Parameter  | Min. time | Min. time | Description                              |

|------------|-----------|-----------|------------------------------------------|

|            | [ns]      | [cycles]  |                                          |

| $t_{CK}$   | 5         | 1         | Clock cycle time                         |

| $t_{RAS}$  | 45        | 9         | Active to precharge command delay        |

| $t_{RC}$   | 60        | 12        | Activate to activate command delay       |

|            |           |           | (same bank)                              |

| $t_{RRD}$  | 7.5       | 2         | Activate to activate command delay       |

|            |           |           | (different bank)                         |

| $t_{RCD}$  | 15        | 3         | Activate to read/write delay             |

| $t_{RFC}$  | 75        | 15        | Refresh to activate command delay        |

| $t_{RP}$   | 15        | 3         | Precharge to activate command delay      |

| $t_{REFI}$ | 7800      | 1560      | Average refresh to refresh command delay |

| CL         | 15        | 3         | Column-access-strobe (CAS) latency       |

| $t_{WTR}$  | 10        | 2         | Write-to-read turn-around time           |

| $t_{WR}$   | 15        | 3         | Write recovery time                      |

Table 2.2: Selected timing parameters for DDR2-400 256 Mb device CL=3

the refresh cycle no data can be transferred to or from the memory. Therefore, those cycles are lost. Regular refreshes are not the only cause why dynamic memories cannot reach 100% efficiency. Equation (2.1) gives a general definition for measuring efficiency in a system with a dynamic memory [Wol05, HP03].

$$efficiency = \frac{data\_cycles}{total\_cycles} = \frac{total\_cycles - lost\_cycles}{total\_cycles}$$

(2.1)

The following paragraphs will discuss other sources of efficiency losses. The following losses are referenced in literature as most important [Wol05, HP03]:

- refresh efficiency

- data efficiency

- bank conflict efficiency

- read/write efficiency

- command conflict efficiency

Keeping the efficiency high overcomes the necessity of introducing faster and wider memories. Introducing faster and wider memories cause the system to be more expensive and to consume more energy.

#### **Refresh efficiency**

To retain the content of a dynamic memory, it is necessary for the memory content to be refreshed regularly. During the time when the memory is being refreshed, no data can be transferred to and from the memory. This causes a loss of data transfer cycles, and has negative affects on the efficiency. For DDR2 devices, it is necessary to refresh the memory once every  $t_{REFI}$ , 7.8µs according to Table 2.2. The maximum amount of lost cycles occurs when all banks have to be precharged before the refresh takes place. The refresh efficiency is traffic independent. The specification of the DDR2 memory allows the postponing of refresh cycles up to  $9^*t_{REFI}$ . However, after this interval, 8 refresh commands have to be sent consecutively. The refresh efficiency is calculated as shown in Equation (2.2), where N is the number of consecutive refreshes.

$$refresh\_efficiency = 1 - \frac{1}{t_{REFI} * N} \left( t_{RFC} * N + t_{PrechargeAll} \right)$$

(2.2)

$t_{PrechargeAll}$  is the sum of  $t_{RAS}$  and  $t_{RP}$ . Calculating the *refresh\_efficiency* for N = 1 and using the timing parameters specified in Table 2.2 results in the following efficiency:

$$refresh_{efficiency} = 1 - \frac{1}{1560 * 1} (15 * 1 + 9 + 3) = 98.27\%$$

The efficiency loss for the refresh cycle is 1.73% and can be lowered when invoking more refresh commands in a consecutive sequence. The reason is that all banks are precharged in a single go, and so the efficiency is improved [Wol05, Å05, Ass04].

#### **Data efficiency**

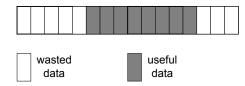

Data is retrieved from the memory in bursts. The bursts cannot start at any arbitrary address. If the required data is contained in the middle of a burst then the remaining data is transmitted without any purpose. See Figure 2.2 for an illustration.

Figure 2.2: Half of the data is lost due to poor data alignment

Data efficiency depends on the burst size. The efficiency is higher for a smaller burst size. Nevertheless, allowed choices of burst sizes depend on the memory type used. The memory controller cannot influence the data alignment nor do the memory controllers usually solve it. It is considered a software problem because software is more susceptible to influence the efficiency of data alignment [Wol05,  $\dot{A}05$ ].

#### Bank conflict efficiency

A bank conflict happens, when a row in a bank is open and the next access targets another row in the same bank. The contents of the open row are still in the sense amplifiers and therefore the current row has to be precharged. After invoking the precharge command, the time  $t_{PrechargeToACT}$  has to elapse until another row in the same bank can be activated. This delay causes a loss of cycles and results in a lowered efficiency. The bank conflict problem can be overcome by reordering the bursts or requests. The goal is to delay the access to the same bank and schedule other non-conflicting bursts in the mean time. This solution leads to an increase in efficiency. However, the latency increases when reordering is considered and has to be factored in the design specification.

Furthermore, when reordering read/write accesses, read/write hazards have to be considered. Read/write hazards occur when a later arriving write access is scheduled earlier than a previously arriving read access to the same address. In the case of reordering, the read access will get modified data back, instead of the old data as expected. It is possible to track read/write hazards by analyzing the addresses of the accesses. When two accesses are identified as possible read/write hazards, the system does not allow reordering of these two bursts. This mechanism comes at the expense of additional logic. Nevertheless, it allows free reordering of the bursts and requests to increase efficiency. However, data reordering comes with the additional expense of buffering allowing reordering the requests [Wol05, Ass04].

#### Read/Write change efficiency

The memory controller is communicating with the memory for transmitting read and writes data over a bidirectional data bus. When a read access is followed by a write access additional time is needed to change the direction of the bus. The same is necessary in the reverse scenario when there is a switch from write to read. However, during the idle state, no data is transferred over the bus and this affects the efficiency of the memory access. The idle cycles needed to switch from read to write is defined as *read\_to\_write\_cost* and can be calculated according to the DDR2 protocol specification [Ass04] with Equation (2.5).

$$RL = CL \tag{2.3}$$

$$WL = CL - 1 \tag{2.4}$$

$$read\_to\_write\_cost = 2 + WL - RL =$$

$$= 2 + CL - 1 - CL =$$

$$= 1$$

(2.5)

The cost of switching from read to write is static and is one clock cycle. Switching from write to read is defined as *write\_to\_read\_cost* and is stated in Equation (2.6).

$$write\_to\_read\_cost = CL - 1 + t_{WTR} + RL - WL =$$

=  $CL - 1 + t_{WTR} + RL - (RL - 1) =$  (2.6)

=  $CL + t_{WTR}$

The cost for switching from write to read depends on the timing parameters of the memory. According to the timing parameters specified in Table 2.2 the costs are 5 clock cycles. The read/write change efficiency is traffic-dependent. Woltjer [Wol05] analyzed the read/write change efficiency for CPU traffic containing 30% write accesses and 70% write accesses and a block size of 32 words, and got an efficiency of 93.8%. Improving this efficiency is possible by favoring read after read and write after write sequences and reducing read/write switches. However, the efficiency gain comes with the cost of higher latency and additional buffering [HdCLE03, ARM04].

#### Command conflict efficiency

DDR allows transferring one data word per clock edge to or from the memory so that two data words are transfered per clock cycle. Nevertheless, sending commands from the memory controller to the memory is only possible once every clock cycle. An access to a memory destination usually consists of three commands: Activate, read/write, and precharge. This leads to the possibility of command-bus contention. For a burst size of 4 words a read or write command has to be placed on the bus every second clock cycle. Thus every other clock cycle is available for an activate and precharge command. The utilization of the command bus by read or write commands is then 50% and the remaining 50% are left for activate and precharge commands. For longer bursts such as 8 words a read or write command has to be invoked every 4 clock cycles. This causes the command bus to be utilized for 25% and the remaining 75% can be used for activate and precharge commands. For a burst size of only 2 words a read or write command has to be issued every clock cycle and this leaves no space for additional commands. However, additional commands are required to access the content of the memory. This results in a reduced efficiency since data cannot be provided at every clock. This loss in efficiency is called the command conflict efficiency.

The command conflict efficiency can be improved by using bigger burst sizes. Using a bigger burst size also affects the bank conflicts and increases the bank conflict efficiency. Another possibility of improving the command conflict efficiency is to use read and write commands with auto precharge. This means that rows are automatically precharged after they are accessed. Furthermore, the DDR2 protocol introduced an additive latency (AL) for read and write commands. This leads to more flexibility for sending read and write commands over the command bus.

The use of autoprecharge is appropriate when having accesses, which address different rows in the same bank. The advantage with autoprecharge is that only two commands have to be invoked for an access. First activate and then read or write with autoprecharge. However, using autoprecharge is inappropriate when accessing a different address in the same row and bank. In this case, the row can be left open and accessed immediately. Advanages of open and closed page policies are investigated by [RDK<sup>+</sup>00]. Additional logic is required to track the dependencies when accessing the same row.

A different approach improving the command conflict efficiency is to influence the order of the commands. Consider the case when a command sequence consists of ACT, RD/WR, and PRE. Consider the following situation, to complete an access to an open bank a precharge is missing, but another access to another bank is waiting. In this case, one of the two commands has to be stalled. Either the read/write or the precharge command can be delayed. Stalling the read/write command results in immediate loss of data cycles and reduces efficiency. Stalling the precharge will stall future accesses to the same bank by one clock cycle because the precharge will finish later. In the DDR2 protocol additive latency is introduced to overcome this problem. This allows sending read/write commands immediately after an activate command. The read/writes are delayed internally to assure the required timing behavior. This solution does not add any additional space on the command bus, but it introduces some flexibility in the timing of sending memory access commands.

The command conflict efficiency is hard to analyze and needs to be estimated for every

application independently. Nevertheless, Woltjer [Wol05] is estimating the loss around 0 - 5%.

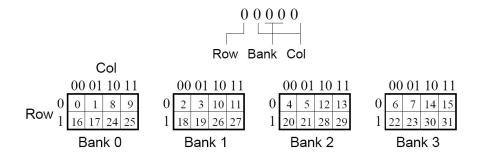

### 2.1.4 Memory mapping

A memory map is consulted to translate the logic address into a physical address. The physical address of a DDR memory consists of the information: bank, row, and column. Multiple banks are introduced to allow higher bandwidth. However, higher bandwidth is reached with an interleaving memory access pattern to hide activate and precharge times. Figure 2.3 shows an illustration of an interleaved memory map. In this example only five bits are used to keep it simple. The most significant bit determines which row to access. In the example a full burst consists of eight words, which means that the eight words have to be spread over all banks. A way to do that is to access consecutive two words in the same bank, switch the bank and access again two consecutive words, and so on. To get an access pattern as described above two consecutive words are mapped into one bank. This can be gained by taken the least significant bit and the bit right to most significant bit and arrange them together as column address. The bank bits are chosen analogously, to get an interleaved access pattern, where an eight word accesses targets 4 banks. The drawback of this memory map is that a minimum burst size is required to hide activate and precharge time, but leads to a 100% bank access efficiency [HP03, Å05].

Figure 2.3: Memory map for an interleaved access [A05]

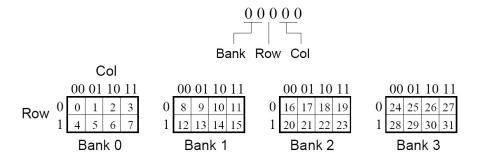

Another way of partitioning and mapping the memory is to make separate address spaces for the accesses. Which means that every access targets only a bank. See Figure 2.4. The two most significant bits determine, which bank to access. The other bits translates the logical address into row and column information [HP03, Å05].

The memory map is a powerful tool for a system architect, which allows specifying how the requestors access the banks. Section 3.3.2 will discuss the impact on the system architecture level further.

### 2.2 Memory controller

This chapter briefly summarizes the architectures of memory controllers designed by others. It starts off with an introduction of the place of a memory controller in the system. After it discusses the different architectures of memory controllers.

Figure 2.4: Memory map for sequential access [A05]

A memory controller translates the accesses from the requestors into commands understood by the memory. The memory controller is placed in a SoC, where the IP blocks are interconnected with each other and further to a memory controller. The memory controller is then connected to an off-chip dynamic memory [Wol05, RDK<sup>+</sup>00, Web01]. See Figure 2.5 for an illustration.

Figure 2.5: Memory controller place in the system

A memory controller is considered to consist of the following elements: memory mapping unit, the arbiter, the command generation unit, and the data path (see Figure 2.6 for an illustration). The memory mapping unit translates the logical addresses to a physical address of the DDR memory. The arbitration unit picks the requests according to the scheduling strategy. To translate the accesses from the requestors to DDR bursts, the command generation provides corresponding commands to access the DDR memory. The data is transported on the data path to and from the memory [Wol05, ARM04, Web01].

In the introduction it is motivated that current computer systems require fast access to high volume storage with high throughput. Therefore, memory controllers are required which provide a high bandwidth and low latency access to the off-chip memory. Different types of memory controllers are proposed, which make attempts to fulfill these constraints.

Figure 2.6: Architecture of a memory controller

An exponent of memory controllers is the PrimeCell<sup>TM</sup>Dynamic Memory Controller proposed by ARM. The controller is designed to be connected to the IP blocks via an ARM bus, like AMBA or AXI. The arbitration between multiple requestors is carried out with an round-robin arbitration mechanism. Read accesses are provided with a quality-of-service (QoS) mechanism which allows providing low latency. Therefore, an adapted round robin mechanism is used. Higher priority is given to these requestors thus allowing lower latency. This mechanism is not provided for write accesses. However, there are no hard bounds provided in the case of a read request either [ARM04].

The aforementioned memory controller is a general purpose memory controller and is not optimized for a special application, unlike the memory controller proposed by Rixner et al. in  $[RDK^+00]$ . This memory controller provides high efficiency due to pipelined accesses with an interleaved access pattern. To get interleaving access pattern, the scheduler reorders the requests and reorders accesses within requests  $[RDK^+00]$ . However, requestor isolation cannot be guaranteed due to the dependencies caused by reordering of the accesses.

Lee et. al. [LLJ05], proposes a memory controller with a layered architecture and a quality-aware scheduler. The functional layers are used to achieve high DRAM utilization. Layer 0 is considered as memory interface socket, which is stated to allow a quick integration into an arbitrary system. The quality aware arbitration is integrated in Layer 1. The goal of the memory controller is to provide high memory efficiency [LLJ05]. The two aforementioned memory controllers of [RDK<sup>+</sup>00] and [LLJ05] both allow providing soft-real-time guarantees. However, both lack providing hard-real-time guarantees.

Weber is proposing in [Web01] a memory controller which is connected to a network and which allows providing quality-of-service. The memory controller proposes to provide high bandwidth combined with low latency. The high bandwidth is reached with reordering the traffic to get an interleaved access pattern. The arbitration is done with a 6-stage filter, where the request is picked, which causes the lowest cost. The cost is measured with the loss of efficiency combined with the quality-of-service level [Web01].

The memory controller described by Heithecker in [HdCLE03] is similar to the memory controller suggested by Weber. However, the memory controller from Heithecker is not used with a network and proposes a lower latency than the memory controller of Weber. The lower latency is reached due to a 2-stage arbitration mechanism instead of a 6-stage arbitration filter. The memory controller is optimized application specific for high-end image processing. Due to the expected reduced application space it is implemented in an FPGA [HdCLE03].

## 2.3 Real-time requirements

This section describes briefly the requirements of real-time systems and their applications. Starting with the definition taken from [Lap93] where a real-time system is considered as:

A real-time system is a system that must satisfy explicit (bounded) responsetime constraints or risk severe consequences, including failure.

With other words the key element of a real-time system is to react on events (possible external) within a certain deadline otherwise the system could break thus risking severe consequences. Severe consequences could be harmful for example when a nuclear power plant is overheating or a car with digital speed control stops accepting break signals when driving 150 km/h on the motorway. However, not all consequences have to be as bad as described above. As stated in Section 1.1 with the set-top box example, the missing of deadlines could results in black boxes on the screen and does not harm people. However, this is not acceptable either. Therefore, real-time systems require to react within a certain time frame and thus providing a maximum response latency. Providing a maximum response latency at every possible situation leads to a system, which is predictable at every moment in time [Lap93].

However, there are also other requirements for real-time system as identified above. These scenarios have in common that they are all fault critical, with different consequences. To design a system, which is fault tolerant it is necessary to test the system exhaustively or to make a formal verification of the system to assure the functionality. Therefore, it is necessary to design and maintain tests, which cover critical test cases [Lap93].

Other requirements of real-time applications are, according to [Lap93], concerned to the budget of a project. This means that a selected solution should contain a hardware/software mix, so that the system is cheap to build. This includes that a decision has to be made if the system should consist of general-purpose components or should be specific for this particular problem set.

# 2.4 Network-on-Chip architecture

The current process technology allows the integration of complex SoCs with many IP blocks. To catch up with Moore's law, it is mandatory to integrate more IPs into a single die. This allows to have a shorter design cycle by reusing IP blocks and the design process becomes more economical [SSM<sup>+</sup>01, BM02]. Currently buses or switches are used to interconnect IP blocks. As investigated in [BM02, SSM<sup>+</sup>01, GDR05] current buses do not scale anymore with the current integration speed of SoCs. The current research in the field suggests using Networks-on-Chip (NoC) to interconnect IP blocks, because NoCs allow more flexibility than buses [GGRN04, RGAR<sup>+</sup>03].

A key idea of NoCs is to decouple computation from communication. An example of a SoC is that a processor performs a task by computing tokens, which are passed on to an other processor. This processor takes the token, performs a computation and passes the token further. However, passing on the tokens causes stalling of the sending processor if the bus arbiter does not allow the sending processor immediately access to the bus. Then the sending processor has to wait until the arbiter grants the processor access to the bus. This behavior denotes that the processor cannot continue its usual work, and stalls. To overcome this problem a separation between calculation and communication is performed. A processor adds the information where it belongs to the token and passes it over to a communication unit. This communication unit passes the token further on to the receiver. This communication architecture is called a Network-on-Chip, and the communication unit a network interface (NI). The NI is directly connected to an IP block, preferably with standard bus protocols (like AXI, AHB, OCP) maintaining the compatibility with existing IP blocks. The IP blocks themselves take care of the computation of tasks and forward the token to a buffer in the NI. The NI distributes the data to the targets. This approach leads to a communication based design, where communication is considered as important as computation [SSM+01, RGAR+03].

The current research proposes the Network-on-Chip concept to overcome the mentioned problems of traditional bus interconnect, which is lacking flexibility and scalability [DRGR03]. Figure 2.7 shows the principle of an on-chip network.

Figure 2.7: Principle of a network on a chip

Network-on-Chip research has much in common with the research carried out on computer networks. One of the differences is the use of relatively shorter wires. This guarantees short time delay between the components and further allows tight synchronization between them. On the other hand, new problems arise such as the limited amount of buffering on a chip, which is expensive in terms of chip area [RGAR<sup>+</sup>03, SLKH02].

#### 2.4.1 Æthereal

Æthereal is a Network-on-Chip concept proposed by Philips Research Laboratories [DRGR03, GDG<sup>+</sup>05, GDR05, GRG<sup>+</sup>05]. The aim is to provide a scalable interconnect with communication guarantees between the IP blocks, and to allow connecting IP blocks with standard interfaces (like AXI) to the network. The provided communication guarantees are guaranteed throughput (GT) and best effort (BE). The GT traffic class is used to provide hard-real-time guarantees in the system.

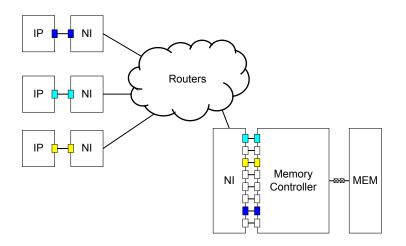

The data passes through the network in packets. Every IP core is connected to a network interface, which in turn is connected to a router. For transmission of data, the IP block offers transactions to the NI. The NI packetizes the transaction and passes the packets to the router where it is transported to the target NI. There, the packet is stripped and the frame is passed on to the target IP block via a standard bus interface. Figure 2.8 shows the connection scheme and the network interfaces from the Æthereal network. The NI contains two modules, the kernel and the shell. The kernel implements the network behavior, passing the packets to the router. The shell translates the incoming and outgoing packets to standard protocols, e.g. AXI. By changing the shell, IP blocks with other interfaces are connected to the Æthereal network.

Figure 2.8: Æthereal network example

The network uses time-division-multiplexed circuit switching to route packets through the network. Source routing is applied to direct the packets. Furthermore, the packets are routed contention free. Every packet is chopped into small tokens, called flits. These flits are placed into pre-allocated slots, which belong to a particular traffic class and connection. The allocation of the slots is calculated off-line, when the network is set-up. The slot allocation algorithm calculates a global slot table, based on the information about the traffic class and the required bandwidth [RGAR+03, RDGP+05, DRGR03].

#### 2.4.2 Proteo NoC

Proteo NoC is a Network-on-Chip concept proposed by the Tampere University of Technology [SSTN02]. This NoC has a packet switched communication network and is constructed with parameterized and reusable hardware blocks. The different functionalities in the NoC are organized according the ISO-OSI 7 layer model. IP blocks are connected to nodes, which are further connected to nodes or IP blocks. The nodes wrap the data from the IP blocks and forward them to the destination. There the packet is unwrapped and forwarded to the destination IP block. In case of a read request a request is sent to the destination IP block, which returns a response. In case of a write request the destination IP block acknowledges the received packet. However, in case of a malfunction (a packet lost in the NoC) the NoC detects the lost packet and re-transmittes the packet automatically [SSTN02].

The nodes are connected to other nodes or to IP blocks. In the case of two connected nodes an interconnection model is used for transmitting and receiving packets. The communication between IP blocks is organized as point-to-point connection. A VHDL based design flow is used to derive the Proteo NoC for different use cases [SSTN02].

#### 2.4.3 Xpipes interconnect

Xpipes is a NoC architecture proposes by the University of Bologna [BB04]. The NoC is designed as packet switched NoC, which targets Multi-GHz communication. The functional units of the NoC are designed as highly parameterized network components in synthesizable SystemC, which are re-used for different applications. The application definition is translated into a application specific NoC definition. With this NoC definition the XpipesCompiler instantiates the network components accordingly and generates routing tables for the routing of the packet. The packets are routed with a static routing algorithm, called a street sign routine. As a result an interconnect is generated in synthesizable SystemC [BB04].

The NoC contains an error correction with packet retransmission. The errors are detected either with a Hamming code or a Cyclic Redundancy Check (CRC). The packets are sent from a transmitter to a receiver. The transmitter adds to the packets the CRC code. The receiver checks the CRC code and acknowledges the packet if received correctly. If the CRC code does not fit to the packet then a NACK (not acknowledge) is returned to the transmitter. Hence the transmitter starts to resend packets beginning from the first detected packet with an error. However, after the error was detected the receiver throws all received correctly). This mechanism allows saving buffering for reordering out-of-order packets, but increases the latency due to the unnecessary retransmission [BB04].

#### 2.4.4 Decoupling of communication and computation

In a typical SoC, IP blocks are interconnected, and share a common external memory. The SoC performs operations on an input stream and delivers the result as an output stream. To perform an operation, the IPs has to know what to do, which means the IP blocks need instructions to run a program. The program code is fetched from an external memory or is located in a ROM. The data needed by the IP blocks is fetched from the memory or directly from other IP blocks. In this example, every IP block is accessing the memory. With the growing number of IP blocks, IPs only get a limited amount of accesses to the memory, and the memory becomes the bottleneck of the system. According to [HP03], this behavior is not only valid in this example system, it is shown that in most systems the memory becomes the bottle-neck. Having limited access to the memory means that the IP stalls when trying to fetch data from the memory, while an other IP block is already accessing the memory. A typical solution to overcome this problem is to introduce a small cache memory next to the IP. The cache keeps recently used data and instructions stored. If the IP block accesses a recently used memory location again, then it does not need to fetch the data or the instruction from the external memory, but instead the data is handed over by the cache, known as a cache hit. This makes the access to the memory faster and reduces the amount of transfers to the memory. According to [HP03], the reason this mechanism works so well is the following. The shape of the accesses follows the principle of locality, stated as rule of thumb, programs spend 90% of their execution times in 10%of the code [HP03].

However, the advent of cashes in the system not only reduces the amount of memory accesses, but it also hides the different operational speeds of the IPs with respect to the memory. The problem with external memories is that they are big in size but slow in terms of access time. A cache is faster because it runs at the same speed as the processors do, but limited in size due the chip area. This means that if there is an access to a new memory location, also known as a cache miss, then the cache fetches the requested data from an external memory and hands it over to the processor. If a cache miss occurs, the access is not faster than compared to a system without cache but applying the principle of locality leads to the conclusion that caches improve the average case [HP03].

Packet switched networks, like the Æthereal NoC, allow a clear decoupling of communication and computation. However, in order to have NoCs accepted in the SoC design process, a major concern is the aspect of buffering. The reason of the high costs of buffers is that it is expensive in terms of chip area. These buffers are needed to properly decouple computation from communication between interacting IPs and between the IPs and the network infrastructure. These buffers are integrated into the NI. The producer places data into the buffers of the NI. The network forwards the data in flits to the NI of the consumer, where it is stored and further forwarded to the consumer. If the buffers in the NI are too small, it causes the processor to stall and the processor cannot resume computing, which is not the intention of the decoupling buffers. Therefore, buffers have to be sufficient in size, but should not be over dimensioned and a waste of area.

In upcoming GALS SoC design, the IP blocks use different clock frequencies [GRG<sup>+</sup>05, SSTN02, MVF02]. Æthereal for example is equipped to handle different clock frequencies of the IP blocks and makes it possible to run the network on a faster speed to handle more data traffic. The required synchronization between the IP blocks and the network is carried out in the buffers of the NI [GRG<sup>+</sup>05].

#### 2.4.5 Real-time guarantees

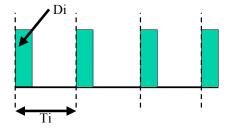

Introducing guaranteed services like GT and BE into a NoC provides real-time guarantees in a SoC. A naive way of calculating the buffer size is analyzing the traffic patterns of the producer. Assuming a periodic producer, the producer is allowed to send a guaranteed payload in a given period, see Figure 2.9 for an illustration, where Ti is the period and Di is the burst-size. The worst-case occurs if two packets are sent consecutively, which happens if the producer sends the data right before the end of the first period and then sends data again at the begin of the next period. This means that it is necessary to be able to buffer twice the guaranteed payload size. Figure 2.10 illustrates this worst-case behavior. However, knowing the arrival pattern and behavior of the system allows to optimize the buffering in the NI [GRG<sup>+</sup>05]. In [GRG<sup>+</sup>05], an algorithm for this optimization is given optimizing the buffer space and providing a full decoupling of computation and communication.

## 2.5 Previous work

Section 2.2 describes different types of memory controllers. Comparing this work with the described memory controllers, then this work is closest to the work carried out by Weber. However, there are certain differences in the design. This thesis proposes a memory

Figure 2.9: Production pattern of a regular producer

Figure 2.10: The worst-case of an irregular producer

controller, which is analyzable and is predictable. This is not the case for the memory controller designed by Weber, where the objective of the memory controller is not to be predictable. However, all other discussed memory controller lack predictable behavior and cannot provide a gross-to-net bandwidth translation.

This thesis is building on the work carried out by Åkesson in [Å05]. Åkesson is proposing an analytical analyzable memory controller which uses a static back-end schedule. The static back-end schedule is predetermined with the access parameters of the requestors. In the design phase a back-end schedule is calculated with the known mix of read and write accesses. The back-end schedule consists of a repeating access pattern. This allows translating the gross bandwidth to a net bandwidth. The drawback of this solution is that it has no flexibility of scheduling requests other than in the order described in the back-end schedule. This leads to a rather high worst-case latency. Furthermore, two (strict) traffic classes are proposed with high bandwidth (HB) and low latency (LL). Taken the work of Åkesson as starting point and identifying ways to improve the design leads to the proposed solution in this thesis. The work from Åkesson focuses on identifying the requirements for an analytical controller. The suggested solution is shown with an implementation in SystemC. In contrast the work for this thesis focuses on the design, implementation and verification of the memory controller at RTL level, which allows synthesis of the design.

# Chapter 3

# Design of the memory controller

This chapter describes the design process of the memory controller. It starts with a motivation of the problem set in Section 3.1. The system architecture is discussed in Section 3.2, and the requirements of the memory controller are identified in Section 3.3. Furthermore, it is explained how the memory controller can be used in an arbitrary system, and how it is used together with Æthereal. Section 3.4 discussed the design flow.

## 3.1 Motivation

Modern system architects face the problem that a flexible design is required for consumer products. When considering the market of mobile phones it appears that every year new product generations arise, with new features and functionalities. Comparing this with the design cycle of SoCs, where in contrast it takes years from the specification to the manufactured chip. However, in the specification phase it is hard to predict future features required from future markets. This is one of the reasons why more and more functionality is put into software and that upcoming SoC generations allow to be reconfigurable  $[GRG^{+}05]$ . SoCs require more and more storage for software and this requires a bigger storage capacity. This makes it necessary to provide high volume storage for SoCs. The difference in the manufacturing process for high volume storage and for standard SoCs makes it necessary and economical to place the dynamic memory off-chip. DDR2 is the current standard for high volume memories. The expense of a higher pin count for going off-chip is overcome, with sharing the memory among several IP blocks. Furthermore, sharing a memory allows having common address spaces allowing memory mapped communication between processes. Almost every IP block in a SoC requires access to a storage device [HP03]. Hennessy and Patterson in [HP03] identify memory as the bottle neck of most modern computer systems since the memory is shared among different IP blocks. An efficient arbitration is necessary to provide the IP blocks with the required bandwidth and to provide an high overall system performance.

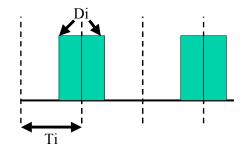

Figure 3.1 shows a system, where IP blocks (requestors) are connected to an external memory. The IP blocks are connected via an interconnect (like a bus, or a NoC) and a memory controller to the memory. The memory controller translates the requests from the requestors into accesses understood by the memory. Furthermore, the memory controller arbitrates between the requestors and allows having a shared memory.

Figure 3.1: Three requestor are connected through an interconnect

The objective of this thesis is to design a memory controller for real-time systems, which is predictable. A prototype is designed for the use with Æthereal, which provides a predictable communication infrastructure. The system architecture is discussed in Section 3.2. The requirements are identified in Section 3.3.

# 3.2 System Architecture

This section identifies the requirements when connecting the designed memory controller to a system, where a predictable memory controller is required. Furthermore, it discusses the basic architecture of the design and states the requirements twice. In the first case the requirements are identified if the memory controller is used in an arbitrary system, and in the second case if the memory controller is used with Æthereal.

Figure 3.1 shows different IP blocks connected via a communication infrastructure to a memory controller, which in turn is connected to an external dynamic memory. Buffering is required to decouple the traffic between the requestors and the memory. Without this decoupling the requestor stalls until the access to the memory is granted. However, by introducing decoupling buffers this problem is overcome.

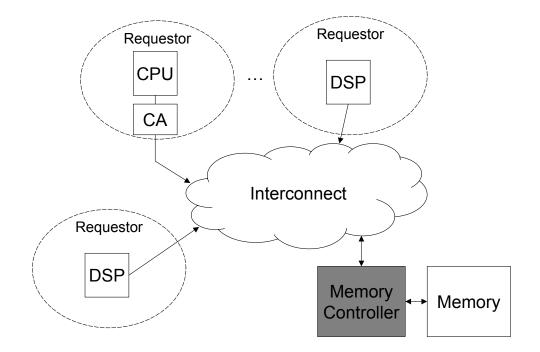

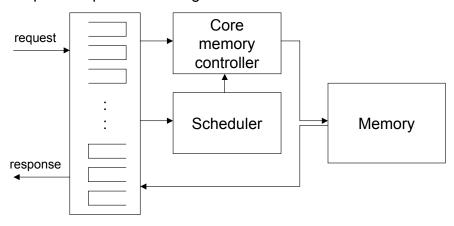

For a predictable memory controller design, it is necessary to implement a scheduler, which is predictable. The scheduler is responsible to provide the memory controller with the best fitting requestor according to the scheduling policy. The core memory controller translates the requests into accesses understood by the memory.

The memory controller is understood in this design process as a three component design with the following identified components:

• request and response buffering

- scheduler

- core memory controller

This three component view of the memory controller is illustrated in Figure 3.2. Summarizing this architecture, the incoming traffic is stored in the request buffer and thus decouples the traffic between requestor and memory. The scheduler arbitrates among the requestors and picks the best fitting requestor according to the scheduling policy. The core memory controller translates the requests to accesses understood by the memory.

request/response buffering

Figure 3.2: Modularization of the design

The above identified components are mandatory for the design of the memory controller. However, since the memory controller is (co-)designed for the use with Æthereal some simplifications can be made. For example the decoupling of the traffic is part of the network and it thus provides the required buffering. Section 3.2.2 discusses the integration steps, when using the memory controller with Æthereal. In contrast the next Section 3.2.1 discusses the required interface for the case when the memory controller is connected to an arbitrary system where a predictable memory controller is required.

#### 3.2.1 Request and response buffering requirements

The request buffers decouple the traffic from the requestor to the memory controller. This prevents the requestor from stalling when accessing the memory. In the other direction response buffers are required to decouple the response path. The size of the request buffers calculates to twice the maximum packet size to reach a decoupling for periodic requestors, as stated in Section 2.4.4. The size of the response buffers is twice the maximum size of the response data for periodic requestors. Furthermore, the memory controller expects that for each requestor address and data is provided in parallel.

A write request (of a requestor) is considered as schedulable if a full request is present in the request buffers because a read request (of a requestor) is considered as schedulable if a full request is present, and if there is enough space in the response buffers so that the read response can be placed in the response buffers. If a request is seen as schedulable only if a full request is received, then this mechanism prevents the memory controller from stalling during an access caused from outstanding data. However, below are the requirements of the request and response buffering for each requestor summarized and illustrated in Figure 3.3:

- request buffer, split up in:

- address

- data

- response buffer for the response data

- information

- if a request is pending

- if a request is read or write

- if enough space is in the response buffers for the response data

Figure 3.3: Request/response buffering for every requestor

The above described informations are required for every requestor. The core memory controller takes the data stored in the request buffer and transfers them in case of a write access to the memory. In the case of a read access the data is transfered by the memory controller from the memory to the response buffer. The scheduler requires the other above identified information's.

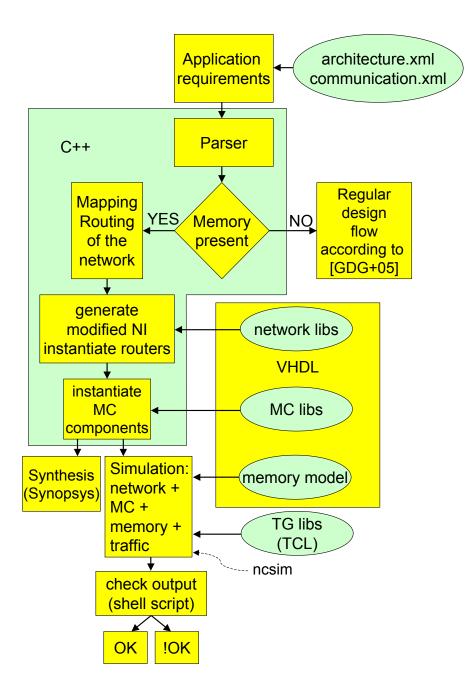

#### 3.2.2 Integration into Æthereal

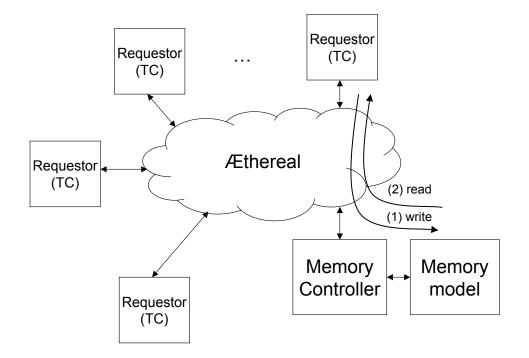

The objective of this thesis is to design a predictable memory controller which can be used with Æthereal. Æthereal provides an interconnection infrastructure for IP blocks  $[GRG^+05]$ . The extension is to provide the functionality, of interconnecting IP blocks with an external dynamic memory. The design flow of Æthereal  $[GDG^+05]$  provides the communication infrastructure and the goal is that automatically a memory controller is generated (at RTL level) with an interface to a DDR2 device, if a memory is present in the design. Figure 3.4 shows IP blocks which are connected via a NI to the network and to an off-chip memory. The off-chip memory is connected via a memory controller to the NI of the network.

Figure 3.4: Goal of the design

As identified in the last section, to use the designed memory controller it is necessary to provide decoupling of communication and computation. However, decoupling the traffic is a key element of Æthereal and thus request and response buffering is provided in the NI. Furthermore, as identified in the last section every requestor requires to provide the information:

- if a request is pending

- if the request is read/write

- if there is enough response space (in case of a read)

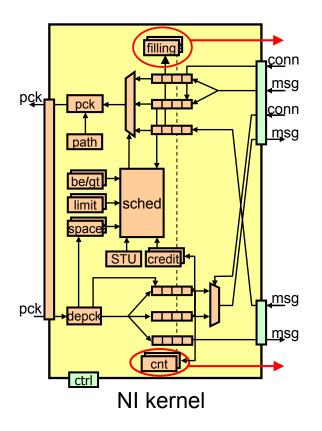

The filling of the buffers in the NI provides the information about a pending request and the information if enough response space is in the response buffer. Therefore, it is necessary to adapt the NI kernel [RDGP+05] to extract this information. To generate the information of request pending, the filling of the request buffer is compared to the packet size of a request available in the first word of the transaction. If it is equal or bigger than it indicates that a request is pending. The free response space is traced for the response buffers. Enough space is present if at least one response packet can fit into the response buffer. The adoptions in the NI kernel are illustrated in Figure 3.5 with the ovals.

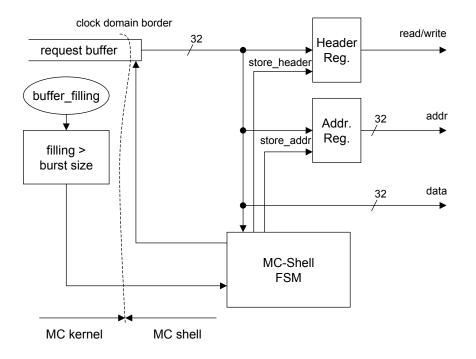

As identified in the last section, the memory controller expects the information address, data, and if the current request is of type read or write. Since the NI kernel does not provide the required information a simple shell is designed, which translates the Æthereal messages into address, data, and type of request. Figure 3.6 illustrates the NI shell for the memory controller.

The NI shell parses the incoming Æthereal message and sorts the information into the corresponding registers read/write, address. The message format of Æthereal is shown in [DRGR03].

Figure 3.5: Modifications to the kernel

Figure 3.6: Incoming messages are parsed by the NI memory controller (MC) shell

# 3.3 Requirements

This section identifies the requirements for a predictable memory controller design. The requirements are derived by discussing the key elements of Æthereal (which provides a predictable communication infrastructure) and identifying there the requirements for a predictable memory controller design. However, the memory controller can be used in any system where a predictable memory controller is required when fulfilling the requirements of buffering mentioned in Section 3.2.1. The example of Æthereal is used to illustrate the requirements with an example. Further, in this section it is described how the requirements are fulfilled in the proposed design.

Æthereal provides hard real time guarantees and a predictable communication infrastructure. In the design phase it allows to specify bandwidth and latency for every IP block. The hardware for the communication infrastructure is generated automatically and the bandwidth and latency bounds are provided as specified, without the need of simulation together with other components [GRG<sup>+</sup>05]. Consult Section 2.4.1 for more details.

As stated in Section 2.4.1 a predictable system needs to be analyzable. This means to deliver an analyzable memory controller it is required to have an analyzable model of the dynamic memory. Section 2.1.3 showed that the efficiency of the memory depends on the traffic patterns and thus makes it difficult to provide an analyzable model of the memory. However, accessing the memory with a determined traffic pattern allows translating the bandwidth of the memory from a gross bandwidth to a net bandwidth and determines the efficiency of the memory. The gross bandwidth is the bandwidth specified in the data sheet of the memory, and defines the maximum throughput of the memory without considering refresh, and other losses caused by read/write switches, etc. The net bandwidth is the effective available bandwidth to the requestors. The net bandwidth is a result of multiplying the memory efficiency with the gross bandwidth. The question is how to provide a traffic pattern, which makes the memory controller analyzable and efficient? The reasoning to this question and a possible solution is presented in Section 3.3.1. Note that an analyzable memory controller must provide a gross-to-net bandwidth translation.

As stated in Section 2.4.1 Æthereal allows to separate the design process of the functionality and the communication. The consequence is that there is decoupling between computation and communication, as motivated in Section 2.4.4. This allows every IP block to be analyzed individually. However, accessing the memory requires to first activate the bank, access a particular column in the row, and to precharge the row afterwards. Considering two requestors accessing two different banks and that the requests do not interfering with each other, then the accesses can be carried out consecutively without introducing idle states. However, considering two accesses going to the same bank, but not the same row, the second access has to be stalled until the first access has finished. The scheduling has to consider the time of precharging the row and wait the time until a new activate command is allowed to the same bank. This example shows that a memory access relies on the current state of the memory, which was caused by another requestor. A similar mechanism has to be considered when changing the directions between two accesses. In this case idle cycles on the data bus have to be inserted before the second requestor is able to access the memory [Ass04]. To provide an analyzable model for every requestor it is not acceptable to consider the current state of the memory, caused by prior accesses of different requestors. Therefore, a further requirement of the memory controller is to make the memory controller predictable providing a clear requestor isolation.

The list below summarizes the constraints and requirements, which are identified for the design of the memory controller:

- predictable minimum bandwidth and maximum latency

- gross-to-net bandwidth translation (predictable net bandwidth and latency)

- provide requestor isolation (net bandwidth and latency per requestor)

- efficient resource utilization