# MSc THESIS

# A predictable and composable front-end for system on chip memory controllers

Eelke Strooisma

## Abstract

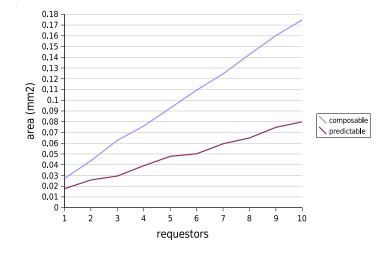

Today, verification and integration dominate the cost of developing a System-on-chip. A front-end for a predictable and composable memory controller is proposed that has the purpose to reduce verification and integration effort. The front-end acts as a scheduler for shared external memory; a back-end is required to access the memory. A predictable memory controller guarantees maximum latency and a minimum net bandwidth at design time. This allows realtime requirements to be satisfied without simulation. Composability means that the service of a requestor is not affected by the behavior of other requestors. Hence, components can be verified in isolation and do not need to be reverified after integration. The behavior of a back-end is abstracted by memory accesses. A predictable and composable mapping from memory accesses to SDRAM commands is proposed. Analysis of the memory accesses shows that the access granularity must be increased for newer memory devices to maintain high efficiency. A modular design and strict separation of concerns is essential to simplify timing analysis. When composability is required, responses are delayed such that the behavior is not affected by interference from other requestors. The front-end is synthesized

for CMOS090LP technology. The predictable front-end consumes  $0.201mm^2$  for five requestors and when composability is enabled,  $0.246mm^2$  is required. However, the buffers to delay the responses need  $0.76mm^2$  additionally.

CE-MS-2007-19

Faculty of Electrical Engineering, Mathematics and Computer Science

# A predictable and composable front-end for system on chip memory controllers

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

$\mathrm{in}$

## COMPUTER ENGINEERING

by

Eelke Strooisma born in Leeuwarden, The Netherlands

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

# A predictable and composable front-end for system on chip memory controllers

#### by Eelke Strooisma

#### Abstract

**\oday**, verification and integration dominate the cost of developing a System-on-chip. A front-end for a predictable and composable memory controller is proposed that has the purpose to reduce verification and integration effort. The front-end acts as a scheduler for shared external memory; a back-end is required to access the memory. A predictable memory controller guarantees maximum latency and minimum net bandwidth at design time. This allows real-time requirements to be satisfied without simulation. Composability means that the service of a requestor is not affected by the behaviour of other requestors. Hence, components can be verified in isolation and do not need to be reverified after integration. The behaviour of a backend is abstracted by memory accesses. A predictable and composable mapping from memory accesses to SDRAM commands is proposed. Analysis of the memory accesses shows that the access granularity must be increased for newer memory devices to maintain high efficiency. A modular design and strict separation of concerns is essential to simplify timing analysis. When composability is required, responses are delayed such that the behaviour is not affected by interference from other requestors. The front-end is synthesized for CMOS090LP technology. The predictable front-end consumes  $0.201mm^2$  for five requestors and when composability is enabled,  $0.246mm^2$  is required. However, the buffers to delay the responses need to store 26k bits in total, resulting in an additional area of  $0.76mm^2$ .

| Laboratory | : | Computer Engineering |

|------------|---|----------------------|

| Codenumber | : | CE-MS-2007-19        |

Committee Members

| Advisor: | Kees Goossens, CE, TU Delft, NXP Semiconductors |

|----------|-------------------------------------------------|

| Member:  | Henk Sips, PDS, TU Delft                        |

| Member:  | Ben Juurlink, CE, TU Delft                      |

| Member:  | Said Hamdioui, CE, TU Delft                     |

# Contents

| List of Figures  | viii |

|------------------|------|

| List of Tables   | x    |

| List of Terms    | xi   |

| Acknowledgements | xiii |

| 1        | Intr | oducti       | ion                               | 1                 |

|----------|------|--------------|-----------------------------------|-------------------|

|          | 1.1  | Proble       | em description                    | . 1               |

|          | 1.2  | Goal         |                                   | . 1               |

|          | 1.3  | Contex       | xt                                | . 2               |

|          | 1.4  | Struct       | gure                              | . 3               |

| <b>2</b> | Rec  | uirem        | ents                              | 5                 |

|          | 2.1  | -<br>Verifia | able                              | . 5               |

|          |      | 2.1.1        | Verification of real-time systems | . 5               |

|          |      | 2.1.2        | Predictable                       | . 7               |

|          |      | 2.1.3        | Composable                        |                   |

|          | 2.2  | Second       | dary requirements                 |                   |

|          |      | 2.2.1        | Configurable                      | . 10              |

|          |      | 2.2.2        | Performance                       |                   |

|          |      | 2.2.3        | Reusable                          |                   |

|          | 2.3  | Conclu       | usions                            |                   |

| 0        | D.1  | 1            |                                   | 10                |

| 3        |      | ated w       | <b>'OFK</b><br>usions             | <b>13</b><br>. 14 |

|          | 3.1  | Concit       |                                   | . 14              |

| 4        | SDI  | RAM          |                                   | 15                |

|          | 4.1  | Histor       | у                                 | . 15              |

|          | 4.2  | Archit       | cecture                           | . 15              |

|          | 4.3  | Access       | sing memory                       | . 15              |

|          | 4.4  | Refres       | shing memory                      | . 17              |

|          | 4.5  | Comm         | nands                             | . 18              |

|          | 4.6  | Efficie      | ncy                               | . 18              |

|          |      | 4.6.1        | Refresh efficiency                | . 20              |

|          |      | 4.6.2        | Data efficiency                   | . 20              |

|          |      | 4.6.3        | Bank efficiency                   | . 21              |

|          |      | 4.6.4        | Read/write switching efficiency   | . 21              |

|          |      | 4.6.5        | Command efficiency                | . 21              |

|          |      |              |                                   |                   |

|   | 4.7            | Concl          | usions                                   | 22        |

|---|----------------|----------------|------------------------------------------|-----------|

| 5 | Me             | mory o         | controllers                              | <b>23</b> |

|   | 5.1            | Tasks          |                                          | 23        |

|   |                | 5.1.1          | Request scheduling                       | 23        |

|   |                | 5.1.2          | Memory mapping                           | 24        |

|   |                | 5.1.3          | Command generation                       | 25        |

|   |                | 5.1.4          | Memory management                        | 25        |

|   | 5.2            | Archit         | tecture                                  | 25        |

|   |                | 5.2.1          | Requestor interfaces                     | 26        |

|   |                | 5.2.2          | Arbiter                                  | 26        |

|   |                | 5.2.3          | Memory interface                         | 26        |

|   | 5.3            | Concl          | usions                                   | 27        |

| 6 | Me             | mory o         | command patterns                         | 31        |

|   | 6.1            | •              | ctable memory                            | 31        |

|   | 6.2            |                | bry access                               |           |

|   | 6.3            |                | bry command patterns                     |           |

|   |                | 6.3.1          | Access patterns                          |           |

|   |                | 6.3.2          | Switching pattern                        |           |

|   |                | 6.3.3          | Refresh pattern                          |           |

|   |                | 6.3.4          | Memory map                               |           |

|   |                | 6.3.5          | Results                                  |           |

|   | 6.4            | Memo           | bry access to pattern map                | 41        |

|   |                | 6.4.1          | Predictable memory access to pattern map |           |

|   |                | 6.4.2          | Composable memory access to pattern map  |           |

|   |                | 6.4.3          | Results                                  | 48        |

|   | 6.5            | Concl          | usions                                   | 50        |

| 7 | $\mathbf{Des}$ | ion            |                                          | 63        |

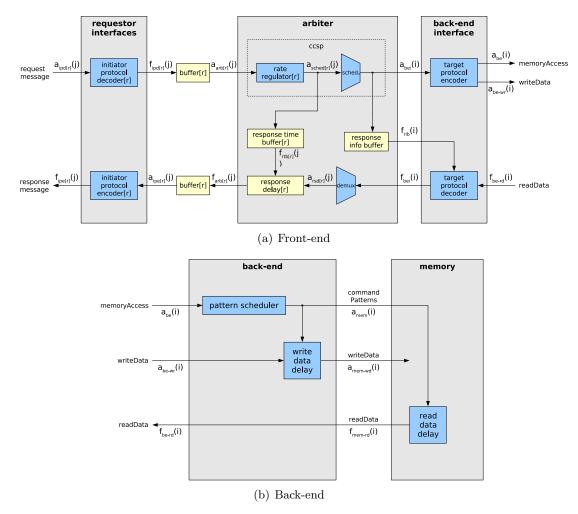

| • | 7.1            |                | tecture                                  | 63        |

|   | 1.1            | 7.1.1          | Requestor interfaces                     |           |

|   |                | 7.1.2          | Arbiter                                  |           |

|   |                | 7.1.2          | Back-end interface                       |           |

|   |                | 7.1.4          | Back-end                                 |           |

|   |                | 7.1.5          | Generalisation                           |           |

|   | 7.2            |                | flow analysis                            |           |

|   | 1.2            | 7.2.1          | Back-end                                 |           |

|   |                | 7.2.1<br>7.2.2 | Back-end interface                       |           |

|   |                | 7.2.2<br>7.2.3 | Arbiter                                  |           |

|   |                | 7.2.3<br>7.2.4 | Requestor interfaces                     |           |

|   | 73             | Concl          | •                                        | 76        |

| 8  | Imp                                                                           | olemen                                                                                                                         | tation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79                                                                                                                                                        |

|----|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

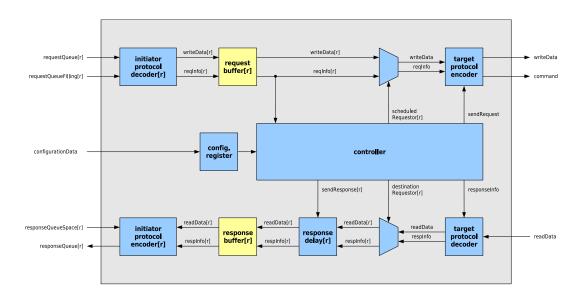

|    | 8.1                                                                           | Functi                                                                                                                         | ional behaviour                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 79                                                                                                                                                      |

|    | 8.2                                                                           | Reque                                                                                                                          | st and response format                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 80                                                                                                                                                      |

|    | 8.3                                                                           | Reque                                                                                                                          | stor interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 80                                                                                                                                                      |

|    |                                                                               | 8.3.1                                                                                                                          | Data-width converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 82                                                                                                                                                      |

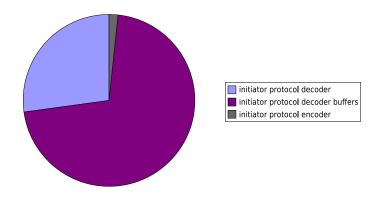

|    |                                                                               | 8.3.2                                                                                                                          | Initiator protocol decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 82                                                                                                                                                      |

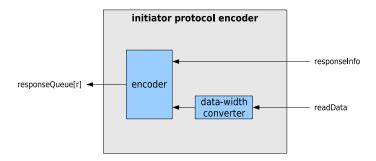

|    |                                                                               | 8.3.3                                                                                                                          | Initiator protocol encoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 86                                                                                                                                                      |

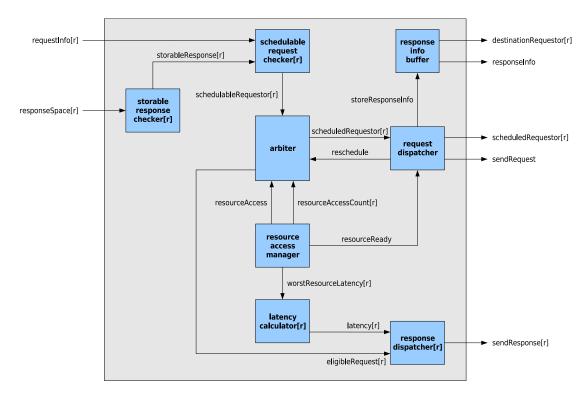

|    | 8.4                                                                           | Arbite                                                                                                                         | er                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 87                                                                                                                                                      |

|    |                                                                               | 8.4.1                                                                                                                          | Storable response checker                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 87                                                                                                                                                      |

|    |                                                                               | 8.4.2                                                                                                                          | Schedulable request checker                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 89                                                                                                                                                      |

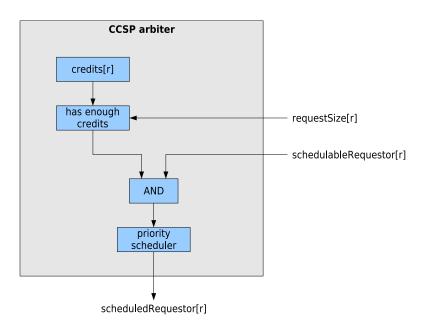

|    |                                                                               | 8.4.3                                                                                                                          | CCSP Arbiter                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 89                                                                                                                                                      |

|    |                                                                               | 8.4.4                                                                                                                          | Request dispatcher                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91                                                                                                                                                        |

|    |                                                                               | 8.4.5                                                                                                                          | Response info buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 92                                                                                                                                                      |

|    |                                                                               | 8.4.6                                                                                                                          | Resource access manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 93                                                                                                                                                      |

|    |                                                                               | 8.4.7                                                                                                                          | Latency calculator                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 95                                                                                                                                                      |

|    |                                                                               | 8.4.8                                                                                                                          | Response dispatcher                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 96                                                                                                                                                      |

|    |                                                                               | 8.4.9                                                                                                                          | Response delay block                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 97                                                                                                                                                      |

|    | 8.5                                                                           | Back-e                                                                                                                         | end interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 99                                                                                                                                                      |

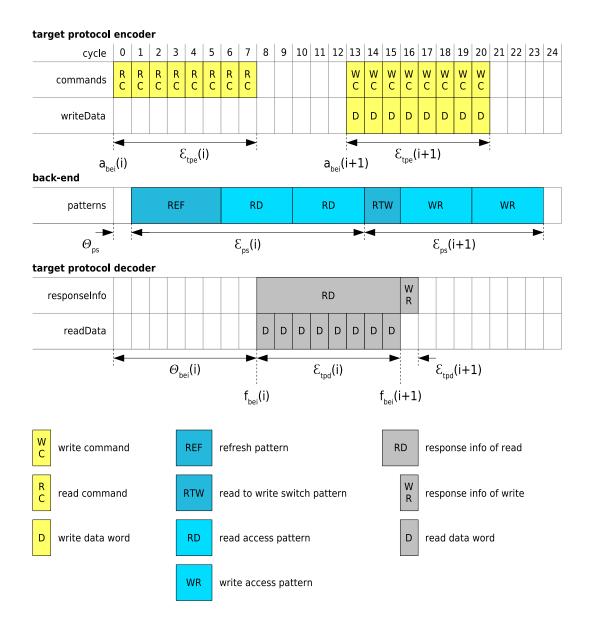

|    |                                                                               | 8.5.1                                                                                                                          | Target protocol encoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 100                                                                                                                                                     |

|    |                                                                               | 8.5.2                                                                                                                          | Target protocol decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 100                                                                                                                                                     |

|    | 8.6                                                                           | Config                                                                                                                         | $\operatorname{guration}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 101                                                                                                                                                       |

|    | 8.7                                                                           | Conch                                                                                                                          | usions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 102                                                                                                                                                       |

|    | _                                                                             |                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                           |

| 9  |                                                                               | perime                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 105                                                                                                                                                       |

|    |                                                                               |                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                           |

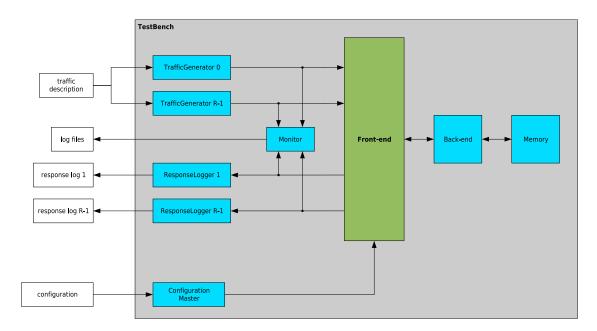

|    | 9.1                                                                           |                                                                                                                                | ench                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                           |

|    | $9.1 \\ 9.2$                                                                  | Use ca                                                                                                                         | ase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105                                                                                                                                                       |

|    |                                                                               | Use ca<br>9.2.1                                                                                                                | Se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 105<br>108                                                                                                                                                |

|    | 9.2                                                                           | Use ca<br>9.2.1<br>9.2.2                                                                                                       | ase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105<br>108<br>109                                                                                                                                         |

|    |                                                                               | Use ca<br>9.2.1<br>9.2.2<br>Simula                                                                                             | ase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105<br>108<br>109<br>110                                                                                                                                  |

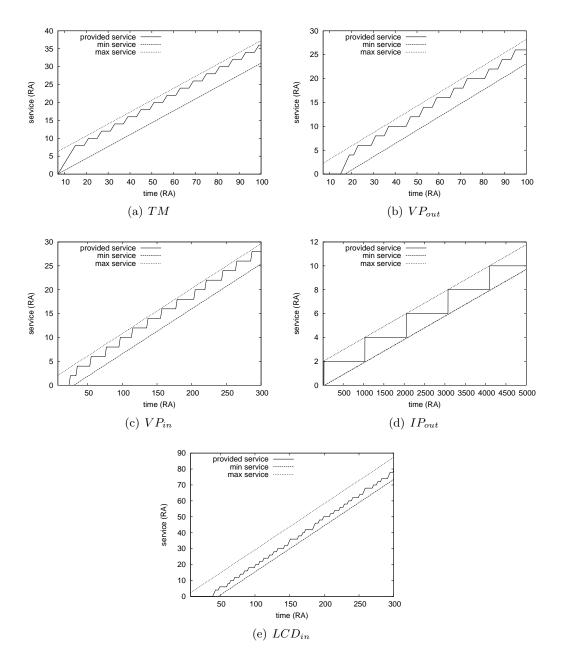

|    | 9.2                                                                           | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1                                                                                    | ase    Configuration      Latency    Latency      ation    Average net bandwidth                                                                                                                                                                                                                                                                                                                                                                                                          | 105<br>108<br>109<br>110<br>110                                                                                                                           |

|    | 9.2                                                                           | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2                                                                           | ase       Configuration         Latency       Lation         Average net bandwidth       Latency         Latency distribution       Latency                                                                                                                                                                                                                                                                                                                                               | 105<br>108<br>109<br>110<br>110<br>111                                                                                                                    |

|    | 9.2                                                                           | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2<br>9.3.3                                                                  | ase       Configuration         Latency       Latency         ation       Average net bandwidth         Latency distribution       Latency of subcomponents                                                                                                                                                                                                                                                                                                                               | . 105<br>. 108<br>. 109<br>. 110<br>. 110<br>. 111<br>. 112                                                                                               |

|    | 9.2                                                                           | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4                                                         | ase       Configuration         Latency       Latency         ation       Average net bandwidth         Latency distribution       Latency         Latency of subcomponents       Abstract service                                                                                                                                                                                                                                                                                        | . 105<br>. 108<br>. 109<br>. 110<br>. 110<br>. 111<br>. 112<br>. 113                                                                                      |

|    | 9.2                                                                           | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5                                                | See       Configuration         Latency       Latency         ation       Average net bandwidth         Latency distribution       Latency distribution         Latency of subcomponents       Abstract service         Mapping from memory access to real time domain       Image domain                                                                                                                                                                                                 | . 105<br>. 108<br>. 109<br>. 110<br>. 110<br>. 111<br>. 111<br>. 112<br>. 113<br>. 113                                                                    |

|    | 9.2                                                                           | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6                                       | See       Configuration         Latency       Latency         ation       Average net bandwidth         Latency distribution       Latency distribution         Latency of subcomponents       Abstract service         Mapping from memory access to real time domain       Buffer filling                                                                                                                                                                                               | <ul> <li>105</li> <li>108</li> <li>109</li> <li>110</li> <li>110</li> <li>111</li> <li>112</li> <li>113</li> <li>113</li> <li>114</li> </ul>              |

|    | 9.2                                                                           | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5                                                | See       Configuration         Latency       Latency         ation       Average net bandwidth         Latency distribution       Latency distribution         Latency of subcomponents       Abstract service         Mapping from memory access to real time domain       Buffer filling                                                                                                                                                                                               | <ul> <li>105</li> <li>108</li> <li>109</li> <li>110</li> <li>110</li> <li>111</li> <li>112</li> <li>113</li> <li>113</li> <li>114</li> <li>115</li> </ul> |

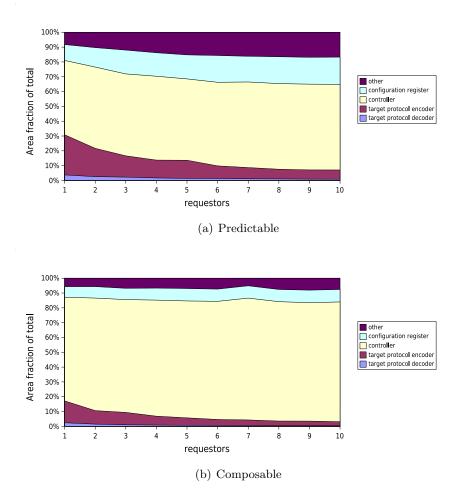

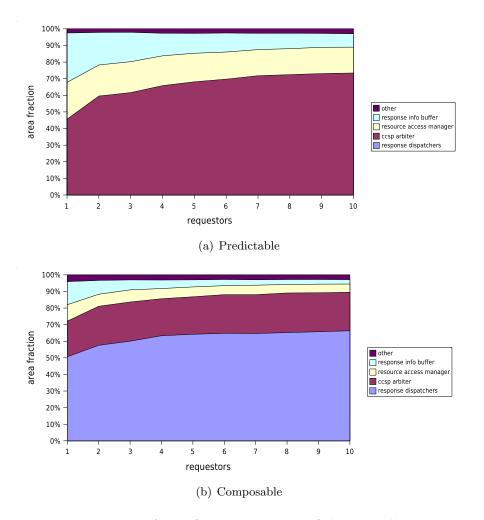

|    | 9.2                                                                           | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>Synthe<br>9.4.1                    | See       Configuration         Latency       Latency         ation       Latency         Average net bandwidth       Latency         Latency distribution       Latency distribution         Latency of subcomponents       Abstract service         Mapping from memory access to real time domain       Buffer filling         Requestor interfaces       Sector                                                                                                                       | $\begin{array}{cccc} 105\\ 108\\ 109\\ 110\\ 110\\ 111\\ 112\\ 113\\ 113\\ 114\\ 115\\ 115\\ 115\end{array}$                                              |

|    | 9.2                                                                           | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>Synthe                             | See       Configuration         Latency       Latency         ation       Average net bandwidth         Latency distribution       Latency distribution         Latency of subcomponents       Abstract service         Mapping from memory access to real time domain       Buffer filling                                                                                                                                                                                               | $\begin{array}{cccc} 105\\ 108\\ 109\\ 110\\ 110\\ 111\\ 112\\ 113\\ 113\\ 114\\ 115\\ 115\\ 115\end{array}$                                              |

|    | 9.2                                                                           | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>Synthe<br>9.4.1<br>9.4.2           | See       Configuration         Latency       Latency         ation       Latency         Average net bandwidth       Latency         Latency distribution       Latency distribution         Latency of subcomponents       Abstract service         Mapping from memory access to real time domain       Buffer filling         Requestor interfaces       Sector                                                                                                                       | $\begin{array}{cccc} 105\\ 108\\ 109\\ 110\\ 110\\ 111\\ 112\\ 113\\ 113\\ 113\\ 114\\ 115\\ 115\\ 115\\ 115\end{array}$                                  |

| 10 | <ul> <li>9.2</li> <li>9.3</li> <li>9.4</li> <li>9.5</li> </ul>                | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>Synthe<br>9.4.1<br>9.4.2<br>Conclu | ase       Configuration         Latency       Latency         ation       Average net bandwidth         Latency distribution       Latency distribution         Latency of subcomponents       Abstract service         Mapping from memory access to real time domain       Buffer filling         esis       Arbiter and back-end interface                                                                                                                                             | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                      |

| 10 | <ul> <li>9.2</li> <li>9.3</li> <li>9.4</li> <li>9.5</li> </ul>                | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>Synthe<br>9.4.1<br>9.4.2           | ase       Configuration         Latency       Latency         ation       Average net bandwidth         Latency distribution       Latency distribution         Latency of subcomponents       Abstract service         Mapping from memory access to real time domain       Buffer filling         esis       Arbiter and back-end interface                                                                                                                                             | $\begin{array}{cccc} 105\\ 108\\ 109\\ 110\\ 110\\ 111\\ 112\\ 113\\ 113\\ 113\\ 114\\ 115\\ 115\\ 115\\ 115\end{array}$                                  |

|    | <ul> <li>9.2</li> <li>9.3</li> <li>9.4</li> <li>9.5</li> <li>O Cor</li> </ul> | Use ca<br>9.2.1<br>9.2.2<br>Simula<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>Synthe<br>9.4.1<br>9.4.2<br>Conclu | ase       Configuration         Latency       Iteration         ation       Average net bandwidth         Latency distribution       Iteration         Latency of subcomponents       Iteration         Abstract service       Iteration         Mapping from memory access to real time domain       Iteration         Buffer filling       Iteration         Requestor interfaces       Iteration         Arbiter and back-end interface       Iteration         usions       Iteration | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                      |

| Α            | SDRAM command timing constraints | 139 |

|--------------|----------------------------------|-----|

| В            | Memory command patterns          | 141 |

| С            | Serialized AXI protocol          | 143 |

| D            | CCSP arbiter pseudo code         | 147 |

| $\mathbf{E}$ | Abstraction layers               | 151 |

# List of Figures

| $1.1 \\ 1.2$ | Application, jobs and tasks2Memory controller inside a SoC3 |

|--------------|-------------------------------------------------------------|

| $1.2 \\ 1.3$ | Abstract interface of a memory controller    4              |

| 2.1          | Mapping of an application to a SoC                          |

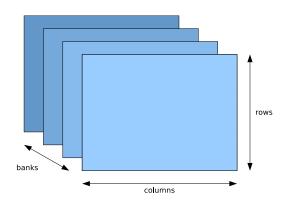

| 4.1          | SDRAM architecture                                          |

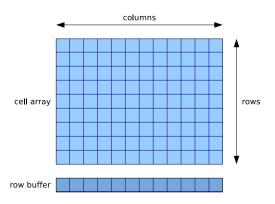

| 4.2          | Bank architecture                                           |

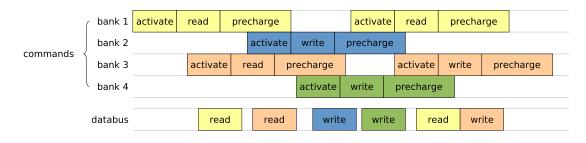

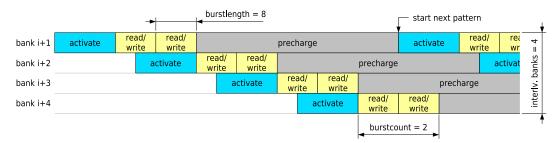

| 4.3          | Bank interleaving                                           |

| 4.4          | Timing constraints of SDRAM commands                        |

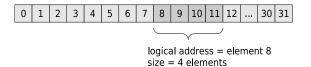

| 5.1          | The memory as perceived by a requestor                      |

| 5.2          | Sequential memory map                                       |

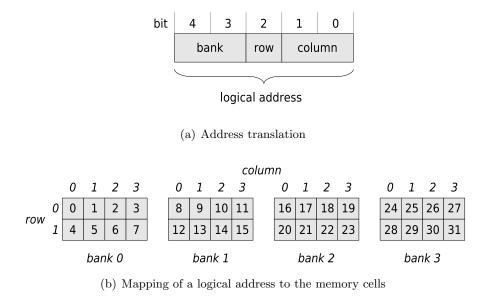

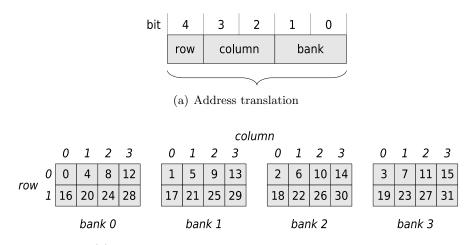

| 5.3          | Bank interleaving memory map                                |

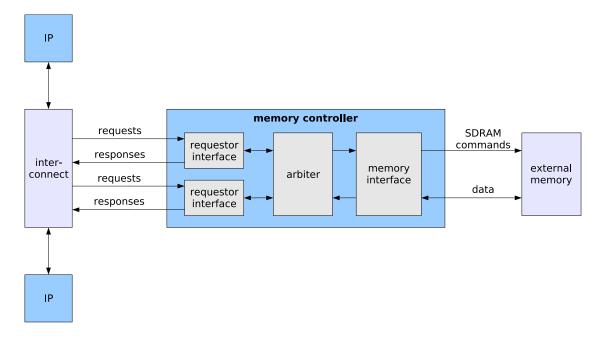

| 5.4          | General structure of a memory controller 29                 |

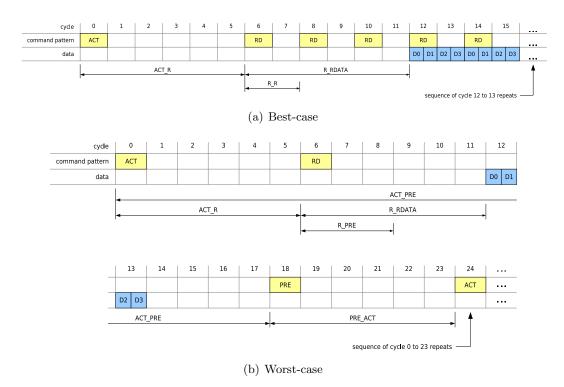

| 6.1          | Sequences for executing read bursts                         |

| 6.2          | Memory partitioning and request alignment                   |

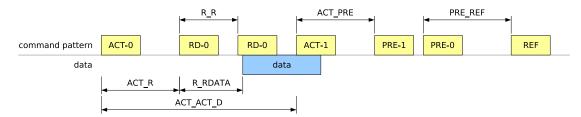

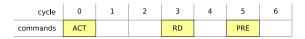

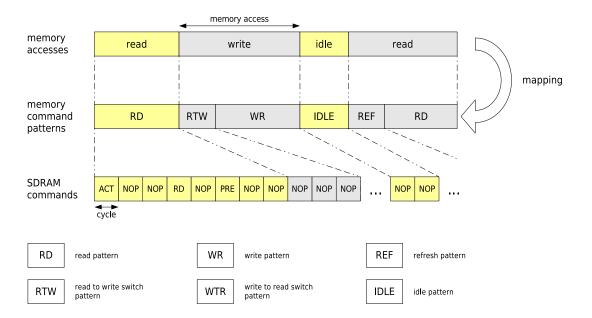

| 6.3          | Memory command pattern that performs a read operation       |

| 6.4          | Read and write pattern 52                                   |

| 6.5          | Memory map for generalized basic groups 53                  |

| 6.6          | Bank efficiency for read patterns                           |

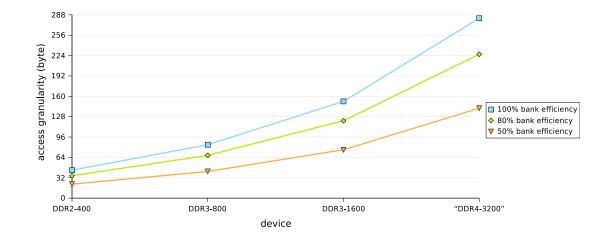

| 6.7          | Granularity trend of read patterns                          |

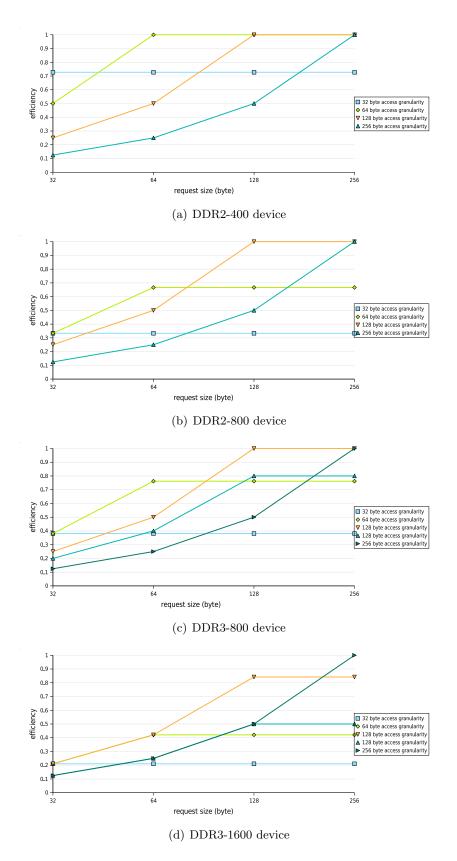

| 6.8          | Bank and data efficiency for read patterns                  |

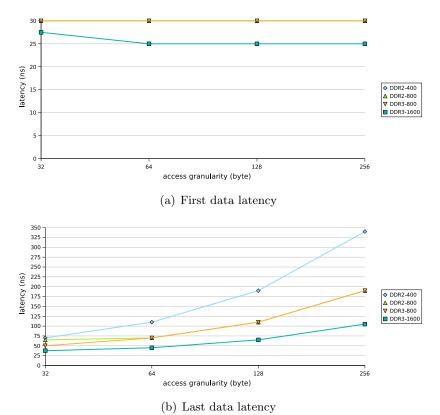

| 6.9          | Data latency of read patterns                               |

| 6.10         |                                                             |

| 6.11         |                                                             |

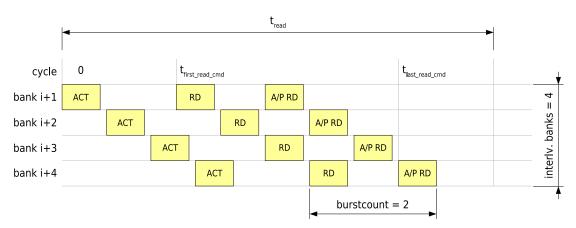

| 6.12         | Timing details of a read request                            |

|              | The composition of the patterns of the CAM 59               |

|              | Two sequence of patterns according to the CAM 59            |

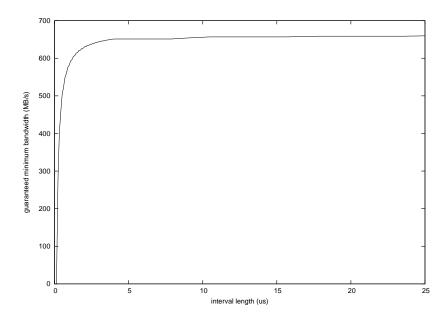

| 6.15         | Guaranteed net bandwidth for DDR2-400 device                |

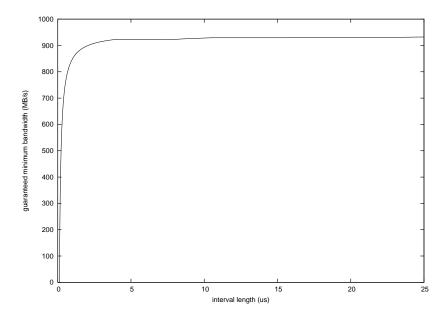

|              | Guaranteed net bandwidth for DDR2-800 device                |

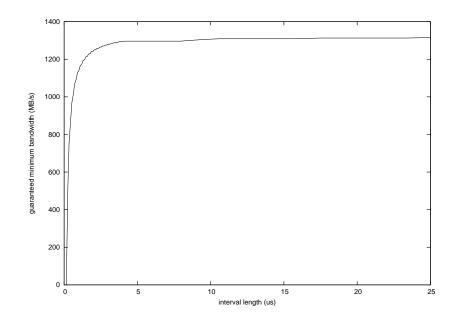

| 6.17         | Guaranteed net bandwidth for DDR3-800 device                |

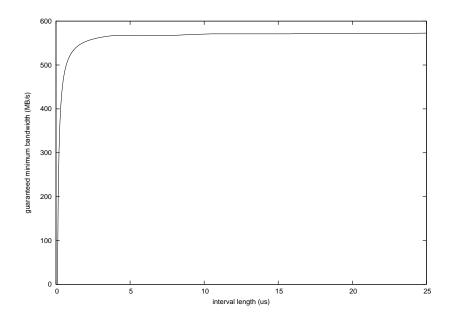

| 6.18         | Guaranteed net bandwidth for DDR3-1600 device               |

| 7.1          | Memory controller split into front-end and back-end 64      |

| 7.2          | Data flow model                                             |

| 7.3          | Data flow of the memory controller                          |

| 8.1          | Block diagram of front-end 80                               |

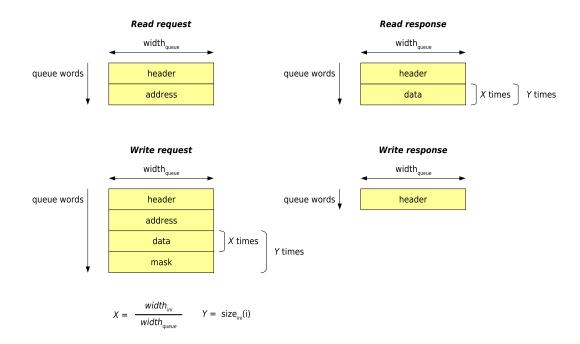

| 8.2          | Format of the serialized AXI protocol                       |

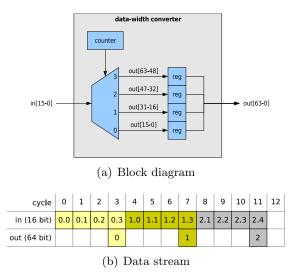

| 8.3          | Data-width converter for 16 to 64 bits                      |

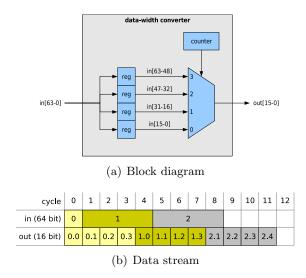

| 8.4          | Data-width converter for 64 to 16 bits                      |

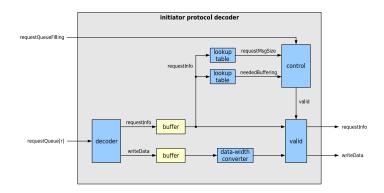

| 8.5          | Block diagram of initiator protocol decoder                  |

|--------------|--------------------------------------------------------------|

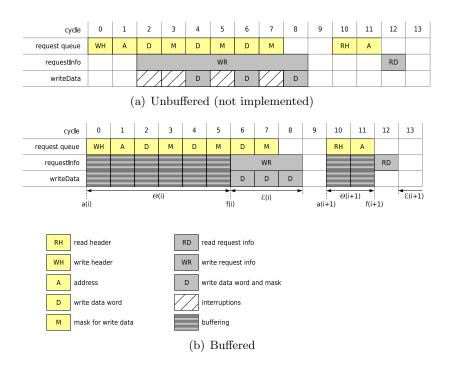

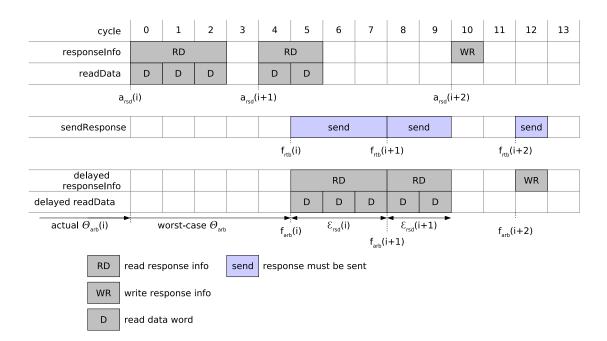

| 8.6          | Timing behaviour of an initiator protocol decoder            |

| 8.7          | Timing behaviour of an initiator protocol encoder            |

| 8.8          | Initiator protocol encoder                                   |

| 8.9          | Block diagram of the controller                              |

| 8.10         | Simplified block diagram of CCSP arbiter                     |

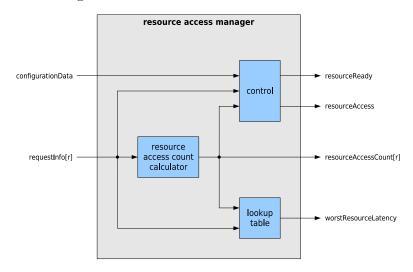

| 8.11         | Block diagram of resource access manager                     |

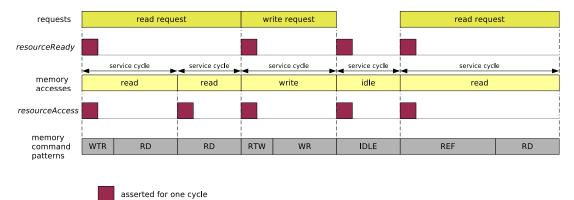

| 8.12         | 0                                                            |

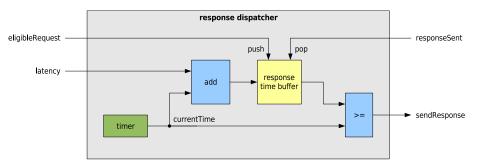

|              | Block diagram of response dispatcher                         |

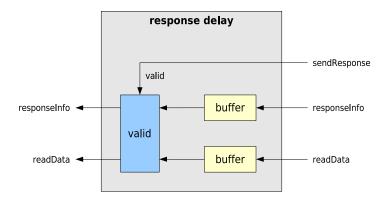

|              | Response delay block                                         |

| 8.15         | Timing behaviour of the response delay block                 |

| 8.16         | Timing diagram of the back-end interface                     |

| 0.1          |                                                              |

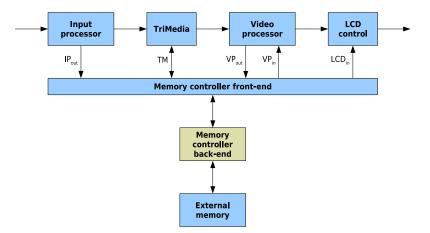

| $9.1 \\ 9.2$ | Test bench106Architecture of the use case107                 |

| -            |                                                              |

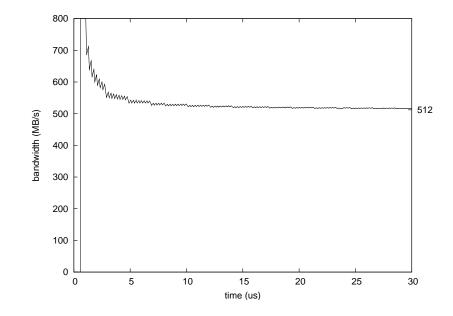

| $9.3 \\ 9.4$ | Average net bandwidth of a 16 bits memory                    |

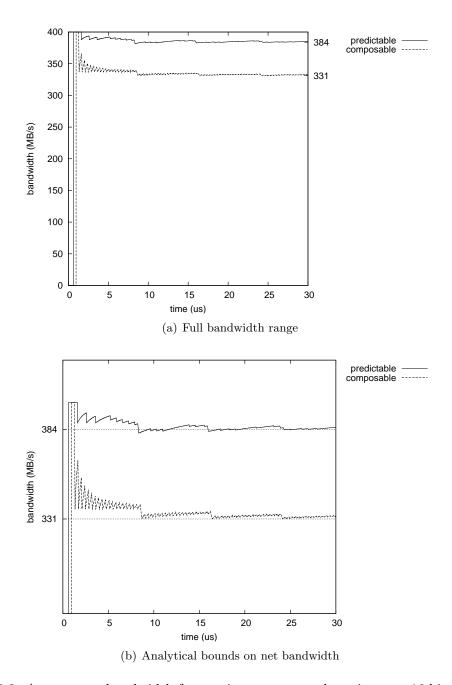

|              | Average net bandwidth of a 16 bits memory                    |

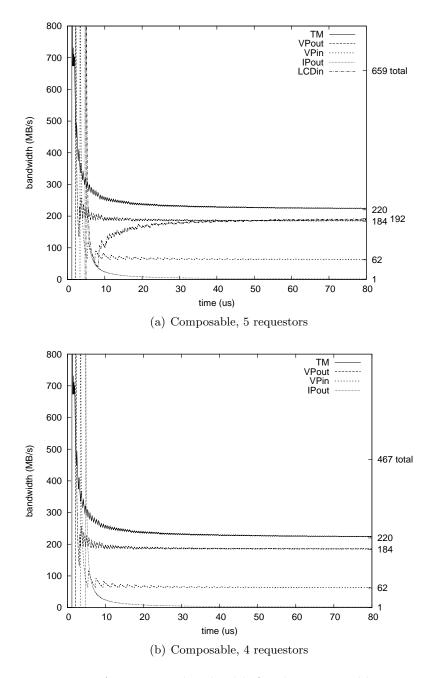

| 9.5          | Average net bandwidth for the composable use case            |

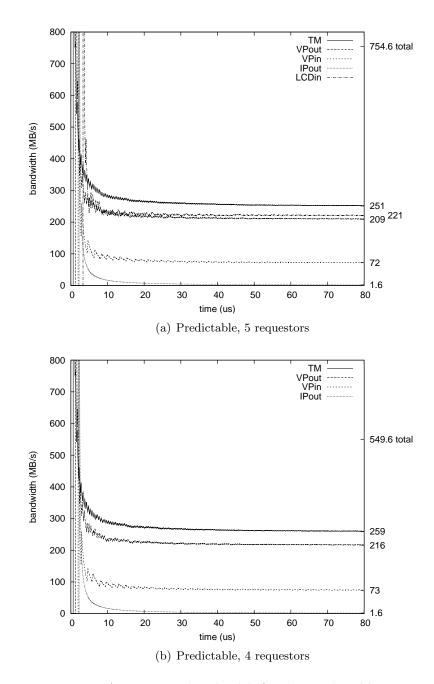

| 9.6          | Average net bandwidth for the predictable use case           |

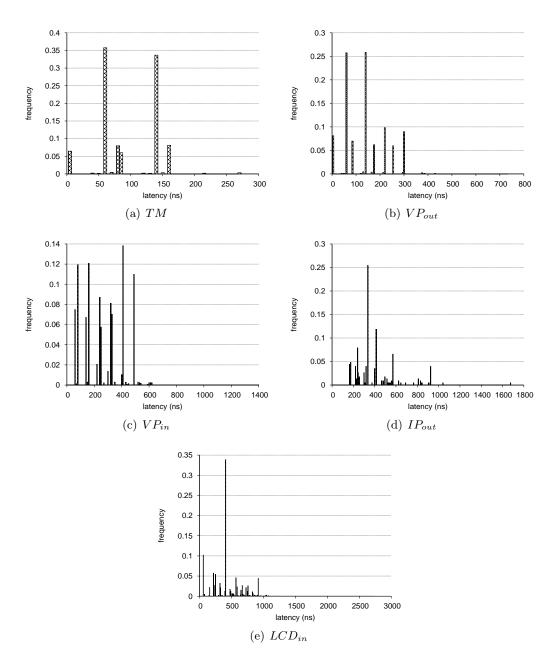

| 9.7          | Latency distribution of the predictable front-end            |

| 9.8          | Latency distribution of the composable front-end             |

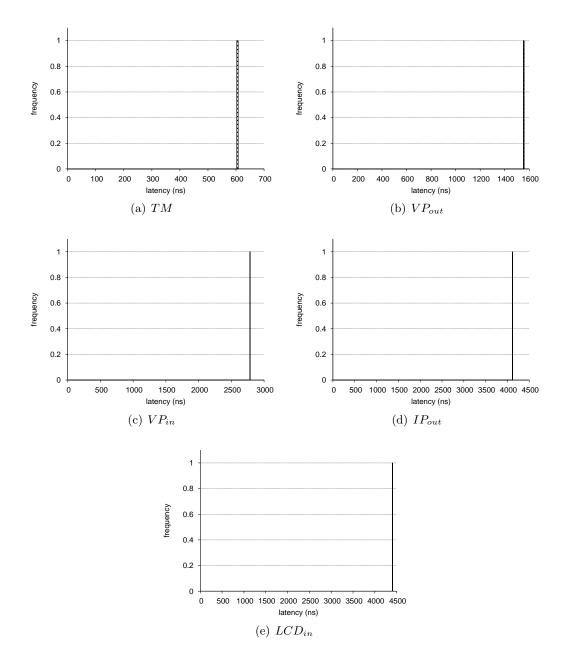

| 9.9          | Latency fraction of the subcomponents                        |

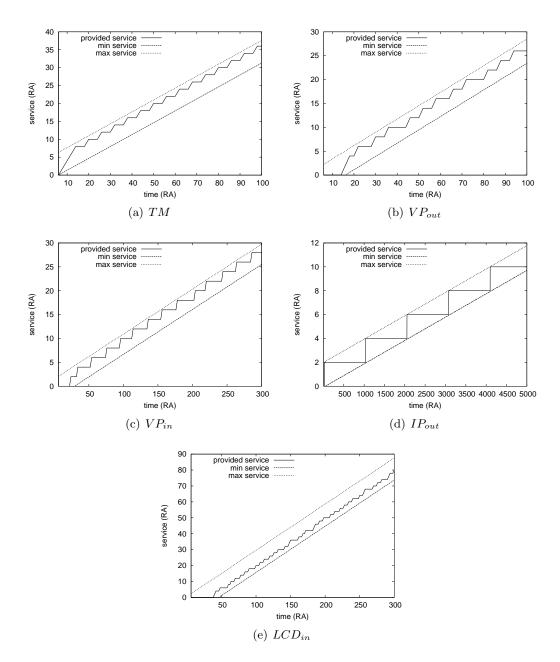

| 9.10         | 1                                                            |

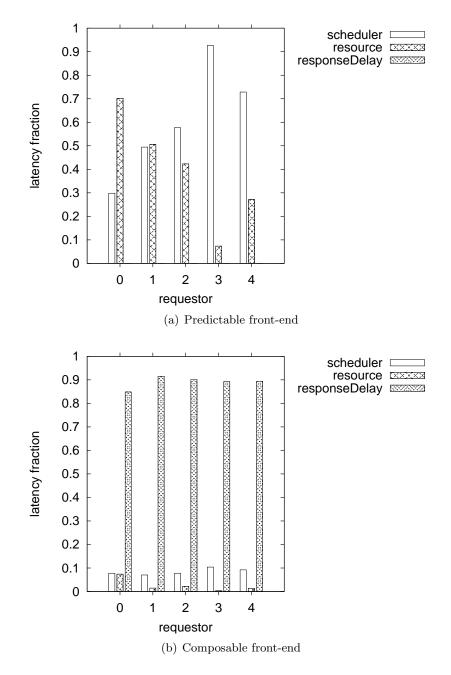

|              | Service of the composable front-end                          |

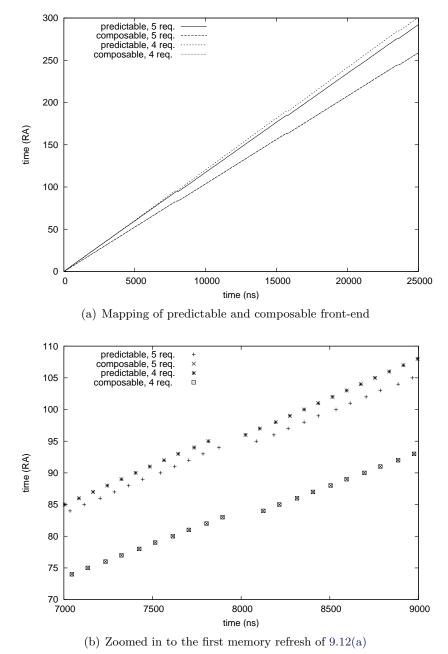

|              | Mapping of resource accesses to real time                    |

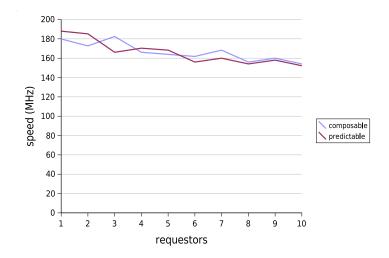

|              | Maximum frequency for front-end                              |

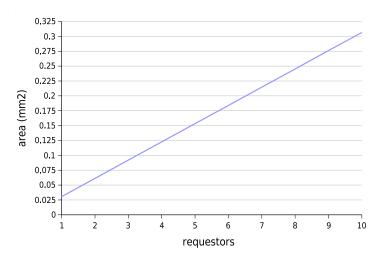

|              | Area of all requestor interfaces                             |

|              | Area of the components of a single requestor interface       |

|              | Area of the components of the arbiter and back-end interface |

|              | Area of the components of the arbiter and back-end interface |

| 9.10         |                                                              |

| E.1          | Abstraction layers on the data domain                        |

| E.2          | Abstraction layers on the time domain                        |

|              |                                                              |

# List of Tables

| 4.1          | Command timing constraints 19                                                                                                                  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1          | Properties of a DDR2-800 memory device                                                                                                         |

| 6.2          | Symbols of the memory command patterns                                                                                                         |

| 6.3          | Width of the physical addresses (bits) 38                                                                                                      |

| 6.4          | Truth table of the PAM 43                                                                                                                      |

| 6.5          | Notation                                                                                                                                       |

| 6.6          | Truth table for the CAM 48                                                                                                                     |

| 6.7          | Data latency, assuming aligned requests 49                                                                                                     |

| 6.8          | Data latency, assuming unaligned requests                                                                                                      |

| 6.9          | Minimum guaranteed net bandwidth                                                                                                               |

| 7.1          | Notation                                                                                                                                       |

| 7.2          | Symbols of the data flow model of the memory controller                                                                                        |

|              | ° °                                                                                                                                            |

| 8.1          | Request information                                                                                                                            |

| 8.2          | Write data                                                                                                                                     |

| 8.3          | Response information                                                                                                                           |

| 8.4          | Read data                                                                                                                                      |

| 8.5          | Amount of buffering for write requests                                                                                                         |

| 9.1          | Service requirements of the use case                                                                                                           |

| 9.2          | Memory and back-end configuration                                                                                                              |

| 9.3          | Service requirements expressed in resource accesses                                                                                            |

| 9.4          | Front-end configuration for the video application                                                                                              |

| 9.5          | Guaranteed maximum latency (only predictable)                                                                                                  |

| 9.6          | Guaranteed maximum latency (composable mode)                                                                                                   |

| 9.7          | Maximum latency during simulation                                                                                                              |

| 9.8          | Average latency during simulation                                                                                                              |

| 9.9          | Maximum filling of response info buffer                                                                                                        |

| 9.10         | Maximum filling of buffers for composability                                                                                                   |

| 9.11         | Size of the response delay block                                                                                                               |

| A.1          | Command timing constraints                                                                                                                     |

| B.1          | DDR2-400 8/4/1 patterns                                                                                                                        |

| B.2          | DDR2-800 8/4/1  patterns                                                                                                                       |

| B.3          | DDR3-800 $8/4/2$ patterns                                                                                                                      |

| B.4          | DDR3-1600 $8/2/1$ patterns $\dots \dots \dots$ |

| B.5          | Symbols for the patterns                                                                                                                       |

| C.1          | Read and write requests                                                                                                                        |

| C.1<br>C.2   | Read and write requests                                                                                                                        |

| $\bigcirc.2$ | 11 = 11 = 11 = 11 = 11 = 11 = 11 = 11                                                                                                          |

# List of Terms

| AHB     | Advanced High-speed Bus                                   |

|---------|-----------------------------------------------------------|

| AMBA    | Advanced Microcontroller Bus Architecture                 |

| ΑΧΙ     | Advanced eXtensible Interface                             |

| CCSP    | Credit-Controller Static-Priority                         |

| CoMPSoC | Composable and Predictable Multi-Processor System on Chip |

| САМ     | Composable memory access to pattern map                   |

| CPU     | Central Procession Unit                                   |

| DDR     | Double Data Rate                                          |

| DDR2    | Double Data Rate 2                                        |

| DDR3    | Double Data Rate 3                                        |

| DMA     | Direct Memory Access                                      |

| DPRAM   | Dual Port RAM                                             |

| DTL     | Device Transaction Level                                  |

| FIFO    | First In First Out                                        |

| HD      | High Definition                                           |

| IP      | Intellectual Property                                     |

| LCD     | Liquid Crystal Display                                    |

| LPDDR   | Low Power Double Data Rate                                |

| NoC     | Network on Chip                                           |

| PAM     | Predictable memory access to pattern map                  |

| QoS     | Quality of Service                                        |

| RAM     | Random Access Memory                                      |

| SDRAM   | Synchronous Dynamic RAM                                   |

| SoC     | System on Chip                                            |

| TDM     | Time Division Multiplexing                                |

| VHDL    | Very high speed integrated Hardware Description Language  |

|         |                                                           |

# Acknowledgements

This thesis is the result of a project offered by NXP Semiconductors in cooperation with Delft University of Technology. First of all, I want to thank NXP Semiconductors for offering me the possibility to do an internship and performing research on this very interesting topic. Initially, I was working at IP & Architecture group of the department Corporate I&T. I would like to thank Ad Siereveld for helping me to understand the architecture and various issues of memory controllers. Later on, I moved to the SoC Architectures and Infrastructure (SAI) group of the Research department.

Both groups are located at the High Tech Campus in Eindhoven, The Netherlands. I liked doing my thesis in such an industrial environment, because it resulted in a practical project. Besides that, I learned a lot from all the people around me sharing their knowledge.

For supervising my activities and results I would like to thank Kees Goossens. During my internship I worked together with Benny Akesson who is doing a PhD at NXP Semiconductors about predictability and composability in external memory storage services. He helped me a lot with the analysis and concepts of my project.

Eelke Strooisma Delft, The Netherlands May 27, 2008

# 1

# 1.1 Problem description

Due to the miniaturisation of transistors, complete systems are implemented on a single chip. Such chips are called System on Chip (SoC). SoCs consist of numerous Intellectual Property (IP) components. Compared to a system composed of several chips this has the advantage that it has higher performance and lower power consumption, because the distance between the IP components is shorter. Also the production is cheaper, since only one package has to be made.

The miniaturisation of transistors reduces the cost and allows the implementation of more and more functionality by a SoC. The drawback is that complexity of the contemporary SoCs is very high, and is probably getting higher in the future. When the same development methods are used, the time to develop such systems will increase. While time-to-market is getting more and more important, improvement of the development methods is critical.

The effort of design, integration and verification of the IP components of a SoC rapidly increases for larger components [1]. A way to reduce the size of the components, and therefore decreasing the complexity, is to make a hierarchy of components. Another method to decrease development time is to avoid as much design and verification as possible. The key is to create more universal components that can be reused for new applications. Most systems use common components like processors, audio/video decoders and memory. Reusable components that already have been designed and verified save a lot of time, thereby increasing design productivity [1]. Only new features of a SoC have to be developed, and ideally the rest can be dragged and dropped into the design. This idea is supported by the fact that new systems are often an improved version of an older system.

The first drawback is that the cost of universal components (like performance, power consumption and chip area) is always higher than that of specialized ones. Secondly, it is not easy to create and integrate such reusable components. Almost all of the SoCs have specific timing requirements. For these systems, the integration of components to form the system is difficult, because the timing can depend on the other components. For universal components this is even a bigger problem. At the time that they are being created, the environment is unknown. Structured methods for the design of IP components are developed to solve this problem.

## 1.2 Goal

At the SAI group of NXP Research, a platform template called CoMPSoC is being defined and developed to reduce the development effort of SoCs from an architectural point of view [8]. CoMPSoC is a template for a SoC containing different kinds of IP components, resources and multiple processors, all connected by a Network on Chip (NoC). Currently, the focus is on predictable and composable design methodologies. They have the purpose to ease integration and verification of the IP components. Often, external memories shared by multiple IP components are used to reduce the cost. External memories offer high bandwidth and capacity at a low cost per pin. A memory controller is required to communicate with an external memory. The current prototype implementation of the platform template does not have a controller for external memory. The main goal of the graduation project is to create a memory controller that fits into the platform template and composability and composability. The memory controller also has to be universal such that it can be reused more easily. An important aspect of the design and implementation process is to investigate the additional cost caused by the predictability and composability requirements.

# 1.3 Context

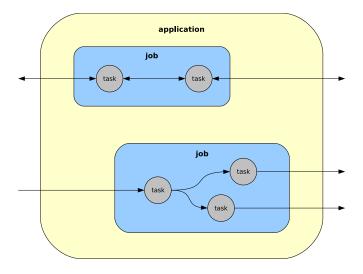

A SoC is used to run one or more applications. An application consist of a number of jobs that are started and stopped to perform different functions. The jobs are dedicated to a specific function and have no direct relation with other jobs. The tasks of a job perform the actual work. Tasks have dependencies between each other. Figure 1.1 shows this application model. The model only describes how the application should work and how the jobs and tasks are related. In what way the model is mapped to hardware and software depends on the constraints of the application. Common constraints are performance, power consumption and time-to-market.

Figure 1.1: Application, jobs and tasks

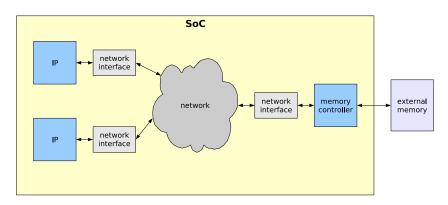

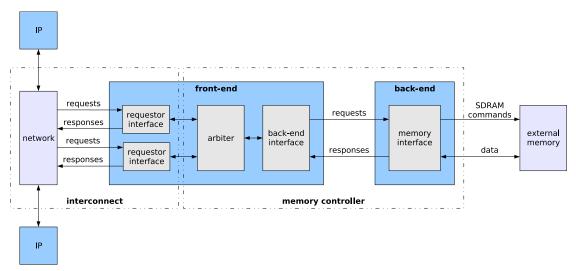

Jobs that are independent have their own memory space. In an implementation, such jobs could have separate memories. To reduce the cost in terms of price, area, input and output pins, often an external memory is used, as mentioned earlier. Figure 1.2 shows an example of a SoC architecture that uses external memory. The application with its jobs and tasks are mapped to the IP components. This architecture uses a NoC as interconnect. All IP components are connected to the NoC by means of network interfaces. Note that the memory controller is also an IP component. This infrastructure allows the IP components to communicate with the memory controller, and indirectly the memory. The memory controller forms the bridge between the IP components and the external memory. The IP components that send requests to the memory controller are called initiators. The memory is the target that responds to the request.

Figure 1.2: Memory controller inside a SoC

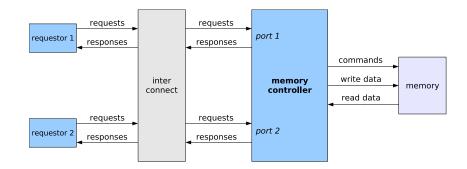

A more abstract representation of the environment of the memory controller is illustrated in Figure 1.3. The memory controller can handle requests and responses of multiple requestors to allow memory sharing. The requestors can use any kind of interconnect to communicate with the memory controller as long as that interconnect can provide the right interface for the ports of the memory controller. To access the memory, a requestor sends requests to its corresponding port at the memory controller. There are two types of requests for a memory: read and write request. A read request instructs the memory controller to get data from the memory. The read data is sent back as part of the response. When a requestor wants to write data to the memory, it issues a write request including the data. The response contains the result of the write request. An IP components that access the memory are called requestors. In practice this could be components like Direct Memory Access (DMA) controllers and processors. It is possible that a single IP component is connected to multiple ports. In this case the IP component corresponds to multiple requestors. Multiple IP components can be aggregated on one port, but they are regarded as a single requestor.

## 1.4 Structure

This thesis is intended to present the activities, design process, issues and results, such that it can be used to continue the work on the composable and predictable SoC. From the problem and goals, the requirements to build the memory controller are derived in Section 2. Section 3 discusses related research on the field of memory controllers, predictability and composability. Information about SDRAM is given in Section 4 to provide more understanding of the issues in the memory controller caused by the memory. The

Figure 1.3: Abstract interface of a memory controller

basic functionality of memory controllers is explained in Section 5. Section 6 introduces and defines the memory command patterns, which are used to get a predictable and composable memory controller. At this point, there is enough background information to explain the design. Given the requirements, the design is proposed in Section 7. This design is implemented using VHDL, such that it can be synthesized. Section 8 discusses the architecture of the hardware implementation in detail. Using that implementation several experiments are done to verify and analyse the behaviour. The results of these experiments are shown and discussed in Section 9. Also synthesis results are presented in this section. Section 10 summarizes important aspects of the integration and verification problem and the proposed solution and implementation. Finally, Section 11 presents future work that could improve the proposed memory controller, or lead to better solutions. The remainder of the report consists of appendices which can be used as reference for details of the project. As discussed in Section 1, a major problem of current SoC development is the complexity of integration and verification. The goal is to design a memory controller that fits in a predictable and composable SoC architecture. This section introduces and motivates the requirements for such a memory controller. Section 2.1 explains what predictable and composable components are and why they simplify integration and verification of IP components. Section 2.2 discusses the secondary requirements, which have the objective to get a usable memory controller.

# 2.1 Verifiable

Verification of a system is the task of checking if the design is actually implementing the intended behaviour. One of the most difficult tasks of verification is to check if the real-time requirements are satisfied.

## 2.1.1 Verification of real-time systems

Systems with explicit timing requirements are called real-time systems. Besides correct functional behaviour, such systems have to guarantee timing behaviour to a certain extent. The system may not behave correctly or may even cause harm when the timing is violated.

Two categories of real-time requirements exists: hard and soft real-time requirements. Hard real-time requirements contain deadlines which may never be missed. Missing these deadlines results in a system that could cause harm or is useless. The property of soft real-time requirements is that missing a small number of soft deadlines does not result in an unusable system. To what extend misses may occur depends on the application.

Applications on a personal computer like a word processor do not have timing constraints. The time between typing and displaying the text on the screen is not bounded. The computer tries to make the delay as short as possible (best effort), but it may take a long time when the system is very busy. This is probably irritating for the user, but it does not affect the functionality. The timing behaviour for SoCs that are applied in embedded systems is often much more critical. An example of an application with hard real-time requirements is the ignition system for engines. It has strict timing bounds for certain actions (i.e. the time to ignite) to guarantee that the engine runs smoothly and is not damaged. Video or audio decoders often have soft real-time requirements. Deadline misses typically result in some distortion in the image or sound. A manufacturer of professional recording equipment has a lower tolerance of such effects than when the chip is used by a television for home use.

#### 2.1.1.1 Dependencies

A dependency exists between two tasks when the behaviour of one task could be affected by the second task. Verification of a task in isolation is not possible when there are dependencies. Tasks with a lot of dependencies are hard to verify because all dependencies must be part of the verification process.

During the integration process, IP components are connected to each other and therefore (new) dependencies are created between tasks. At the time all dependencies exist, real-time requirements can be verified. A violated requirement could be fixed by reconfiguring or using a different IP component to execute the task for example. However, all dependent tasks have to be verified again because their timing behaviour may have been changed, possibly resulting in new violations.

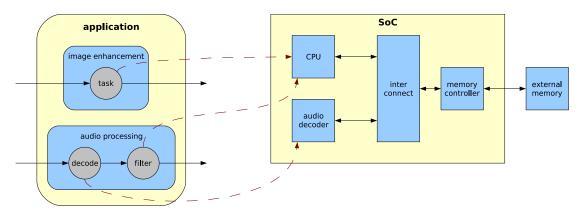

To illustrate how dependencies are created and how they affect verification, consider the fictive application in Figure 2.1. The application has a job for image enhancement and one that processes an audio stream. The audio processing job consists of a task that decodes an audio stream and a task that applies some filter. The filter is dependent on the decoding task, since that one provides the input for the filter. Dependencies in the application model are called *explicit*.

Figure 2.1: Mapping of an application to a SoC

As mentioned in Section 1.3, an application with its tasks and jobs is mapped to hardware and software. Often, there is no one to one relation between jobs, tasks and the IP components of a SoC. It could be the case that a task needs multiple IP components and multiple tasks share the same IP component. Figure 2.1 shows how the application is mapped to a SoC. The dashed arrows indicate which IP components execute the tasks. The CPU is used to execute the task of the image enhancement job, but also for filtering the audio stream. The external memory is used as input and output of the image and audio stream. Three shared resources can be identified: the CPU, interconnect and the memory. Due to the mapping, all introduce additional dependencies. First, the CPU has to execute tasks of different jobs, which do not have a dependency in the application model. Secondly, the memory and interconnect are shared by the CPU as well as the audio decoder. These dependencies are called *implicit*.

Some applications allow starting and stopping jobs at run-time. This causes depen-

dencies to change at run-time. Assume that a third job is started at run time, which contains a task that must be executed by the CPU. Now there exists implicit dependencies between all three jobs of the application. To determine the timing behaviour of a single job, all three jobs have to be analysed.

Like the example, the requestors of a shared memory (or any other shared resource) usually do not belong to a single job. The service that a requestor receives depends on the behaviour of other requestors and therefore causes implicit dependencies. When one requestor needs less service than allocated, the other requestors can get more.

#### 2.1.1.2 Timing analysis

To check if all real-time requirements are satisfied, the timing behaviour must be analysed. In general, there are two methods for timing analysis: