## **MSc THESIS**

## Front-end for Composable Resource Sharing Using Latency-Rate Servers

Getachew Teshome Woldegebreal

In this thesis, the design and implementation of an efficient front-end for composable resource sharing is presented. With composable resource sharing, every application obtains a service that is not affected by interference from other applications that share the same resource. Since applications are shielded from interference, each one of them can be verified by simulation independently and integrated without reverification. This reduces the verification effort that would, otherwise, be tremendous.

Abstract

Our solution is based of Latency-rate  $(\mathcal{LR})$  servers, which are used to model service provided by a predictable resource. The front-end provides composable resource sharing when attached to a predictable resource. A series of tests have been carried out to verify that the front-end isolates applications from each other while sharing a resource.

The design has been synthesized for FPGA as well as ASIC on CMOS 90nm technology to estimate area and operating frequency.

CE-MS-2009-22

### Front-end for Composable Resource Sharing Using Latency-Rate Servers

#### THESIS

submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

$\mathrm{in}$

#### COMPUTER ENGINEERING

by

Getachew Teshome Woldegebreal born in Motta, Ethiopia

Computer Engineering Department of Electrical Engineering Faculty of Electrical Engineering, Mathematics and Computer Science Delft University of Technology

#### by Getachew Teshome Woldegebreal

#### Abstract

I n this thesis, the design and implementation of an efficient front-end for composable resource sharing is presented. With composable resource sharing, every application obtains a service that is not affected by interference from other applications that share the same resource. Since applications are shielded from interference, each one of them can be verified by simulation independently and integrated without reverification. This reduces the verification effort that would, otherwise, be tremendous.

Our solution is based of Latency-rate  $(\mathcal{LR})$  servers, which are used to model service provided by a predictable resource. The front-end provides composable resource sharing when attached to a predictable resource. A series of tests have been carried out to verify that the front-end isolates applications from each other while sharing a resource.

The design has been synthesized for FPGA as well as ASIC 90nm technology to estimate area and operating frequency.

| Laboratory<br>Codenumber | :<br>: | Computer Engineering<br>CE-MS-2009-22                 |

|--------------------------|--------|-------------------------------------------------------|

| Committee Members        | :      |                                                       |

| Advisor:                 |        | Prof. Kees Gooossens, CE, TU Delft                    |

| Advisor:                 |        | Benny Akesson, ES/ICS, TU Eindhoven                   |

| Member:                  |        | Prof. Kees Goossens, CE, TU Delft; NXP Semiconductors |

| Member:                  |        | Prof. A. Van Der Veen, CAS, TU Delft                  |

| Member:                  |        | Dr. Sorin Cotofana, CE, TU Delft                      |

I dedicate this thesis to my beloved parents, my dad Ato Teshome and my mom W/ro Mitikie. They always devote themselves for the success of their children, usually giving more than what they afford.

## Contents

| List of Figures    | х    |

|--------------------|------|

| List of Tables     | xi   |

| List of Algorithms | xiii |

| Acknowledgements   | xv   |

| 1        | I Introduction |                                           |                                              |                            |  |

|----------|----------------|-------------------------------------------|----------------------------------------------|----------------------------|--|

|          | 1.1            | Trend                                     | s in Embedded Systems                        | 1                          |  |

|          |                | 1.1.1                                     | Embedded System Market                       | 1                          |  |

|          |                | 1.1.2                                     | Multiple functions per device                | 1                          |  |

|          |                | 1.1.3                                     | Real-time requirements                       | 2                          |  |

|          |                | 1.1.4                                     | Modular IP Design and IP Reuse               | 2                          |  |

|          |                | 1.1.5                                     | Resource Sharing                             | 3                          |  |

|          | 1.2            | Proble                                    | em Statement                                 | 3                          |  |

|          | 1.3            | Conte                                     | xt                                           | 4                          |  |

|          | 1.4            | Requi                                     | rements                                      | 7                          |  |

|          |                | 1.4.1                                     | Composability                                | 7                          |  |

|          |                | 1.4.2                                     | Programmability                              | 7                          |  |

|          |                | 1.4.3                                     | Modular Design                               | 7                          |  |

|          | 1.5            | Contr                                     | ibutions                                     | 8                          |  |

|          | 1.6            | Organ                                     | nization of The Thesis                       | 8                          |  |

| <b>2</b> | $\mathbf{Rel}$ | ated V                                    | Vorks                                        | 9                          |  |

| 3        | Pro            | posed                                     | Solution                                     | 11                         |  |

|          | 3.1            | -                                         |                                              | 11                         |  |

|          | 3.2            |                                           |                                              | 14                         |  |

| 4        | $\mathbf{Des}$ | ign                                       |                                              | 17                         |  |

| -        | 4.1            | 0                                         |                                              |                            |  |

|          |                | Atomi                                     | zer                                          | 17                         |  |

|          |                | Atomi 4.1.1                               |                                              | $17 \\ 17$                 |  |

|          |                |                                           | Functions of the Atomizer                    | 17                         |  |

|          |                | 4.1.1<br>4.1.2                            | Functions of the Atomizer       Architecture | 17<br>19                   |  |

|          | 4.2            | 4.1.1<br>4.1.2<br>Delay                   | Functions of the Atomizer                    | 17<br>19<br>20             |  |

|          |                | 4.1.1<br>4.1.2                            | Functions of the Atomizer                    | 17<br>19                   |  |

|          |                | 4.1.1<br>4.1.2<br>Delay<br>4.2.1          | Functions of the Atomizer                    | 17<br>19<br>20<br>20<br>21 |  |

|          |                | 4.1.1<br>4.1.2<br>Delay<br>4.2.1<br>4.2.2 | Functions of the Atomizer                    | 17<br>19<br>20<br>20       |  |

|          | 4.3                    | Arbite            | r                                                | 25               |  |  |  |  |

|----------|------------------------|-------------------|--------------------------------------------------|------------------|--|--|--|--|

|          |                        | 4.3.1             | CCSP Parameters                                  | 25               |  |  |  |  |

|          |                        | 4.3.2             | Mechanism                                        | 25               |  |  |  |  |

|          |                        | 4.3.3             | Architecture                                     | 26               |  |  |  |  |

|          | 4.4                    | Resour            | rce Sharing Bus                                  | 28               |  |  |  |  |

|          |                        | 4.4.1             | Timer                                            | 28               |  |  |  |  |

|          |                        | 4.4.2             | Request Multiplexer and Response Demultiplexer   | 29               |  |  |  |  |

|          | 4.5                    | Config            | ration                                           | 30               |  |  |  |  |

|          |                        | 4.5.1             | Front-end Feature Selection                      | 30               |  |  |  |  |

|          |                        | 4.5.2             | Design Time Configuration (Block Customization): | 30               |  |  |  |  |

|          |                        | 4.5.3             | Run-time Configuration                           | 31               |  |  |  |  |

| <b>5</b> | Imr                    | lemen             | tation                                           | 33               |  |  |  |  |

| 0        | 5.1                    |                   | inaries                                          | 33               |  |  |  |  |

|          | 0.1                    | 5.1.1             | Communication Protocol                           | 33               |  |  |  |  |

|          |                        | 5.1.2             | Representation of Time                           | 35               |  |  |  |  |

|          | 5.2                    |                   | onal Blocks                                      | 37               |  |  |  |  |

|          | 0.2                    | 5.2.1             | Atomizer                                         | 37               |  |  |  |  |

|          |                        | 5.2.1             | Delay Block                                      | 39               |  |  |  |  |

|          |                        | 5.2.2             | CCSP Arbiter                                     | 49               |  |  |  |  |

|          |                        | 5.2.3<br>5.2.4    | Resource Sharing Bus                             | 4 <i>3</i><br>51 |  |  |  |  |

|          | 5.3                    |                   | puration                                         | 55               |  |  |  |  |

|          | 0.0                    | 5.3.1             | Feature Selection                                | 55               |  |  |  |  |

|          |                        | 5.3.1             | Design Time Configuration                        | 55               |  |  |  |  |

|          |                        | 5.3.2             | Run Time Configuration                           | 57               |  |  |  |  |

|          | 5.4                    |                   | a Flow and Automation                            | 60               |  |  |  |  |

|          | 0.4                    | 5.4.1             | Architecture Specification                       | 60               |  |  |  |  |

|          |                        |                   | •                                                |                  |  |  |  |  |

|          |                        | 5.4.2             | Specification of Communication Requirements      | 60               |  |  |  |  |

| 6        | $\mathbf{E}\mathbf{x}$ | perime            | ents and Results                                 | 63               |  |  |  |  |

|          | 6.1                    | Simula            | ation                                            | 63               |  |  |  |  |

|          |                        | 6.1.1             | Testbench                                        | 63               |  |  |  |  |

|          |                        | 6.1.2             | Use Case                                         | 64               |  |  |  |  |

|          |                        | 6.1.3             | Predictability Test                              | 65               |  |  |  |  |

|          |                        | 6.1.4             | Composability Test                               | 66               |  |  |  |  |

|          |                        | 6.1.5             | Impact on Performance                            | 73               |  |  |  |  |

|          | 6.2                    | Test of           | n FPGA                                           | 74               |  |  |  |  |

| 7        | Syn                    | nthesis Results 7 |                                                  |                  |  |  |  |  |

|          | 7.1                    |                   | esis FPGA                                        | 77               |  |  |  |  |

|          |                        | 7.1.1             | Atomizer                                         | 77               |  |  |  |  |

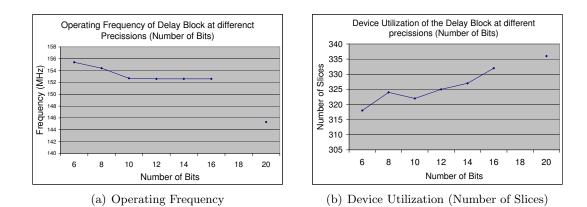

|          |                        | 7.1.2             | Delay Block                                      | 77               |  |  |  |  |

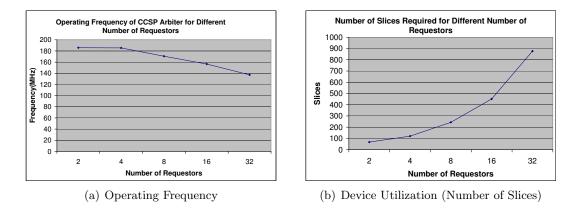

|          |                        | 7.1.3             | CCSP Arbiter                                     | 79               |  |  |  |  |

|          |                        | 7.1.4             | Resource Sharing Bus                             | 80               |  |  |  |  |

|          | 72                     | Synthe            | osis ASIC                                        | 81               |  |  |  |  |

|    | 7.2.1        | Synthesis Results for Atomizer             | 82 |

|----|--------------|--------------------------------------------|----|

|    | 7.2.2        | Synthesis Results for Delay Block          | 82 |

|    | 7.2.3        | Synthesis Results for CCSP Arbiter         | 83 |

|    | 7.2.4        | Synthesis Results for Resource Sharing Bus | 85 |

| 8  | Conclusio    | ns                                         | 87 |

| 9  | Future wo    | ork                                        | 89 |

| A  | Specificati  | ion in the Æthereal Design Flow            | 91 |

|    | A.1 Archit   | secture Specification                      | 91 |

|    | A.2 Specif   | ication of Communication Requirements      | 93 |

| Bi | Bibliography |                                            | 96 |

|    |              |                                            |    |

# List of Figures

| $1.1 \\ 1.2$ | Components of a Transaction and Flow-Control            | $\frac{4}{5}$ |

|--------------|---------------------------------------------------------|---------------|

| 1.2 1.3      | A System-on-Chip                                        | 6             |

| 1.4          | Mapping of an Application on to an SOC                  | 6             |

| 1.4          |                                                         | 0             |

| 3.1          | Paths of Interference During Resource Sharing           | 11            |

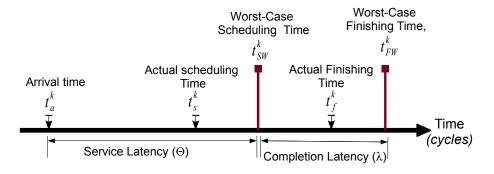

| 3.2          | Timing of Events in the Resource Sharing Front-end      | 12            |

| 3.3          | Service Curve with latency-rate $(\mathcal{LR})$ model  | 13            |

| 3.4          | The Proposed Resource Sharing Front-end.                | 14            |

| 4.1          | Requests Chopped by the Atomizer                        | 18            |

| 4.2          | Merging of Responses in the Atomizer                    | 19            |

| 4.3          | Architecture of the Atomizer                            | 19            |

| 4.4          | Delay Processes in the Response and flow-control Paths. | 20            |

| 4.5          | Important Events in serving a request                   | 21            |

| 4.6          | Generation of flow-control signal (a),(b)               | 23            |

| 4.7          | Architecture of the Delay Block                         | 24            |

| 4.8          | Architecture of CCSP Arbiter                            | 26            |

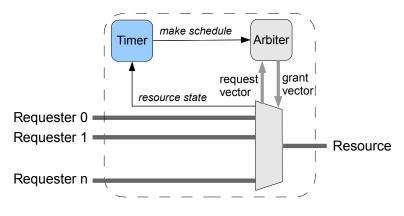

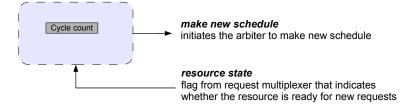

| 4.9          | Architecture of Resource Sharing Bus                    | 28            |

| 4.10         | Service Timer                                           | 28            |

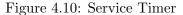

| 4.11         | Multiplexing Requests and Demultiplexing Responses      | 29            |

| 4.12         | Configuration Infrastructure                            | 32            |

| 5.1          | Direction and Grouping of DTL Signals                   | 35            |

| 5.2          | MOD-2M Circular Counter, where $M=2^N$                  | 36            |

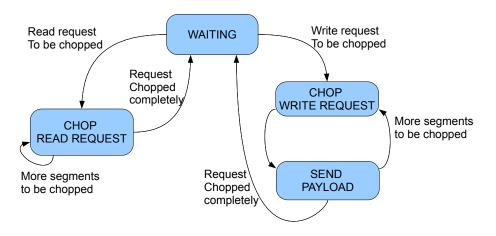

| 5.3          | FSM for Chopping Requests                               | 38            |

| 5.4          | Accumulation of Error due to Approximation of $\lambda$ | 39            |

| 5.5          | Request Buffer (a),(b)                                  | 41            |

| 5.6          | FSM for Receiving and Validating Requests               | 43            |

| 5.7          | Validating Arrival of Requests in the Delay Block       | 44            |

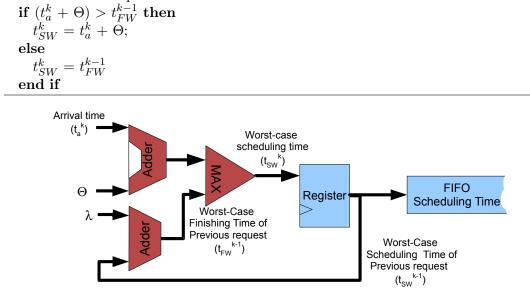

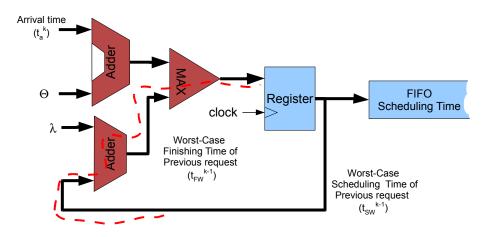

| 5.8          | Computation of Worst-Case Scheduling Time               | 45            |

| 5.9          | Computation of Worst-Case Finishing Time                | 46            |

| 5.10         | Counters in the Delay Block and Their Management        | 48            |

| 5.11         |                                                         |               |

| 5.12         | FSM for multiplexing requests                           | 53            |

| 5.13         | An Example Instance of The Front-end                    | 55            |

| 5.14         | Address Mapping for Configuration of the Delay Block    | 58            |

| 5.15         | Mapping of Configuration Data to CCSP Parameters        | 59            |

| 6.1          | Testbench For The Resource Sharing Front-end            | 63            |

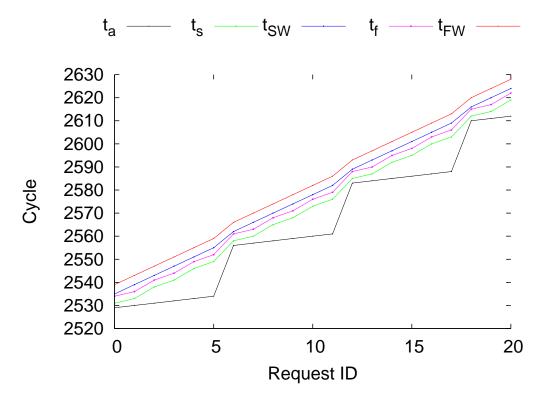

| 6.2          | Timing of Events                                        | 66            |

| 6.3          | Timing of Events for Each Requestor                     | 69            |

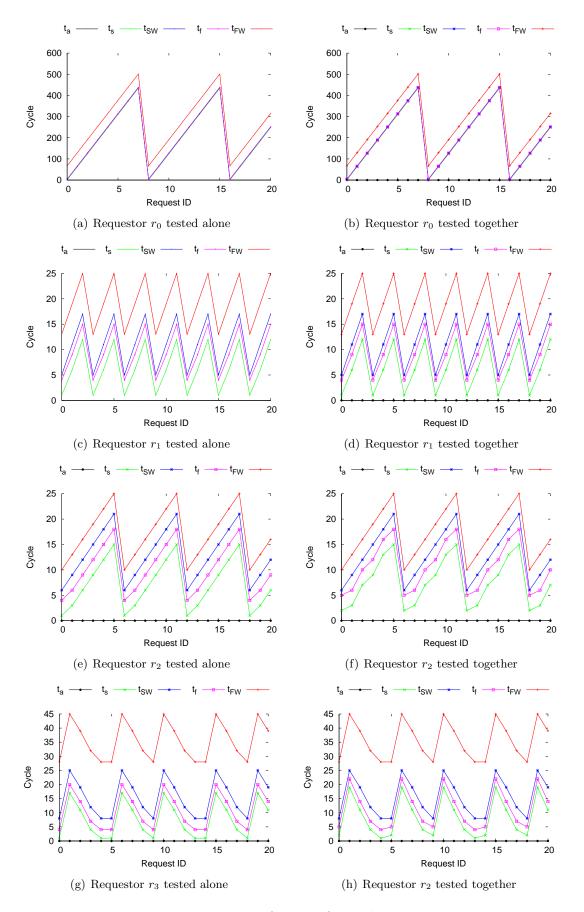

| 6.4          | Comparison                                              | 70            |

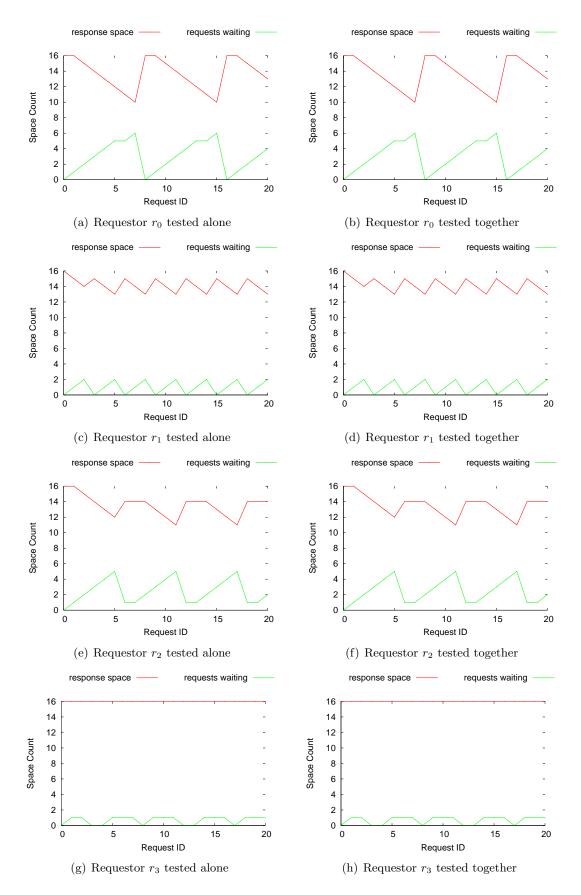

| 6.5  | Buffer State of Requestors                                                                        | 72 |

|------|---------------------------------------------------------------------------------------------------|----|

| 6.6  | System on FPGA To Test The Resource Sharing Front-end                                             | 74 |

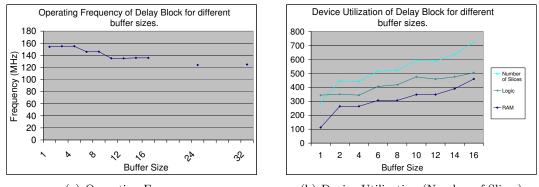

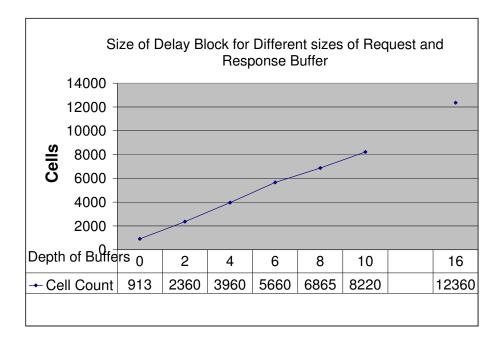

| 7.1  | Synthesis Result for The Delay Block - for different buffer sizes                                 | 78 |

| 7.2  | The Critical Path in the Delay Block                                                              | 78 |

| 7.3  | Synthesis Result for The Delay Block - for Different Precisions                                   | 78 |

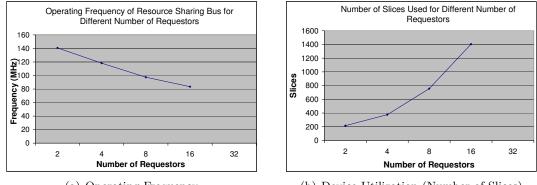

| 7.4  | Synthesis Result for the CCSP Arbiter - for Different Number of Re-                               |    |

|      | questors (a),(b) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 79 |

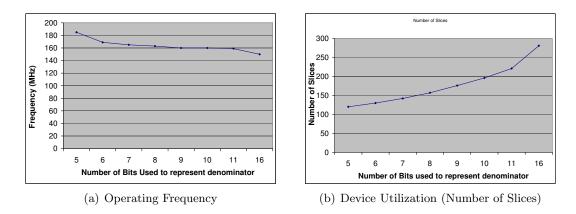

| 7.5  | Synthesis Result for CCSP Arbiter - for Different Precisions (a),(b)                              | 80 |

| 7.6  | Synthesis Result for The Resource Sharing Bus                                                     | 80 |

| 7.7  | The Critical Path in the CCSP Arbiter and the Resource Sharing Bus                                | 81 |

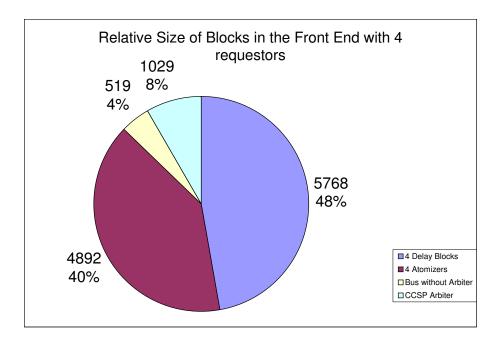

| 7.8  | Relative Size of Units in the Front-end                                                           | 82 |

| 7.9  | Size of the Delay Block as a Function of Buffer Size                                              | 83 |

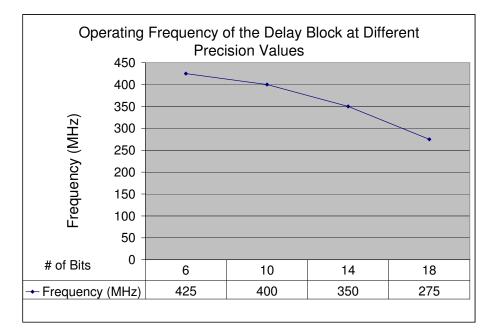

| 7.10 | Operating Frequency of the Delay Block for Different Precision Values                             | 83 |

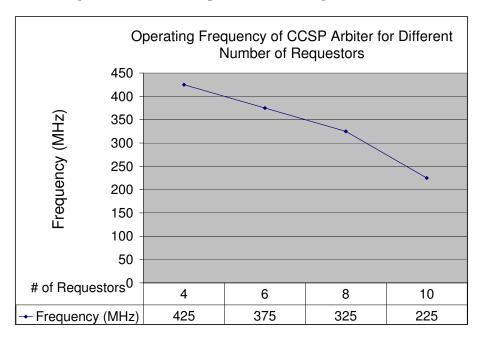

| 7.11 | Operating Frequency of the CCSP Arbiter for Different Number of Re-                               |    |

|      | questors                                                                                          | 84 |

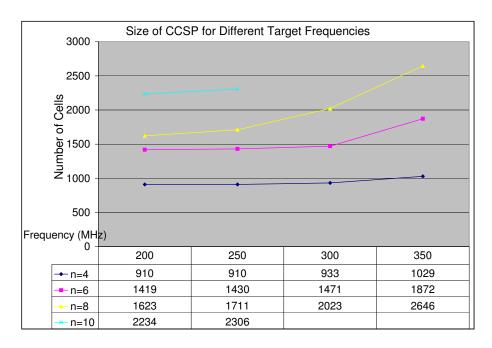

| 7.12 | Size of the CCSP Arbiter for Different Number of Requestors                                       | 85 |

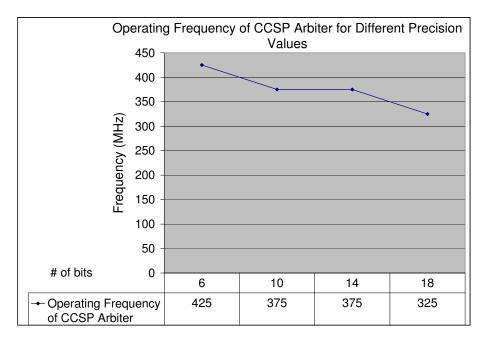

| 7.13 | Operating Frequency of the CCSP Arbiter for Different Precision Values .                          | 85 |

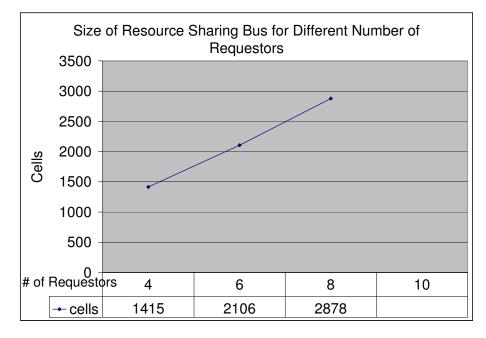

| 7.14 | Size of the Resource Sharing Bus for Different Number of Requestors                               | 86 |

## List of Tables

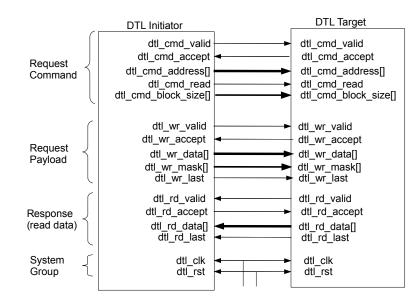

| 5.1 | Definition of Relevant Signals in the DTL Protocol                            | 34 |

|-----|-------------------------------------------------------------------------------|----|

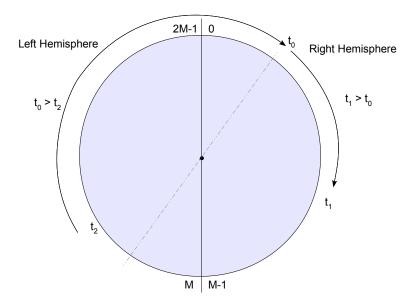

| 5.2 | Comparison of Two Time Values $x$ and $y$ based on their difference $(x-y)$ . | 37 |

| 5.3 | Identifying the sub range for $(x-y)$                                         | 37 |

| 6.1 | Time Stamp for Requests From Core 0                                           | 64 |

| 6.2 | Service requirements of the four requestors in the use case                   | 65 |

| 6.3 | Service requirements of the four requestors and configuration parameters .    | 65 |

| 6.4 | Configuration Values for the Front-end                                        | 65 |

| 6.5 | Comparison of Service offered to requestors - Isolated Vs. Composed           | 68 |

| 6.6 | Impact of the Resource Sharing Front-end on Performance                       | 73 |

| 6.7 | Service requirements of the three requestors                                  | 74 |

| 6.8 | Service requirements of the three requestors in resource accesses             |    |

| 6.9 | Configuration Values for the Front-end                                        | 75 |

# List of Algorithms

| 4.1  | Eligibility Check in the CCSP Arbiter                | 26 |

|------|------------------------------------------------------|----|

| 4.2  | Static-Priority Scheduling in the CCSP Arbiter       | 27 |

| 4.3  | Budget Management in the CCSP Arbiter                | 27 |

| 5.1  | Merging Responses in the Atomizer                    | 38 |

| 5.2  | Validating Arrival of a Request in the Delay Block   | 44 |

| 5.3  | Compute Worst-case Scheduling Time for a Request     | 45 |

| 5.4  | Compute Worst-case Finishing Time for a Request      | 45 |

| 5.5  | Operations During a Scheduling Event                 | 47 |

| 5.6  | Check Eligibility of Requestors in the CCSP Arbiter  | 50 |

| 5.7  | Priority Relationship Among requestors               | 51 |

| 5.8  | Static-Priority Scheduling in the CCSP Arbiter       | 52 |

| 5.9  | Credit Management in the CCSP Arbiter                | 52 |

| 5.10 | Service Timer in the Resource Sharing Bus            | 53 |

| 5.11 | Demultiplexing Responses in the Resource Sharing Bus | 54 |

| 5.12 | Configuration of CCSP Parameters                     | 59 |

|      |                                                      |    |

## Acknowledgements

This thesis is the result of a project done at NXP Semiconductors, High Tech Campus in Eindhoven, under the supervision of Prof. Kees Goossens. I would like to thank Prof. Kees for offering me the opportunity to work on such an interesting project in a very conducive working environment. I had the privilege of getting his wonderful supervision regularly throughout the course of the project. It would be unfair to mention Benny Akesson just as a great supervisor. He was also like an elder brother who shows his youngest a new road everyday. I can't thank him enough.

All this wouldn't have been possible without the support that I got from Nuffic (Netherlands Organization for International Cooperation in Higher Education) to pursue my study at Delft University of Technology; I am very grateful. I am also grateful to Addis Ababa University (in Ethiopia) for the support and arrangement of my stay in the Netherlands.

Last but not least, my beloved family and friends had never been further than a phone call away. Their encouragement and advice is the single thing that kept me upright even at moments of my weakness.

Thank you God for giving me everything I needed to reach this point.

Getachew Teshome Woldegebreal Delft, The Netherlands August 26, 2009

1

Time after time, embedded systems are increasing their presence in our daily life. From mobile phones to aviation, kitchen appliances to medical equipments and toy cars to space shuttles, we depend upon embedded systems to lead our daily life properly. Their application areas range from simple consumer applications to safety critical applications, in which malfunctioning may result in severe consequences, such as loss of life. To prevent mishaps from happening, devices are vigorously tested before putting them to actual use. As verification is part of the design cycle, it increases the time-to-market and introduces more expenses. Embedded systems in mission critical application domains enjoy the luxury of a huge budget to spend on testing and longer design cycle. In consumer electronics, in contrast, reducing time-to-market and design cost is determinant to the success of a product. Some trends in embedded systems design and market, however, tend to increase the complexity of system verification, thereby, raising verification effort, design cost and time-to-market.

We start this chapter by highlighting some trends in System-on-Chip (SoC) that are important to our work in Section 1.1. In section 1.2, statement of the problem is presented. Section 1.3 explains the context in which this work has been done. This introduction section is concluded with Section 1.4, where requirements from the solution are pointed out.

#### 1.1 Trends in Embedded Systems

#### 1.1.1 Embedded System Market

Due to the fast growth of the consumer electronics, the Embedded System market has attracted the attention of many manufacturers. A lot of them compete fiercely to manufacture devices that have good value in the market. This puts a lot of pressure on each manufacturer to be successful. The first key issue is coping with the dynamic market and being able to satisfy user demand that continues to rise day by day [15]. Equally important is a short time-to-market in releasing a product. Shorter time-to-market not only reduces design cost, but also gives the products good price in the market. Thus it is necessary for every manufacturer to reduce the design time of products.

#### 1.1.2 Multiple functions per device

Driven by market convergence [19], between *Telecom*, *Consumer Electronics* and *Computers*, it has become a common practice to incorporate multiple functionalities into a single device. A white paper from the Economist Intelligence Unit [20], mentions iPhone as a successful converged device.

... game-changing iPhone, which neatly combines a mobile phone, handheld computer and a music player in one converged device.

This practice, for one thing, adds more portability to the devices, and then it makes it possible to share some of the device components, such as processors and memories, among different applications thereby reducing the total cost.

In a device with multiple applications, the set of applications that are active changes from time to time. Each envisaged combination of applications that run simultaneously on a device is called a *use-case*. The number of use-cases grows exponentially with the number of applications included in the device. As each use-case must be verified, *the verification complexity also grows exponentially with number of applications*.

#### 1.1.3 Real-time requirements

As new applications continue to enhance the capability of embedded systems, many of them are emerging with different real-time requirements. Based on their real-time requirements, applications are categorized into *Non Real-time* and *Real-time* applications. An application is said to be real-time if the usefulness of operations that comprise it depends not only upon its logical correctness, but also upon the time in which it is performed. In *non real-time* application, on the other hand, timing is not of concern as long as the operations are logically correct.

Real-time Applications are further categorized into *Soft Real-time* and *Hard Real-time*. In hard real-time applications, timing requirements are so strict that an operation is useless, or may even have negative consequences, if it is not completed within the deadline. Missing deadlines in hard real-time systems may lead to failure of the application and, even, damage the surrounding. One example of hard real-time applications is Fly-by-wire flight control, which uses electronic signals to measure a pilots input and to control the aircraft [7]. The flight control *must* receive the pilot's inputs and transmit actuation signals at a predetermined frequency. If it fails to meet the timing requirements, the aircraft can become instable and lead to a crash.

Soft real-time applications also have timing requirements. However, occasional deadline misses are tolerated with impact on the quality of application only. For instance, deadline misses in *Video Decoder* application lead to missing frames in display. But, the consequence is limited to degradation in application quality.

Timing requirements in real-time applications, obviously, add another dimension to system verification. Such systems require verification of timing behavior on top of the trivial functional verification and, hence, lead to higher verification effort.

#### 1.1.4 Modular IP Design and IP Reuse

One of the emerging methodologies in a System-on-chip (SoC) design is combining predesigned and pre-verified blocks - often called intellectual property (IP) blocks - on a chip to increase design productivity [15]. An IP block can be software or hardware component that is obtained from internal sources, or even from external vendors, in reusable form. With this design approach, an SoC is built from small blocks that have well-defined function and approach. The role of an SoC designer is, then, to integrate IP blocks on to a chip to implement a complex function. This design paradigm has benefit for IP vendors as well as users. For IP vendors, it gives the opportunity to design components that can be used by more clients so that the design cost is amortized. IP users, on the other hand, benefit from reduced design cost and short time-to-market.

Although reuse is a viable approach to tackle the unprecedented complexity of current SoCs, the associated verification problem is in some respects harder [15]. As mentioned in the *International Technology Road map for Semiconductors (ITRS)* [8], while design sizes have grown exponentially over time [16], theoretical verification complexity has been growing double exponentially [15]. If the entire SoC were to be tested at once without exploiting the structure of the building blocks, all possible verification states would have to be considered and the complexity would be tremendous. The solution is incremental verification, in which individual cores are verified once in isolation and then the integrated system is verified under the assumption that each core is correct. By doing so, the verification effort for each core is made reusable.

#### 1.1.5 Resource Sharing

A SoC, usually, contains one or more IPs that can be used for multiple applications. In such occasions, sharing resources becomes the economical approach. Memory units and I/O devices are among resources that are often shared. Resource sharing is not, however, without problems. This implicit interaction between applications alters their temporal behaviors. In verifying real-time applications, it is necessary to conform that the interference due to resource sharing does not lead to violation of timing requirements. This, obviously, adds to verification complexity unless a mechanism is put in place to share resources between applications in an interference-free way.

#### 1.2 Problem Statement

Each of the trends discussed in the Section 1.1 relate to the verification effort in SoC design. The market dynamics pushes manufacturers for new products and new features more often than ever. With the remaining trends tending to increase complexity of system verification, it becomes a big challenge to verify all requirements within reasonable time frame and budget. However challenging it might be, system verification is mandatory to ensure reliability of products and hence to sustain in the market.

The objective of this work is reducing system verification effort by removing implicit dependencies between applications that arise due to resource sharing. When applications do not have implicit dependence among them, they can be verified independently and integrated later without requiring re-verification.

Consider a system composed of n applications, with the  $i^{th}$  application having some measure of verification complexity (e.g., number of reachable states, number of functional coverage points) of  $v_i$ . If the integration leads to interference among the applications, it becomes necessary to consider the cross product [15] of all possible verification states.

This results in a verification complexity of

$$\prod_{i=1}^{n} v_i \tag{1.1}$$

which is exponential in n. The goal of this work is a resource sharing mechanism that shields applications from interference from other applications so that individual applications are verified once in isolation and only system-level verification is required after integration. The system-level verification is carried out under the assumption that each application behaves correctly as was verified independently. This leads to a lower overall verification complexity which amounts to

$$v_{sys} + \sum_{i=1}^{n} v_i \tag{1.2}$$

where  $v_{sys}$  represents the system-level verification effort. As can be seen in Equation (1.2), the total verification effort grows only linearly as the number of applications is increased. Another benefit of this design approach is incremental verification. The verification process can be started earlier with the available applications without having to wait for the whole application set.

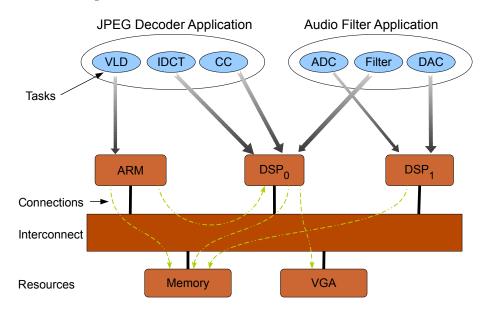

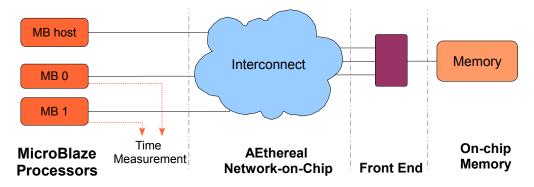

#### 1.3 Context

The context of this thesis is a SoC with multiple IP blocks interconnected with an onchip interconnect. Some of the IPs are processing elements, such as a DSP or general purpose processor while others are resources; such as memory or VGA display that are to be used by applications. Communication between two IPs is carried out via requests and responses. One of the IPs (*the master*) generates request and the other IP (*the slave*) responds by sending back responses. A request contains the command component of a transaction and the data to be written (*payload data*) in case the request is a write operation. Critical elements such as *request address*, *request size* and *request type* are

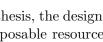

Figure 1.1: Components of a Transaction and Flow-Control

included in the command component. The response sent by the slave can be read data

for read requests or information about the completion of a write operation for write requests. The components of a transaction and the direction of signals involved are shown in Figure 1.1. When a master sends a request, it informs the slave about the validity of the request by setting the *valid* flag high. The slave then acknowledges by setting the *accept* flag high if it is able to accept the request or indicates otherwise if it is unable. Similarly, when the slave returns responses, it sets the *valid* signal in the response path high. The master, then, indicates whether or not it is able to accept the response. These handshakes between two communicating parties represent the flowcontrol mechanism. The DTL protocol, which uses such flow-control mechanism and used in our implementation is discussed in detail in Section 5.1.1.

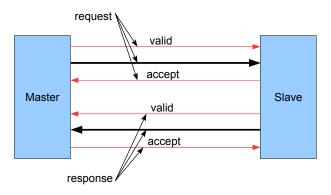

When there are multiple links between the master and the slave, the communication involves link-level flow-control at each hop. Figure 1.2 illustrates the link-level flow-

Figure 1.2: Link-level Flow-Control

control involved as a master and a slave communicate with multiple hops in between.

As the number of IP blocks in a single SoC increases, it becomes difficult, if not impossible, to satisfy the communication needs using ad-hoc means. Interconnect infrastructures such as busses, switches and network on chips (NoCs) provide an elegant communication platform in a SoC [3]. Communicating IPs use the shared infrastructure to send request and responses. A virtual path in the interconnect that is used for communication between a master IP and a slave IP is referred to as a *connection*.

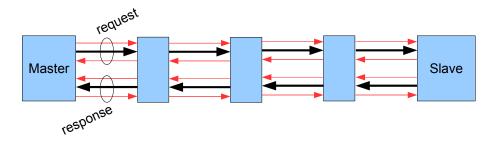

Figure 1.3 illustrates an example SoC with three processing IPS (ARM,  $DSP_0$  and,  $DSP_1$ ) and two resources (*Memory* and VGA). The example also demonstrates that the memory is used by the three processing elements and hence represents a shared resource. When there is a shared resource in the system, a resource sharing front-end is required to arbitrate/ schedule access to the resource and that is the central issue in this thesis.

One or more applications, such as *JPEG decoder* or *Audio Filter* run on the system to bring about the required functionality. When an application is loaded, the tasks that comprise it, such as *color conversion* in JPEG decoder are mapped on to hardware IPs in the system.

Mapping of two applications, a JPEG Decoder Application and an Audio Filter Application, on to the system in Figure 1.3 is presented in Figure 1.4 as an example. The JPEG decoder application is comprised of three tasks [5] - Variable Length DecodingVLD, Inverse Discrete Cosine Transform (IDCT) and Color Conversion (CC). Similarly, the Audio Decoder application has three tasks - Analog-to-Digital Converter (ADC) Filter and Digital-to-Analog Converter (DAC). Communication between tasks of an application

Figure 1.3: A System-on-Chip

is carried out through connections between IP blocks.

Figure 1.4: Mapping of an Application on to an SOC

A connection that terminates at a target port of a resource is referred to as a *requestors*. Each resource has a set of requestors, which correspond to a request path from different IPs. For instance, the Memory port in Figure 1.4 has three requestors that emanate from ARM,  $DSP_0$  and  $DSP_1$ . The focus of this work is the elimination of implicit dependence between applications caused by interference while sharing a resource.

#### 1.4 Requirements

The major requirement in the solution is isolating applications so that they can be verified independently. In addition, the design has to feature state-of-the-art design requirements, such as programmability and modular design. These requirements are briefly discussed next one by one.

#### 1.4.1 Composability

A system is said to be composable if both the functional and temporal behaviors of every application are independent of how other applications behave. In a composable system dependence between applications is eliminated both in time and value domains [2]. This isolation is important because it enables incremental design and reduces complexity of system integration and verification [9]. Composability simplifies the verification process for the following three reasons [2].

- As applications are independent of each other, they can be designed, tested and verified in isolation. This reduces system simulation time and makes the verification process linear and non-circular.

- The verification process can be done incrementally and, can, hence be started even before the complete application set is ready.

- Moreover, composability contributes to IP protection. Since verification of IPs can be done in isolation, before the final integration, vendors do not have to share their IP.

In a situation where a resource is shared, availability of the resource for one application may depend on the behavior of other applications that use the same resource. If an entire system is to be composable, resource sharing also has to be composable.

#### 1.4.2 Programmability

When applications are started and stopped at run time, they create different use-cases. Whenever there is use-case transition, requirements from applications are added to or removed from the system. To effectively satisfy such changing demands, the system has to be flexible. Flexibility is achieved by having some programmable parameters in the system that can be changed at run time.

#### 1.4.3 Modular Design

Instead of realizing a solution as a monolith, building it out of smaller functional modules has benefits. First of all, the modules can be designed and modified independently without affecting other modules. Hence parts of the system can be changed while keeping the rest intact. Another benefit is reusability, which reduces design time and time-tomarket. By creating individual blocks with specific functions, reusability of the design is maximized. To facilitate reusability modules should be created with standard interfaces to connect with other modules.

#### 1.5 Contributions

The result of this thesis is a hardware block *(resource sharing front-end)* that eliminates interference between applications as they share a resource. The following mechanisms have been implemented to realize this function.

- 1. Mechanism to chop transactions into fixed size (Atomizer).

- 2. Mechanism to delay transactions and release them at a predefined time (Delay Block).

- 3. Hardware Implementation of the Credit-Controlled Static-Priority (CCSP) Arbiter [2].

- 4. Representation of time with circular cycle counter and associated mechanism to compare time stamps.

- 5. Synthesis and testing of the resulting hardware for FPGA and ASIC (only Synthesis).

The hardware overhead and the operating frequency of the resulting hardware has been assessed, too.

#### **1.6** Organization of The Thesis

The rest of the thesis is organized into nine chapters. We start by looking at related works in Chapter 2. Then, in Chapter 3, we propose a solution to address the problem stated. Our approach towards the solution and the proposed system architecture are outlined there. The design of all architectural elements based on our proposed solution is presented in Chapter 4 followed by implementation details in chapter 5. Experiments and test results are presented in Chapter 6 followed by synthesis results in Chapter 7. Analysis on hardware cost and operating frequency of our design is made there. The thesis ends with conclusions in Chapter 8 and direction to future work in Chapter 9.

# 2

A lot of work has been done with the aim of reducing system verification effort while building complex systems. In [10], worst-case resource allocation is enforced to each application during verification in order to account for maximal interference from others. If a given user-level performance goal is satisfied with the enforcement, then the system is considered to be able to perform equally well, or even better, during actual use with the enforcement removed. This approach can guarantee better performance, during deployment, only if the applications considered execute on the platform in a *per*formance monotonic manner i.e. if applications are known to perform better with more service. However, in many cases, earlier service availability or higher service amount than the guaranteed value does not necessarily result in better system performance [4]. For instance, timing anomalies are observed in multi-processor systems with out-of-order processing [11]. Cases have been demonstrated in which a system performs better with cache miss than with cache hit. Hence a system verified with enforcement is not guaranteed to meet requirements during deployment, when service may be available earlier and/or with higher amount. Thus system verification requires system level simulation which can take tremendous effort when many applications are integrated to the system.

Composability has been proposed in many works to reduce system verification cost. In the automotive industry, for instance, the traditional way to achieve composability is by not sharing resources between applications. With this approach, systems are designed with *federated architectures*, where every function is served by a dedicated *Electronic Control Unit (ECU)* [12]. As the units are not shared between applications, obviously, there is no interference and hence the resulting system is composable. The cost of systems without resource sharing, however, is prohibitively high for consumer electronics. To circumvent the cost problem, *integrated architectures* are in use in the consumer electronics domain, and even in the automotive industry [14]. To ensure composability in integrated architectures, where resources are shared among applications, the resulting interference has to be eliminated.

Despite difference in approach, the works in [9, 6, 2] propose composable system to reduce verification cost in an integrated system. The Time-Triggered Architecture in [9] proposes a two-phased design methodology to achieve composability. During architecture design phase, components are specified in value and temporal domain. Communication at the interfaces of the shared resource is statically scheduled. After validating the constraints, the resulting components are used to build a composable system. As the individual components are pre-validated, the resulting system incurs less verification effort. This approach requires global notion of time and is limited to applications that can be scheduled statically.

The CoMPSoC platform proposed in [6] employs local Time Division Multiplexing (TDM) to bring about composability in a multi-processor SoC. With TDM, every ap-

plication is guaranteed access to resources during allocated slots of time and hence is shielded from interference. With this approach, however, latency and bandwidth are coupled. As a result, applications with low bandwidth requirement cannot be guaranteed with low latency without overallocation of bandwidth. Many resources such as SDRAM are scarce and have to be shared efficiently.

The composable resource sharing presented in [2], which is implemented in this work, is based on latency-rate ( $\mathcal{LR}$ ) servers. By using different arbitrers in the class of ( $\mathcal{LR}$ ) servers, it makes it possible to provide greater service differentiation than in TDM [2]. For instance, an arbitrer in this class that decouples latency and bandwidth can be chosen to efficiently satisfy tight latency requirements. As this approach is the base for the work in this thesis, it will be discussed in more depth in Section 3.

#### 3.1 Approach

When requestors share a resource, interference arises between them due to two major reasons - Arbitration for service and effect on resource state.

- Arbitration: When multiple requestors seek service from the same resource, arbitration is required to sequentialize the requesters. The result of the arbitration depends on the set of requests waiting to be served and the scheduling policy. With static-priority scheduling, for instance, the lowest priority requestor is deprived of service as long as there are other requestors with higher priority.

- State of resource: Once a request has been admitted to the shared resource, the actual service that it gets may depend on the state of the resource at the moment. We can consider a case with a Synchronous Dynamic RAM (SDRAM) to demonstrate such a dependence. Depending on the request served previously, the SDRAM may have to go through read/write switch, write/read switch or no switching at all. It may even require to refresh before serving the request at hand. That means the waiting time for a request depends on the nature of requests served previously. As there is a possibility for the previous request to be from another requestor, this situation entails interference between requestors.

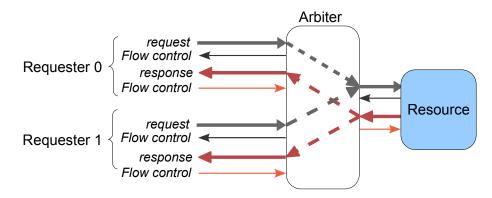

The effect of interference is reflected on the timing of *responses* and *flow-control information* sent to each requestor. Figure 3.1 illustrates these paths of interference for two requestors sharing a resource. First of all, the time at which a response becomes ready

Figure 3.1: Paths of Interference During Resource Sharing

depends on the time when the corresponding request is admitted to the resource. Then, it matters how fast the request is processed. The time of admission is determined by the scheduling decision, which is made considering requests from other requestors, as well. As a result, access to the resource is affected by the behavior of others. The state of the resource, which, among others, is affected by the nature of requests served previously, determines the time at which responses are made available. The other path of interference is through the flow-control mechanism. As shown in Figure 1.1, flow-control signals represent critical information about acceptance of requests and availability of resources. Requestors change their behavior in accordance with flow-control information about state of the system.

In summary, resource sharing creates implicit dependence between requestors and the resulting interference is reflected on the timing of responses and flow-control signals. If resource sharing is to be composable, the amount of interference that each requestor faces should not be affected by the behavior of other requestors.

We propose a resource sharing front-end based on the approach in [2] to eliminate fluctuation in the timing of the two events - release of responses and generation of flowcontrol information. Regardless of the actual time when responses are made available, they are always delayed and released at a later time that emulates maximum interference from other requestors, i.e., whether other applications are present or not and regardless of their actual behavior, our solution always emulates their worst-case interference. Similarly, flow-control signals are sent at a time that reflects maximum interference.

Figure 3.2: Timing of Events in the Resource Sharing Front-end

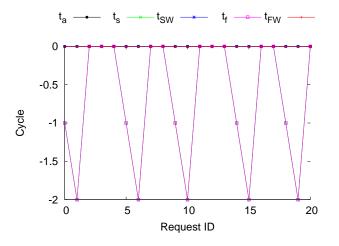

Figure 3.2 shows arrival time( $t_a$ ), actual scheduling time( $t_s$ ), worst-case scheduling time( $t_{SW}$ ), actual finishing time( $t_f$ ) and worst-case finishing time( $t_{FW}$ ) for a request. The worst-case values ( $t_{SW}$  and  $t_{FW}$ ) are computed considering the worst-case interference from all other requestors. From the figure, it can be seen that the request is scheduled before the worst-case scheduling time ( $t_{SW}$ ) and the responses are made available at  $t_f$ , which is earlier than the worst-case finishing time ( $t_{FW}$ ). However, in order to absorb any fluctuation caused by change in behavior of other requestors, generation of flow-control signals and release of responses is delayed until the worst-case scheduling time( $t_{SW}$ ) and the worst-case finishing time( $t_{FW}$ ), respectively. The interval between ( $t_s$ ) and ( $t_{SW}$ ) represents delay in generation of flow-control information introduced by the resource sharing front-end to absorb fluctuation caused by changing behavior of other requestors. Similarly, the interval between ( $t_f$ ) and ( $t_{FW}$ ) represents the delay in releasing responses that is introduced by the front-end.

Since the generation of flow-control information and release of responses is always delayed until a predefined time, each requestor obtains service that does not fluctuate with the actual behavior of other requestors. This makes the system composable on the level of requestors, which is sufficient to be composable on the level of applications [2]. With this approach, requestors are prohibited from using any slack (unused capacity) that results from change in behavior of other requestors. It seems like waste not to utilize slack, but being able to shield applications from interference while providing a guaranteed service (both in time and value domains) pays off by reducing system verification cost.

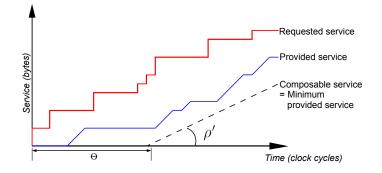

#### Predictable Service

Our approach to bring about composability requires the resource to be predictable. A resource is said to be predictable when the service that it provides can be bounded by a known finite value. Arbiters in the class of latency rate ( $\mathcal{LR}$ ) servers [17] are used to give guarantees on the service provided to each requestor.

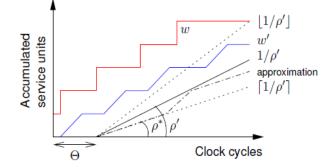

With the  $\mathcal{LR}$  model, service provided to each requestor is expressed in terms of two values - service latency and service rate. Service latency refers to the amount of time that a request has to wait in front of the resource before it is scheduled for service. Even though the actual time of scheduling for a request fluctuates depending on the availability of requests from other requestors, the state of the resource and the scheduling policy,  $\mathcal{LR}$ servers provide an upper bound on this waiting time, which is Maximum Service Latency ( $\Theta$ ). The service rate, on the other hand, stands for the rate, such as the throughput of a memory, at which a request is served after admission to the resource. Once more, the actual service rate provided to a requestor can fluctuate depending on the momentary state of the resource. However, with  $\mathcal{LR}$  servers, the amount is lower bounded with the Allocated Service Rate ( $\rho'$ ) which is the minimum service rate that is always reserved for a requestor [17].

The service curve in Figure 3.3 shows requested service along with provided service and composable service. As can be seen from the curves, requests are served at an earlier time that the worst-case scheduling time and at a rate higher than the allocated service rate. But the composable service, which is represented by the bounds ( $\Theta$ ) and ( $\rho'$ ), is what every requestor obtains in our approach.

Figure 3.3: Service Curve with latency-rate  $(\mathcal{LR})$  model

As mentioned above, predictability of the resource is a pre-requisite, in our approach,

to achieve composability. Given a predictable resource, there are additional requirements in order to ensure service guarantees. Either requests should have a known maximum size or preemption should be allowed after a certain time. Restricting the size of requests limits robustness of the solution. Such a restriction has implication on the domain of applications that can be supported. The later approach, on the other hand, either limits the solution to preemptive schedulers such as TDM or complicates the arbiter. Our solution employs a third way that allows usage of any arbiter in the class of  $\mathcal{LR}$  servers while maintaining robustness [2]. Requests can be of varying size but they are split into smaller pieces before they are scheduled.

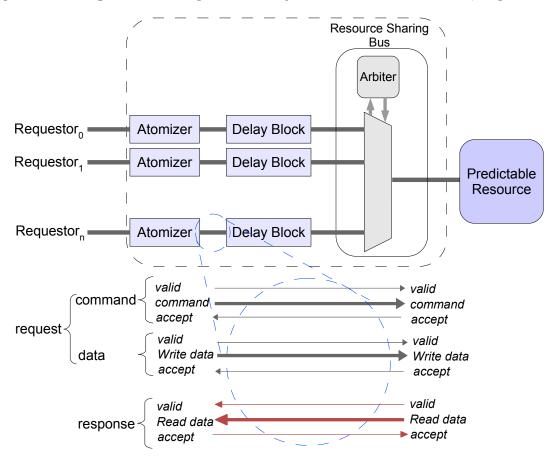

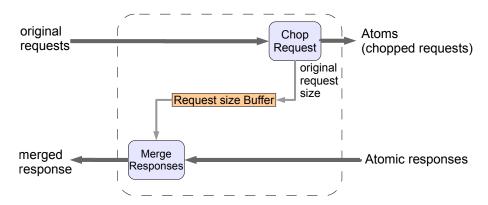

#### 3.2 Architecture

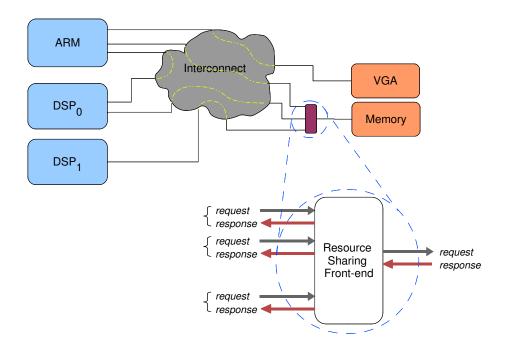

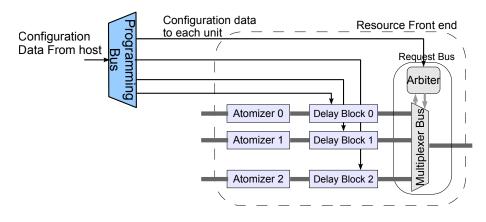

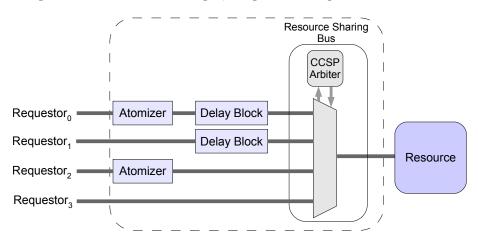

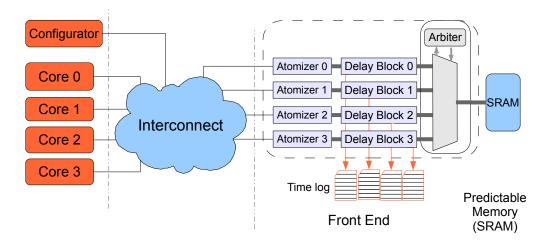

The front-end in our design, which is to be placed in front of the shared resource, is presented in Figure 3.4. It comprises four major functional blocks - *Arbiter*, *Request Bus*,

Figure 3.4: The Proposed Resource Sharing Front-end.

Delay Block and Atomizer. The link between blocks is composed of request, response and flow-control components. One of the links is shown in detail to make the request and response components visible. Requests contain command component and data to be written and responses contain the data read. In each direction a pair of *valid* and *accept* signals is used for flow-control.

As mentioned in Section 3.1, composability is achieved, in our solution, by delaying responses and flow-control signals to emulate worst-case interference at all times. Therefore, a hardware block, called *Delay Block* is dedicated to each requestor for the purpose. Another important unit of the front-end is the Atomizer. It is responsible for chopping requests into fixed size so that a variety of arbiters in the class of  $\mathcal{LR}$  servers can be used without imposing restriction on the size of request.

In the following chapters, the design (Chapter 4) and implementation (Chapter 5) of the entire frontend are presented.

In this chapter, the design of the entire front-end is presented. The design of the Atomizer is presented in Section 4.1 and that of the Delay Block in Section 4.2. The design of the arbiter and the Resource Sharing Bus, which contains the arbiter, is presented in Sections 4.3 and 4.4, respectively. Finally, the configuration mechanism for the front-end is presented in Section 4.5.

# 4.1 Atomizer

The function of the Atomizer is to homogenize requests before they enter the rest of the front-end. It chops requests into smaller pieces called *atoms*. The Atomizer has the size of atoms as a generic parameter to be chosen based on the resource. It is determined by the access granularity of the shared resource. For instance, with a 32-bit static RAM (SRAM), the size of an atom is chosen to be a word (4 bytes).

Chopping requests brings additional benefits to the design. Since all requests are made to have similar size as they leave the atomizer, subsequent units of the front-end (*Delay Block, Resource Sharing Bus* and *Arbiter*) can be simpler and more efficient. The major operations in the Atomizer are discussed in Section 4.1.1, and then the architecture is presented in Section 4.1.2.

# 4.1.1 Functions of the Atomizer

### **Chopping Requests:**

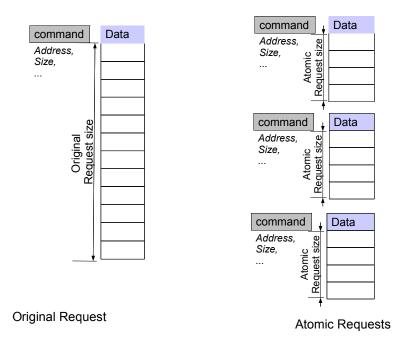

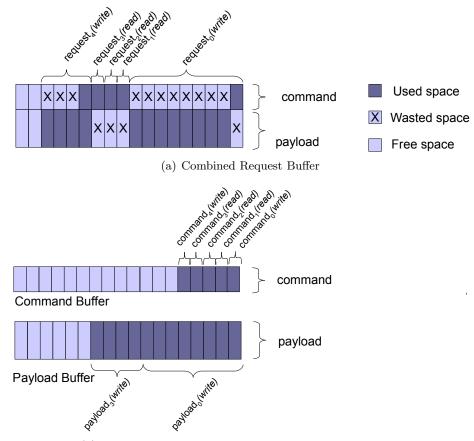

This process is responsible for chopping requests and feeding them to the Delay Block. Whenever the Atomizer receives a valid request and the Delay Block is ready to accept requests, this process starts chopping incoming requests. The chopped requests are, then, sent to the Delay Block one after the other. Requests contain command component and data to be written in case of a write request. The command component holds crucial information about size and address of the request. Hence, chopping a request involves attaching new request size and appropriate start address to the command component of each atom. The first atom has its start address the same as that of the original request. The start address of subsequent atoms is, then, offset from that of their predecessor by an amount proportional to the *Chopped Request Size*. In case of a write request, a portion of the payload data is sent with each chopped request. Figure 4.1 illustrates a request as it enters the Atomizer and the corresponding atoms produced after chopping.

If the request being chopped is expected to produce response, the size is recorded in *Request Size Buffer* to be used later in the process of merging responses. For instance, a read request is turned into a series of atomic read requests and the atomizer expects

Figure 4.1: Requests Chopped by the Atomizer

responses corresponding to each atom to arrive one after the other. Hence, the request size recorded here is required to count responses and identify the ones that belong to each request.

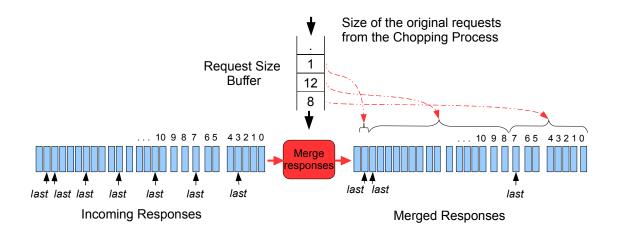

### Merging Response:

Since requests delivered to the resource are chopped, the resulting responses are also chopped alike. The requestors, however, expect responses in accordance with the original requests sent. Hence, responses are merged before leaving the front-end. This process of the Atomizer is responsible for merging responses so that they match the size of the original request. The original request sizes recorded in *Request Size Buffer* are used to count and merge responses that belong to the same request. Merging read responses, for instance, is equivalent to removing markers (indicators of the last response) from the individual pieces and generating one for the whole group of responses that belong to the same request. Figure 4.2 demonstrates an example in which responses of size 4 are merged in to responses of size 8, 12, 1, ..., according do request sizes recorded by the chopping process.

Figure 4.2: Merging of Responses in the Atomizer

# 4.1.2 Architecture

As shown in Figure 4.3, the Atomizer comprises two major processes - one that chops requests and another that merges responses. FIFOs are used for buffering requests to be chopped.

Figure 4.3: Architecture of the Atomizer

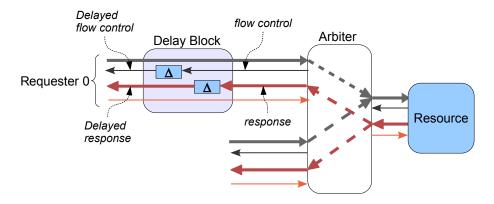

# 4.2 Delay Block

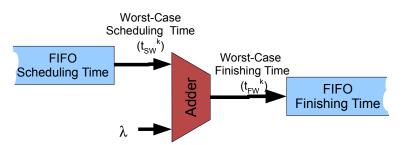

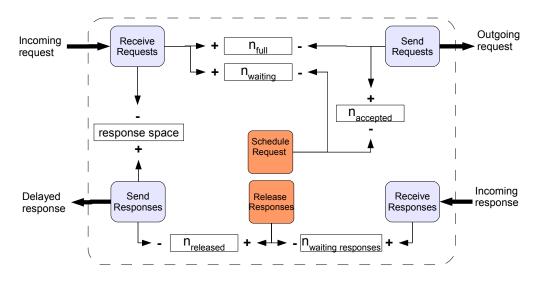

The Delay Block is the core unit of our approach to bring about composability. It absorbs fluctuations in the service provided to each requestor (*latency* and *bandwidth*). As pointed out in Section 3.1, interference between requestors is reflected on the timing of the following two events:

- 1. Time at which flow-control signals are sent when requests are accepted by the resource.

- 2. Time, after acceptance of a request, at which the corresponding responses are sent back to the requestor.

The time at which a request is accepted by the resource fluctuates depending on activity of other requestors and the state of the resource. This determines generation of flowcontrol signals. The time when responses become available depends not only on the time of scheduling but also on the actual service rate offered by the resource.

To hide the fluctuation in timing of the two events, the Delay Block always delays responses until the worst-case finishing time of requests, which reflects worst-case interference from other requestors. Similarly, flow-control information about acceptance of requests is generated based on the worst-case scheduling time. Figure 4.4 illustrates the delay processes along the response and flow-control paths. Computation of time stamps

Figure 4.4: Delay Processes in the Response and flow-control Paths.

that are used in the timing of these events is presented in detail in Section 4.2.2.

In summary, the Delay Block ensures that the scheduling time of a request and release time of the corresponding response are not affected by interference from other requestors, which is required in composable resource sharing.

#### 4.2.1 Parameters

Before describing the operation of the Delay Block, it is important to define two crucial parameters used in the timing of events - *Service Latency* ( $\Theta$ ) and *Completion Latency* ( $\lambda$ ). The value of these parameters is determined by the service guarantees provided by the  $\mathcal{LR}$  servers.

- 1. Service Latency ( $\Theta$ ): This represents the worst-case amount of time that a request waits in front of the resource before it is scheduled for service [2]. The bound depends on the priority that the source requestor has at the shared resource.

- 2. Completion Latency ( $\lambda$ ): This the worst-case amount of time that the resource needs to serve a unit-sized request. The value depends on the service rate allocated to each requestor, viz.  $\lambda = 1/\rho'$  [2].

# 4.2.2 Timing of Events

In this section, the timing of some interesting events in the front-end is discussed. The time line in Figure 4.5 illustrates the most outstanding points in time as a request passes through the front-end to get service from a predictable resource.

Figure 4.5: Important Events in serving a request

- Arrival Time  $(t_a^k)$ : is the time when the  $k^{th}$  request has, fully, arrived in the Delay Block and can be scheduled. This requires two conditions to be fulfilled.

- The request, along with the associated payload data, if any, should be buffered in the Delay Block.

- The Delay Block should have enough space for responses, if any, corresponding to the request at hand.

When these conditions are fulfilled, the time stamp is recorded as *Arrival Time* for the request at hand.

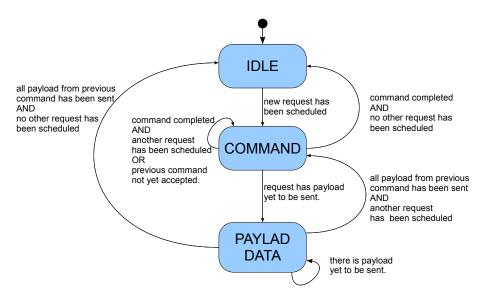

- Actual Scheduling Time  $(t_s^k)$ : Once a request has fully arrived in front of the resource, the time when it is admitted depends on the actual state of the resource and , possibly, arbitration among other contending requests. This time stamp represents the actual time when a request is accepted by the resource for service.

- Worst-case Scheduling Time  $(t_{SW}^k)$ : This refers to the worst-case time when the  $k^{th}$  request is accepted by the resource. The actual scheduling time depends on state of the resource and availability of other requests. This time stamp, however, is computed based on  $\Theta$  and the arrival time. To bring about composability, this worst-case time is recorded as scheduling time for requests and is used for timing

of flow-control information. The value of this time stamp is computed according to Equation (4.1) in Section 4.2.3. Note that it depends on the worst-case, and not actual, behavior of other requestors.

- Actual Finishing Time  $(t_f^k)$ : This is the time at which the resource finishes serving the  $k^{th}$  request and returns the corresponding responses, if any. The finishing time depends on actual scheduling time of a request and the actual service rate. Hence, the actual behavior of other requestors and the state of the resource affects its value.

- Worst-case Finishing Time  $(t_{FW}^k)$ : This time stamp represents worst-case finishing time for a request. Actual finishing time of a request depends on the actual time when it has been admitted to the resource and the actual rate at which it is served. To absorb fluctuations in actual values, this finishing time is computed based on the worst-case scheduling time and the allocated service rate. Despite the actual finishing time of a request, responses are, always, released at this worst-case finishing time. Hence, this time stamp can also be referred to as *Response Release Time*. The time stamp is computed according to Equation (4.2) in Section 4.2.3.

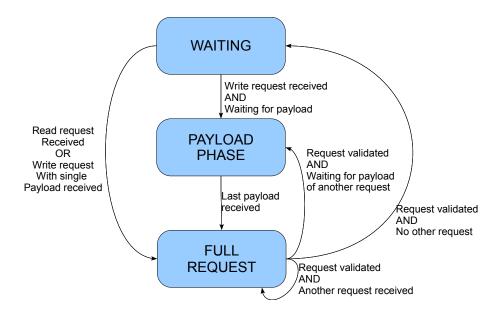

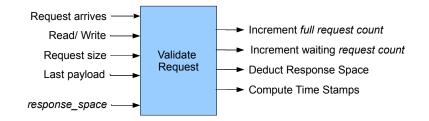

# 4.2.3 Computation of Time Stamps

The arrival of a request is validated when it has fully arrived in the Delay Block and space has been reserved in the response buffer for the corresponding responses, if any. This is the time that is taken as arrival time  $(t_a)$  for the request. (The reason behind reserving space for responses upon the arrival of requests is explained in Section 3.2.) The worst-case scheduling time  $(t_{SW})$  and worst-case finishing time  $(t_{FW})$  are, then, computed based on this arrival time. The worst-case scheduling time for a request is either *Service Latency* ( $\Theta$ ) cycles after its arrival time or at the worst-case finishing time of its predecessor, whichever is later [2].

$$t_{SW}^k = MAX(t_a^k + \Theta, t_{FW}^{(k-1)})$$

$$\tag{4.1}$$

The second term in the MAX equation (Equation (4.1)) is the result of self-interference because the scheduling time, in this case, is determined by the worst-case finishing time of a previous request from the same requestor.

The worst-case finishing time for responses is always computed as  $\lambda$  cycles after the worst-case scheduling time of the corresponding request [2].

$$t_{FW}^k = t_{SW}^k + \lambda \tag{4.2}$$

## 4.2.4 Flow-Control

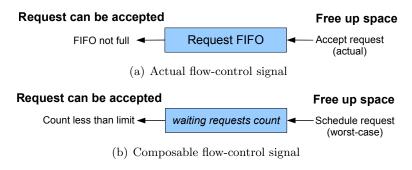

In addition to its effect on the time when responses become available, interference between requestors leads to fluctuation in the timing of flow-control signals. The flowcontrol signals refer to acceptance of requests and responses into the Delay Block. A new request can be admitted into the Delay Block if there is space in the *request buffer*. Space is freed up in the *request buffer* when a request is accepted by the resource. Therefore, the flow-control signal, which tells availability of space in the *request buffer* depends on the actual scheduling process and hence on other requestors. To eliminate such interference, flow-control signals, in our approach, are generated based on worst-case scheduling. Figure 4.6 compares generation of the actual flow-control signal and that of the composable flow-control signal.

Figure 4.6: Generation of flow-control signal (a),(b)

The front-end is also responsible for preventing a misbehaving requestor from stalling the resource, so that it does not affect the service provided to the remaining requestors. The resource is stalled when a requestor sends many requests to the resource and then does not accept the responses. To prevent this, the front-end performs validation of requests before presenting them to the resource. A request is validated when it has fully arrived in the Delay Block, including associated payload, and if there is guarantee that responses will be accepted when they are made available by the resource. The guarantee is made by reserving space, in the response buffer, for potential response, before sending the request to the resource. If there is no space in the response buffer, the request is not validated and forwarded to the resource until a previous response leaves the Delay Block and space is freed up. Since each request is validated after reserving space for its responses, it is always guaranteed that responses are always accepted to the Delay Block as soon as they are made available by the resource.

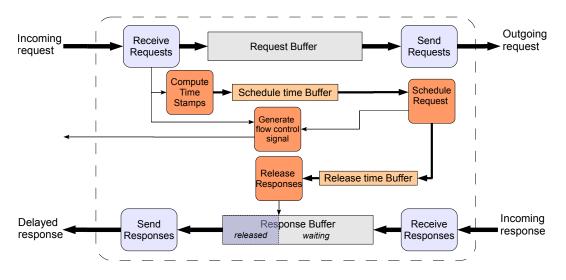

## 4.2.5 Architecture

The architecture in Figure 4.7 shows major processes and buffers that comprise the Delay Block. The Delay Block has four concurrent processes that are responsible for *receiving requests, sending requests, receiving responses* and *sending responses* to and from connected blocks. It has additional processes that manage timing of events and record relevant time stamps. One of the processes, *Compute Time Stamps*, is responsible for the computation of worst-case scheduling time and worst-case finishing time of requests based on the service bounds. Another process generates flow-control information based on worst-case scheduling of requests. The *Schedule Request* process, shown in Figure 4.7, takes care of the scheduling event that takes place at the worst-case scheduling time of requests. Similarly, the *Release Response* process handles releasing of responses at the worst-case finishing time.

The Delay Block contains four buffers. The *Request Buffer*, as the name indicates, holds requests in the Delay Block until they are scheduled and sent to the resource.

Figure 4.7: Architecture of the Delay Block

The *Response Buffer*, on the other hand, holds responses until their release time is due and they leave the Delay Block. The remaining two buffers - *Scheduling Time Buffer* and *Release Time Buffer* hold time stamps to be used for the timing of Scheduling and Releasing events, respectively. Each of the units and their implementation are detailed in Section 5.2.2.

# 4.3 Arbiter

In the proposed resource sharing front-end, any arbiter in the class of  $\mathcal{LR}$  servers can be used. One such arbiter is the Credit-Controlled Static-Priority Arbiter (CCSP) [1]. One difference is that the arbiter is now the resource sharing front-end and hence can be used with any predictable resource. A few changes have also been made in the implementation. This will be explained while discuss the implementation in Section 5.2.3. The design of the CCSP arbiter has been revised with an approach different from the one used in a previous implementation [18]. , here, so that it fits well in the resource sharing bus. The CCSP arbiter combines rate regulation and priorities to decouple guarantee on latency and rate. This is required, because some applications are latency sensitive and others are latency tolerant. By decoupling the two requirements, the CCSP arbiter allows providing low-latency service to low-bandwidth requests without overallocation. The parameters, mechanism and architecture of CCSP are presented in Sections 4.3.1, 4.3.2 and 4.3.3, respectively.

# 4.3.1 CCSP Parameters

The arbitration process in CCSP relies on three crucial parameters. These are the Allocated Service Rate  $(\rho')$  required for rate regulation, Priority for the static-priority scheduling and Allocated Burstiness  $(\sigma')$  to control burst of service.

- **Priority** (*p*): of a requestor, as the name implies, indicates the priority given to a requestor when it is in contention with other requestors for a resource. Every requestor is given a unique priority value.

- Allocated Service Rate ( $\rho'$ ): represents the amount of service that a requestor is entitled for every service cycle. Every service cycle, its budget is upgraded by this amount. The allocated service rate is expressed as fraction of the resource capacity allocated to a requestor. Hence, it always has value between 0 and 1.

- Allocated Burstiness ( $\sigma'$ ): represents the maximum burst of service that each requestor can get, i.e. the maximum number of times that a requestor can be served in succession without having to upgrade its budget. The initial budget that each requestor obtains at start up is based on this parameter.

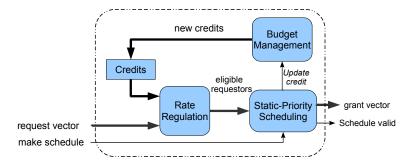

# 4.3.2 Mechanism

CCSP maintains a budget per requestor in order to regulate service provided to each one. This protects low priority requestors from starvation. Because of the regulation, requestors are always guaranteed that they can get their allocated service amount. Every service cycle, all requestors are entitled for service that amounts to their allocated rate. This is reflected by an upgrade to their budget value. Each requestor, then, pays from its budget for every service it gets i.e. whenever it is scheduled. Requestors that do not have enough budget have to wait and accumulate enough budget to be eligible for service. After identifying requestors that have enough budget to be considered for service, one of them is selected based on priority. The scheduling is based on static priority and the requestor that has the highest priority is scheduled. After every scheduling event, the budget of all requestors is updated in accordance with the scheduling result.

# 4.3.3 Architecture

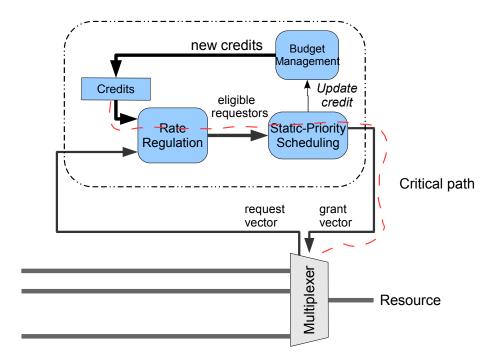

The architecture in Figure 4.8 shows the three major functional units of the CCSP arbiter - *Rate Regulation, static-priority scheduling* and *Budget Management*.

Figure 4.8: Architecture of CCSP Arbiter

## 4.3.3.1 Rate Regulation

The CCSP arbiter regulates service by watching the budget status of each requestor. This stage of the arbiter identifies requestors that are eligible for service based on their budget status and passes them to the next arbitration stage. To be eligible, requestors are required to have budget amount that exceeds a certain threshold. The threshold is also determined based on the service rate allocated to each requestor. The pseudocode of Algorithm 4.1 shows the simple process of identifying eligible requestors.

```

Algorithm 4.1 Eligibility Check in the CCSP Arbiter

GIVEN: R requestors with corresponding budget amount

OUTPUT: Eligibility Mask of requestors.

for each requestor r do

if budget[r] > Budget Threshold[r] then

Eligibility (r) \leftarrow TRUE;

else

Eligibility (r) \leftarrow FALSE;

end if

```

## 4.3.3.2 Static-Priority Scheduling

This stage of the CCSP carries out static-priority scheduling on those requestors that have been identified by the previous state as *eligible*. The result of the scheduling, schedule mask is sent to request multiplexer so that the scheduled request is handed over to the resource. Static-priority scheduling is a simple process of selecting the highest priority requestor.

| Algorithm 4.2 Static-Priority Scheduling in the CCSP Arbiter                         |

|--------------------------------------------------------------------------------------|

| GIVEN: R requestors with corresponding priority values PRIORITY.                     |

| <b>OUTPUT:</b> Scheduled Mask which indicates the requestor that has been scheduled. |

| $VARIABLE \ scheduled \leftarrow FALSE \ ;$                                          |

| for each requestor $\mathbf{r}$ in decreasing order of priority $\mathbf{do}$        |

| <b>if</b> Eligibility(r) = '1' and scheduled = FALSE <b>then</b>                     |

| schedule mask(r) $\leftarrow$ '1'; scheduled $\leftarrow TRUE$ ;                     |

| else                                                                                 |

| $schedulemask(r) \leftarrow' 0';$                                                    |

| end if                                                                               |

| end for                                                                              |

## 4.3.3.3 Budget Management

The budget for each requestor is updated according to the result of the scheduling. After each scheduling event, which takes place every service cycle, the budget manager upgrades the budget of each requestor by an amount equal to the allocated service rate. And for the requestor that is scheduled, if any, budget value is deducted by 1 because it has to pay for the service it has obtained. There is, however, a limit on the maximum budget that can be accumulated by requestors when they do not have valid request and that limit is equal to the *initial budget*. This is enforced in order to limit the burstiness of requestors to their allocated amount ( $\sigma'$ ).

```

Algorithm 4.3 Budget Management in the CCSP ArbiterGIVEN: Current Budget of Each Requestor, Result of the Scheduling Decision.OUTPUT: New Budget for Each Requestor.Every Service Cyclefor each requestor r doBudget[r] \leftarrow Budget[r] + Allocated Rate [r];if schedule mask (r) = TRUE thenBudget[r] \leftarrow Budget[r] - 1;elseif requestor r has no request pending then//reset budget to initial amountBudget[r] \leftarrow Initial Budget[r];end ifend ifend for

```

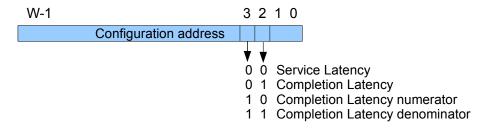

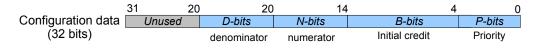

# 4.4 Resource Sharing Bus